Буферний каскад

Номер патенту: 59353

Опубліковано: 10.05.2011

Автори: Богомолов Сергій Віталійович, Азаров Олексій Дмитрович, Росощук Анастасія Володимирівна

Формула / Реферат

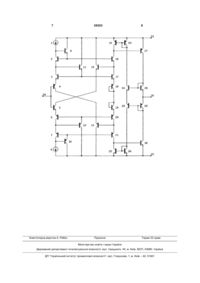

Буферний каскад, який містить вісімнадцять транзисторів, перше та друге джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами третього і четвертого транзисторів, колектори третього і четвертого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, емітери третього і четвертого транзисторів з'єднано з емітерами другого і п'ятого транзисторів відповідно, бази другого і п'ятого транзисторів з'єднано з базами чотирнадцятого і сімнадцятого транзисторів відповідно, а також з емітерами дев'ятого і десятого транзисторів відповідно, колектори другого і п'ятого транзисторів з'єднано з базами дев'ятого і десятого транзисторів відповідно, а також з емітерами першого і шостого транзисторів відповідно, бази першого і шостого транзисторів з'єднано з базами тринадцятого і вісімнадцятого транзисторів відповідно, а також з емітерами сьомого і восьмого транзисторів відповідно, колектори першого і шостого транзисторів з'єднано з базами сьомого і восьмого транзисторів відповідно, а також з першими виводами першого і другого джерел струмів відповідно, другий вивід першого джерела струму та колектори сьомого, дев'ятого, одинадцятого транзисторів з'єднано з шиною додатного живлення, другий вивід другого джерела струму та колектори восьмого, десятого, дванадцятого транзисторів з'єднано з шиною від'ємного живлення, емітери тринадцятого і вісімнадцятого транзисторів з'єднано з базами одинадцятого і дванадцятого транзисторів відповідно, а також з колекторами чотирнадцятого і шістнадцятого транзисторів відповідно, емітери чотирнадцятого і сімнадцятого транзисторів з'єднано з емітерами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази та колектори п'ятнадцятого і шістнадцятого транзисторів об'єднано, який відрізняється тим, що у нього введено дев'ятнадцятий, двадцятий, двадцять перший, двадцять другий, двадцять третій, двадцять четвертий, двадцять п'ятий, двадцять шостий, двадцять сьомий, двадцять восьмий транзистори, причому емітери дев'ятнадцятого, двадцять першого, двадцять п'ятого та двадцятого, двадцять четвертого, двадцять восьмого з'єднано з шинами додатного та від'ємного живлення відповідно, колектори дев'ятнадцятого і двадцятого транзисторів з'єднано з колекторами тринадцятого і вісімнадцятого транзисторів відповідно, а також з базами двадцять п'ятого і двадцять восьмого транзисторів відповідно, бази дев'ятнадцятого і двадцятого транзисторів з'єднано з базами та колекторами двадцять першого та двадцять четвертого транзисторів відповідно, а також з колекторами двадцять другого та двадцять третього транзисторів відповідно, емітери двадцять другого і двадцять третього транзисторів об'єднано, бази двадцять другого і двадцять третього транзисторів з'єднано з базами та колекторами двадцять шостого і двадцять сьомого транзисторів відповідно, а також з колекторами двадцять п'ятого і двадцять восьмого транзисторів відповідно, транзистори двадцять шостого і двадцять сьомого транзисторів об'єднано і з'єднано з вихідною шиною.

Текст

Буферний каскад, який містить вісімнадцять транзисторів, перше та друге джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами третього і четвертого транзисторів, колектори третього і четвертого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, емітери третього і четвертого транзисторів з'єднано з емітерами другого і п'ятого транзисторів відповідно, бази другого і п'ятого транзисторів з'єднано з базами чотирнадцятого і сімнадцятого транзисторів відповідно, а також з емітерами дев'ятого і десятого транзисторів відповідно, колектори другого і п'ятого транзисторів з'єднано з базами дев'ятого і десятого транзисторів відповідно, а також з емітерами першого і шостого транзисторів відповідно, бази першого і шостого транзисторів з'єднано з базами тринадцятого і вісімнадцятого транзисторів відповідно, а також з емітерами сьомого і восьмого транзисторів відповідно, колектори першого і шостого транзисторів з'єднано з базами сьомого і восьмого транзисторів відповідно, а також з першими виводами першого і другого джерел струмів відповідно, другий вивід першого джерела струму та колектори сьомого, дев'ятого, одинадцятого транзисторів з'єднано з шиною додатного живлення, другий вивід другого джерела струму та колектори восьмого, десятого, U 2 UA 1 3 гого транзисторів відповідно, база та колектор першого транзистора об'єднані і приєднані до шини додатного живлення через перше джерело струму, а також до бази другого транзистора, база сьомого транзистора з'єднана з шиною від'ємного живлення через друге джерело струму, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно. Крім того містить дев'ятий, десятий, одинадцятий, дванадцятий транзистори, причому база кожного з них з'єднана з його колектором, емітер восьмого транзистора з'єднано з базою сьомого транзистора та першим виводом другого джерела струму, емітери дев'ятого та десятого транзисторів з'єднано з емітерами четвертого та п'ятого транзисторів відповідно, бази та колектори дев'ятого та десятого транзисторів з'єднано з базами третього та шостого транзисторів відповідно, а також базу та колектор дев'ятого транзистора з'єднано з емітером першого транзистора, базу та колектор десятого транзистора з'єднано з базою та колектором восьмого транзистора, емітери третього та шостого транзисторів з'єднано з емітерами одинадцятого та дванадцятого транзисторів відповідно, бази і колектори одинадцятого та дванадцятого транзисторів з'єднано з вихідною шиною. Основним недоліком аналогу є низька точність роботи пристрою, яка обумовлена великим рівнем вхідного струму зміщення. За прототип обрано буферний пристрій (Патент України №24882, H03F 3/26, 2007р.), який містить вісімнадцять транзисторів, перше та друге джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами третього і четвертого транзисторів, колектори третього і четвертого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, емітери третього і четвертого транзисторів з'єднано з емітерами другого і п'ятого транзисторів відповідно, бази другого і п'ятого транзисторів з'єднано з базами чотирнадцятого і сімнадцятого транзисторів відповідно, а також з емітерами дев'ятого і десятого транзисторів відповідно, колектори другого і п'ятого транзисторів з'єднано з базами дев'ятого і десятого транзисторів відповідно, а також з емітерами першого і шостого транзисторів відповідно, бази першого і шостого транзисторів з'єднано з базами тринадцятого і вісімнадцятого транзисторів відповідно, а також з емітерами сьомого і восьмого транзисторів відповідно, колектори першого і шостого транзисторів з'єднано з базами сьомого і восьмого транзисторів відповідно, а також з першими виводами першого і другого джерел струмів відповідно, другий вивід першого джерела струму та колектори сьомого, дев'ятого, одинадцятого, тринадцятого транзисторів з'єднано з шиною додатного живлення, другий вивід другого джерела струму та колектори восьмого, десятого, дванадцятого, вісімнадцятого транзисторів з'єднано з шиною від'ємного живлення, емітери тринадцятого і вісімнадцятого транзисторів з'єднано з базами одинадцятого і дванадцятого транзисторів відповідно, а також з колекторами чотирнадцятого і шістнадцятого транзисторів відповідно, емітери чотирнадцятого і 59353 4 сімнадцятого транзисторів з'єднано з емітерами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази та колектори п'ятнадцятого і шістнадцятого транзисторів з'єднано з вихідною шиною. Недоліком прототипу є низька точність, що обмежує галузь використання пристрою. В основу корисної моделі поставлено задачу створення буферного каскаду, в якому за рахунок введення нових елементів та зв'язків між ними підвищується точність, це розширює галузь використання корисної моделі у різноманітних цифрових вимірювальних пристроях та аналоговоцифрових перетворювачах. Поставлена задача досягається тим, що в буферний каскад, який містить вісімнадцять транзисторів, перше та друге джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами третього і четвертого транзисторів, колектори третього і четвертого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, емітери третього і четвертого транзисторів з'єднано з емітерами другого і п'ятого транзисторів відповідно, бази другого і п'ятого транзисторів з'єднано з базами чотирнадцятого і сімнадцятого транзисторів відповідно, а також з емітерами дев'ятого і десятого транзисторів відповідно, колектори другого і п'ятого транзисторів з'єднано з базами дев'ятого і десятого транзисторів відповідно, а також з емітерами першого і шостого транзисторів відповідно, бази першого і шостого транзисторів з'єднано з базами тринадцятого і вісімнадцятого транзисторів відповідно, а також з емітерами сьомого і восьмого транзисторів відповідно, колектори першого і шостого транзисторів з'єднано з базами сьомого і восьмого транзисторів відповідно, а також з першими виводами першого і другого джерел струмів відповідно, другий вивід першого джерела струму та колектори сьомого, дев'ятого, одинадцятого транзисторів з'єднано з шиною додатного живлення, другий вивід другого джерела струму та колектори восьмого, десятого, дванадцятого транзисторів з'єднано з шиною від'ємного живлення, емітери тринадцятого і вісімнадцятого транзисторів з'єднано з базами одинадцятого і дванадцятого транзисторів відповідно, а також з колекторами чотирнадцятого і шістнадцятого транзисторів відповідно, емітери чотирнадцятого і сімнадцятого транзисторів з'єднано з емітерами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази та колектори п'ятнадцятого і шістнадцятого транзисторів об'єднано, введено дев'ятнадцятий, двадцятий, двадцять перший, двадцять другий, двадцять третій, двадцять четвертий, двадцять п'ятий, двадцять шостий, двадцять сьомий, двадцять восьмий транзистори, причому емітери дев'ятнадцятого, двадцять першого, двадцять п'ятого та двадцятого, двадцять четвертого, двадцять восьмого з'єднано з шинами додатного та від'ємного живлення відповідно, колектори дев'ятнадцятого і двадцятого транзисторів з'єднано з колекторами тринадцятого і вісімнадцятого транзисторів відповідно, а також з базами двадцять п'ятого і двадцять восьмого транзисторів відповідно, бази дев'ятнадцятого і двадцятого транзис 5 торів з'єднано з базами та колекторами двадцять першого та двадцять четвертого транзисторів відповідно, а також з колекторами двадцять другого та двадцять третього транзисторів відповідно, емітери двадцять другого і двадцять третього транзисторів об'єднано, бази двадцять другого і двадцять третього транзисторів з'єднано з базами та колекторами двадцять шостого і двадцять сьомого транзисторів відповідно, а також з колекторами двадцять п'ятого і двадцять восьмого транзисторів відповідно, транзистори двадцять шостого і двадцять сьомого транзисторів об'єднано і з'єднано з вихідною шиною. На кресленні представлено принципову схему буферного каскаду. Пристрій містить вхідну шину 34, яку з'єднано з базами третього 4 і четвертого 5 транзисторів, колектори третього 4 і четвертого 5 транзисторів з'єднано з емітерами одинадцятого 13 і дванадцятого 14 транзисторів відповідно, емітери третього 4 і четвертого 5 транзисторів з'єднано з емітерами другого 3 і п'ятого 6 транзисторів відповідно, бази другого 3 і п'ятого 6 транзисторів з'єднано з базами чотирнадцятого 17 і сімнадцятого 20 транзисторів відповідно, а також з емітерами дев'ятого 11 і десятого 12 транзисторів відповідно, колектори другого 3 і п'ятого 6 транзисторів з'єднано з базами дев'ятого 11 і десятого 12 транзисторів відповідно, а також з емітерами першого 2 і шостого 7 транзисторів відповідно, бази першого 2 і шостого 7 транзисторів з'єднано з базами тринадцятого 16 і вісімнадцятого 21 транзисторів відповідно, а також з емітерами сьомого 9 і восьмого 10 транзисторів відповідно, колектори першого 2 і шостого 7 транзисторів з'єднано з базами сьомого 9 і восьмого 10 транзисторів відповідно, а також з першими виводами першого 1 і другого 8 джерел струмів відповідно, другий вивід першого 1 джерела струму, колектори сьомого 9, дев'ятого 11, одинадцятого 13 та емітери дев'ятнадцятого 15, двадцять першого 23, двадцять п'ятого 27 транзисторів з'єднано з шиною додатного живлення 31, другий вивід другого 8 джерела струму, колектори восьмого 10, десятого 12, дванадцятого 14 та двадцятого 22, двадцять четвертого 26, двадцять восьмого 30 транзисторів з'єднано з шиною від'ємного живлення 33, емітери тринадцятого 16 і вісімнадцятого 21 транзисторів з'єднано з базами одинадцятого 13 і дванадцятого 14 транзисторів відповідно, а також з колекторами чотирнадцятого 14 і шістнадцятого 20 транзисторів відповідно, емітери чотирнадцятого 17 і сімнадцятого 20 транзисторів з'єднано з емітерами п'ятнадцятого 18 і шістнадцятого 19 транзисторів відповідно, бази та колектори п'ятнадцятого 18 і шістнадцятого 19 транзисторів об'єд 59353 6 нано, колектори дев'ятнадцятого 15 і двадцятого транзисторів з'єднано з колекторами тринадцятого 16 і вісімнадцятого 21 транзисторів відповідно, а також з базами двадцять п'ятого 27 і двадцять восьмого 30 транзисторів відповідно, бази дев'ятнадцятого 15 і двадцятого 22 транзисторів з'єднано з базами та колекторами двадцять першого 23 та двадцять четвертого 26 транзисторів відповідно, а також з колекторами двадцять другого 24 та двадцять третього 25 транзисторів відповідно, емітери двадцять другого 24 і двадцять третього 25 транзисторів об'єднано, бази двадцять другого 24 і двадцять третього 25 транзисторів з'єднано з базами та колекторами двадцять шостого 28 і двадцять сьомого 29 транзисторів відповідно, а також з колекторами двадцять п'ятого 27 і двадцять восьмого 30 транзисторів відповідно, транзистори двадцять шостого 28 і двадцять сьомого 29 транзисторів об'єднано і з'єднано з вихідною шиною 32. Буферний каскад працює таким чином: якщо напруга на вхідній шині 34 збільшується, то потенціали емітерів третього 4 і четвертого 5 транзисторів збільшуються, у свою чергу збільшуються потенціали баз другого 3, чотирнадцятого 17 та п'ятого 6, сімнадцятого 20 транзисторів відповідно, а також колекторів двадцять шостого 28 і двадцять сьомого 29 транзисторів відповідно, при цьому потенціал на вихідній шині 32 також збільшується. Якщо напруга на вхідній шині 34 зменшується, то потенціали емітерів третього 4 і четвертого 5 транзисторів зменшуються, у свою чергу зменшуються потенціали баз другого 3, чотирнадцятого 17 та п'ятого 6, сімнадцятого 20 транзисторів відповідно, а також колекторів двадцять шостого 28 і двадцять сьомого 29 транзисторів відповідно, при цьому потенціал на вихідній шині 32 також зменшується. Підвищення точності роботи схеми досягається за рахунок введення двонаправленого відбивача струму, який побудовано на двадцять другому 24, двадцять третьому 25, двадцять шостому 28, двадцять сьомому 29 транзисторах. Двонаправлений відбивач струму разом із компенсаторами струму, які побудовані на дев'ятнадцятому 15, двадцять першому 23 і двадцятому 22, двадцять четвертому 26 транзисторах відповідно, задають режим по постійному струму для проміжних підсилювальних каскадів, які побудовані на двадцять п'ятому 27 і двадцять восьмому 30 транзисторах відповідно. Шини додатного 31 і від'ємного 33 живлення задають відповідний рівень напруг для живлення схеми. 7 Комп’ютерна верстка А. Рябко 59353 8 Підписне Тираж 23 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюBuffer stage

Автори англійськоюAzarov Oleksii Dmytrovych, Rososchuk Anastasia Volodymyrivna, Bohomolov Serhii Vitaliiovych

Назва патенту російськоюБуферный каскад

Автори російськоюАзаров Алексей Дмитриевич, Росощук Анастасия Владимировна, Богомолов Сергей Витальевич

МПК / Мітки

МПК: H03K 5/22

Код посилання

<a href="https://ua.patents.su/4-59353-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Буферний каскад

Наступний патент: Застосування 1-(1-адамантил-1-алкоксі)-3-аміно-2-пропанолів, як засобів, які мають кардіопротекторну активність

Випадковий патент: Промислова система виробництва зневодненого харчового етилового спирту