Пристрій ldpc-декодування

Номер патенту: 98611

Опубліковано: 27.04.2015

Автори: Денисов Олексій Олегович, Крайник Ярослав Михайлович, Мусієнко Максим Павлович

Формула / Реферат

Пристрій LDPC-декодування, що складається з блока прийому вхідного повідомлення, блока обробки інформації в ході декодування, блоків пам'яті для збереження інформації про вхідне повідомлення та блока пам'яті результуючого повідомлення для декодування, блока пам'яті індексів значущих елементів у матриці парності, блока пам'яті результатів обчислень значень перевірки на кожній ітерації, блока пам'яті проміжних значень у ході виконання ітерації процесу декодування, блока пам'яті для запису результуючого декодованого повідомлення, а також блока видачі вихідного повідомлення, який відрізняється тим, що містить блок віднімачів, блок суматорів та блок виконання операцій виключного АБО.

Текст

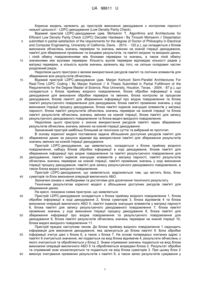

Реферат: UA 98611 U UA 98611 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до пристроїв виконання декодування з контролем парності низької щільності - LDPC-декодування (Low Density Parity Check). Відомий пристрій LDPC-декодування (див. Mohsenin T. Algorithms and Architectures for Efficient Low Density Parity Check (LDPC) Decoder Hardware / By Tinoosh Mohsenin // Dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering, University of California, Davis. - 2010. - 122 p.), що складається з блоків виконання обчислень значень перевірки та значень змінних на кожній ітерації декодування, пам'яті для збереження проміжних та кінцевих результатів, та пам'яті вхідних та вихідних даних, і ліній обміну повідомленнями між блоками перевірки та значень, а також ліній обміну значеннями між вузлами перевірки. Кількість вузлів перевірки відповідає кількості рядків у матриці перевірки, а кількість вузлів значень залежить від того, на скільки складових частин розділений рядок. Недоліком цього пристрою є велике використання ресурсів пам'яті та логічних елементів для збереження всіх результатів обчислень. Відомий пристрій LDPC-декодування (див. Marjan Karkooti Semi-Parallel Architectures For Real-Time LDPC Coding / By Marjan Karkooti // A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree Master of Science, Rice University, Houston, Texas. - 2004. - 87 p.), що складається з блока прийому вхідного повідомлення, блока обробки інформації в ході декодування для виконання обробки перевірок та змінних, блока контролю за процесом декодування, блоків пам'яті для збереження інформації про вхідне повідомлення та блока пам'яті результуючого повідомлення для декодування, блока пам'яті проміжних значень у ході виконання ітерації процесу декодування, блока пам'яті індексів значущих елементів у матриці парності, блока пам'яті результатів обчислень значень перевірки на кожній ітерації та блока пам'яті результатів обчислень значень змінних на кожній ітерації, блока пам'яті для запису результуючого декодованого повідомлення та блока видачі вихідного повідомлення. Недоліком цього пристрою є значне використання ресурсів пам'яті через збереження результатів обчислень значень змінних на кожній ітерації декодування. Зазначений пристрій найбільш близький за технічною суттю та вибраний як прототип. В основу корисної моделі поставлена задача збільшення доступних ресурсів пам'яті для збереження даних за рахунок відмови від використання пам'яті для збереження результатів значень змінних на кожній ітерації декодування. Пристрій LDPC-декодування, що заявляється, складається з блока прийому вхідного повідомлення, набору блоків обробки інформації в ході декодування, блоків пам'яті для збереження інформації про вхідне повідомлення та пам'яті результуючого повідомлення для декодування, пам'яті індексів значущих елементів у матриці парності, пам'яті результатів обчислень значень перевірки на кожній ітерації, пам'яті проміжних значень у ході виконання ітерації процесу декодування, пам'яті для запису результуючого декодованого повідомлення, а також блока видачі вихідного повідомлення. Пристрій LDPC-декодування, що заявляється, відрізняється тим, що містить блок, блок суматорів та блок виконання операцій виключного АБО. Зазначені ознаки є необхідними та достатніми для досягнення технічного результату. Технічним результатом корисної моделі є збільшення доступних ресурсів пам'яті для збереження даних. На кресл. показана схема пристрою, що заявляється. Пристрій LDPC-декодування складається з блока прийому вхідного повідомлення 1, блока обробки інформації в ході декодування 2, блока суматорів 3, блока віднімачів 4 та блока виконання операцій виключного АБО 5, пам'яті індексів значущих елементів у матриці парності 6, блока пам'яті для запису результуючого декодованого повідомлення 7, блока пам'яті проміжних значень у ході виконання ітерації процесу декодування 8, блока пам'яті для збереження інформації про вхідне повідомлення та результуючого повідомлення для декодування 9, блока пам'яті результатів обчислень значень перевірки на кожній ітерації 10, блока видачі вихідного повідомлення 11. Пристрій працює наступним чином. До блока прийому вхідного повідомлення 1 надходить інформація для виконання декодування, яка записується до блока пам'яті 9. Блок обробки інформації зчитує дані з блока 6, а також з блока 7. На основі попередньо зчитаних адрес з пам'яті 9 зчитуються значення, які подаються на вхід блока віднімачів 4, результати обчислень з якого зчитуються та обробляються у блоці 2. Знаки отриманих значень подаються на вхід блока виконання операцій виключного АБО 5 та обробляються всередині блока 2. Результат обробки та отриманий знак конкатенуються та подаються на вхід блока суматорів 3. При цьому блок 2 виконує зчитування проміжних результатів з пам'яті 8, а також запис результатів сумування у 1 UA 98611 U 5 10 15 20 25 блок 8. Після обробки всіх рядків з блока 6 виконується перезапис значень з пам'яті 8 у пам'ять 9. Після виконання перезапису виконується операція жорсткого декодування на основі знаку результатів у блоці 9 з записом у блок 10. Далі починається нова ітерація декодування або видається результат. Після завершення процесу декодування результат з блока 10 видається в блок 11. Таким чином, вказана організація пристрою дозволяє не зберігати значення результатів обчислень значень змінних в окремому блоці пам'яті, а виконувати обчислення згаданих значень за рахунок використання блока віднімачів 4 без зміни результату декодування вихідного повідомлення. У пристрої ж за прототипом значення змінних зберігаються у пам'яті, що призводить до збільшення використання даного ресурсу. Застосування додаткового блока віднімачів 4 дозволило виконувати обчислення значень змінних безпосередньо перед операціями, в яких необхідні ці значення, що не потребує великих додаткових апаратних ресурсів та у порівнянні з прототипом не потребує запису результатів значень змінних у пам'ять, що дає можливість значно скоротити використання ресурсів пам'яті. Приклад конкретного використання. Як приклад реалізовано декодер на базі відлагоджувальної плати ZedBoard з мікросхемою System-on-Chip Xilinx Zynq Z7020, блокова пам'ять якої використовувалась як блоки пам'яті декодеру, для матриці перевірки парності з низькою щільністю значущих елементів розмірністю 5000 рядків на 10000 стовпчиків з максимальною вагою рядка 9 та максимальною вагою стовпця 6. При реалізації пристрою LDPC-декодування відповідно до схеми прототипу необхідно організовувати 96=54 блоків пам'яті для збереження результатів перевірки та значень змінних. При реалізації пристрою, що заявляється, за рахунок використання блока віднімачів організовано лише 9 блоків пам'яті для збереження результатів обчислень значень перевірки на кожній ітерації. Це в 6 разів менше за кількість блоків пам'яті, що необхідна при реалізації за схемою прототипу. Таким чином, пристрій, що заявляється, дозволяє зменшити використання ресурсів пам'яті, а отже, збільшити доступні ресурси пам'яті для збереження даних. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 30 35 Пристрій LDPC-декодування, що складається з блока прийому вхідного повідомлення, блока обробки інформації в ході декодування, блоків пам'яті для збереження інформації про вхідне повідомлення та блока пам'яті результуючого повідомлення для декодування, блока пам'яті індексів значущих елементів у матриці парності, блока пам'яті результатів обчислень значень перевірки на кожній ітерації, блока пам'яті проміжних значень у ході виконання ітерації процесу декодування, блока пам'яті для запису результуючого декодованого повідомлення, а також блока видачі вихідного повідомлення, який відрізняється тим, що містить блок віднімачів, блок суматорів та блок виконання операцій виключного АБО. Комп’ютерна верстка О. Рябко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 2

ДивитисяДодаткова інформація

Автори англійськоюMusiienko Maksym Pavlovych

Автори російськоюМусиенко Максим Павлович

МПК / Мітки

МПК: H03M 13/03

Мітки: пристрій, ldpc-декодування

Код посилання

<a href="https://ua.patents.su/4-98611-pristrijj-ldpc-dekoduvannya.html" target="_blank" rel="follow" title="База патентів України">Пристрій ldpc-декодування</a>

Попередній патент: Спосіб автоматизованого створення медичних документів

Наступний патент: Автоматизована установка для вирощування рослин у штучному кліматі “адам-1″