Обчислювальна система

Номер патенту: 55033

Опубліковано: 10.12.2010

Автори: Жуков Ігор Анатолійович, Ткаченко Валентина Василівна, Клименко Ірина Анатоліївна, Жабін Валерій Іванович

Формула / Реферат

Обчислювальна система, що містить процесор і зовнішні пристрої, зв'язані між собою загальною шиною, кожний i-й зовнішній пристрій (i=1...n) містить блок переривань, перший вихід якого підключений до керуючого входу процесора, елемент АБО, елемент І, вихід якого через перший вхід елемента АБО підключений до входу блока переривань і-го зовнішнього пристрою, перші входи кожного елемента І підключені до керуючого виходу процесора, яка відрізняється тим, що кожний зовнішній пристрій містить тригер початку групи, тригер кінця групи, контролер початку групи, контролер кінця групи, інтерфейс, перший вихід якого підключений до входу тригера початку групи, вихід якого зв'язаний з другим входом елемента І та першим входом контролера початку групи, вихід якого підключений до другого входу елемента АБО, вихід якого підключений до входу блока переривань, другий вихід якого підключений до першого входу контролера кінця групи, перший вихід якого зв'язаний з другим входом контролера початку групи i+1-го зовнішнього пристрою, другий вихід інтерфейсу підключений до входу тригера кінця групи, вихід якого зв'язаний з другим входом контролера кінця групи, при цьому другий вихід контролера кінця групи і-го зовнішнього пристрою пов'язаний з третіми входами контролерів початку груп всіх n зовнішніх пристроїв, а перший вихід контролера кінця групи n-го зовнішнього пристрою підключений до другого входу контролера кінця групи 1-го зовнішнього пристрою.

Текст

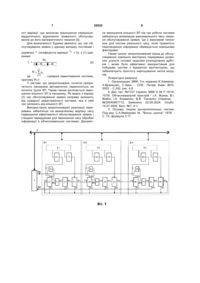

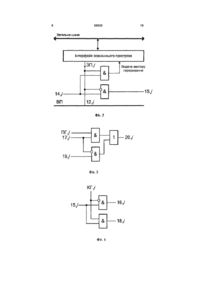

Обчислювальна система, що містить процесор і зовнішні пристрої, зв'язані між собою загальною шиною, кожний i-й зовнішній пристрій (i=1...n) містить блок переривань, перший вихід якого підключений до керуючого входу процесора, елемент АБО, елемент І, вихід якого через перший вхід елемента АБО підключений до входу блока переривань і-го зовнішнього пристрою, перші входи кожного елемента І підключені до керуючого виходу процесора, яка відрізняється тим, що кожний зовнішній пристрій містить тригер початку групи, 3 містить процесор і зовнішні пристрої, зв'язані між собою загальною шиною, кожний і-й зовнішній пристрій (і=1...n) містить блок переривань, перший вихід якого підключений до керуючого входу процесора, елемент АБО, елемент І та тригер, вихід якого зв'язаний з інформаційним входом тригера i+1-го зовнішнього пристрою та з першим входом елемента І і-го зовнішнього пристрою, вихід якого через перший вхід елемента АБО підключений до входу блоку переривань і-го зовнішнього пристрою, другий вихід якого зв'язаний з другим входом елемента АБО i+1-го зовнішнього пристрою, другі входи кожного елемента І та кожного тригера підключені до керуючого виходу процесора, причому вихід тригера та другий вихід блока переривань n-го зовнішнього пристрою підключені відповідно до інформаційного входу тригера та другого входу елемента АБО 1-го зовнішнього пристрою. Недоліком відомої системи є низька швидкодія, що обумовлено затримкою початку обслуговування переривань. В системах управління, що вирішують різного роду задачі управління в тому числі і траєкторні задачі, цикли управління характеризуються своєю неоднорідності. Таким чином у визначений момент часу виконується опитування та обробка переривань від певної кількості ЗП, що впливають на стратегію управління. Інші ж ЗП знаходяться у пасивному стані. У відомій системі реалізоване опитування всіх зовнішніх пристроїв за пріоритетним ланцюжком, незалежно від їх участі у циклі управління в даний момент часу. За великої кількості зовнішніх пристроїв довжина пріоритетного ланцюжка визначає затримку початку обслуговування переривання. В основу корисної моделі поставлено задачу удосконалення обчислювальної системи у режимі переривань шляхом зменшення затримки початку обслуговування переривань, підвищення гарантій обслуговування зовнішніх пристроїв за певний проміжок часу за рахунок динамічного скорочення пріоритетного ланцюжка і видалення із процесу обробки переривань пасивних зовнішніх пристроїв. Встановлена задача виконується тим, що в обчислювальній системі, що містить процесор і зовнішні пристрої, зв'язані між собою загальною шиною, кожний i-й зовнішній пристрій (і=1...n) містить блок переривань, перший вихід якого підключений до керуючого входу процесора, елемент АБО, елемент І, вихід якого через перший вхід елемента АБО підключений до входу блоку переривань і-го зовнішнього пристрою, перші входи кожного елемента І підключені до керуючого виходу процесора, новим є те, що у склад кожного зовнішнього пристрою введені тригер початку групи, тригер кінця групи, контролер початку групи, контролер кінця групи, програмний інтерфейс, перший вихід якого підключений до входу тригеру початку групи, вихід якого зв'язаний з другим входом елемента І та першим входом контролера початку групи, вихід якого підключений до другого входу елемента АБО, вихід якого підключений до входу блоку переривань, другий вихід якого підключений до першого входу контролера кінця групи, перший вихід якого зв'язаний з другим входом контролеру початку циклу i+1-го зовнішнього пристрою, другий 55033 4 вихід інтерфейсу підключений до входу тригера кінця групи, вихід якого зв'язаний з другим входом контролера кінця групи, при цьому другий вихід контролера кінця групи і-го зовнішнього пристрою пов'язаний з третіми входами контролерів початку групи всіх п зовнішніх пристроїв, а перший вихід контролера кінця групи n-го зовнішнього пристрою підключений до другого входу контролеру кінця групи 1-го зовнішнього пристрою. На Фіг.1 показана структурна схема обчислювальної системи; на Фіг.2 - приклад побудови блока переривань. Обчислювальна система (Фіг.1) містіть процесор 1, зовнішні пристрої 2,1,...,2.n, загальну шину 3, до якої підключені процесор 1 та зовнішні пристрої 2.1,..., 2.n. До складу кожного і-го зовнішнього пристрою входить блок переривань 4.i, програмний інтерфейс 5.i, тригер початку групи 6.i, тригер кінця групи 7.i, контролер початку групи 8.i, контролер кінця групи 9.i елемент І 10.i та елемент АБО 11.i. (структура програмного інтерфейсу та апаратура зовнішніх пристроїв, які не стосується реалізації переривань на Фіг.1 умовно не показані). Виходи 12.i блоків переривань 4.i об'єднані у єдину лінію і підключені до входу вимоги переривань (ВП) процесора 1, вихід підтвердження переривання (ПП) якого підведений до перших входів елементів І 10.i. (Технологічні особливості елементної бази повинні допускати об'єднання виходів 12.i. Наприклад, використовуються елементи з відкритим колектором, а сигнали вимоги переривань мають активний низький рівень). Перший вихід програмного інтерфейсу 5.i підключений до входу тригеру початку групи 6.i, який своїм виходом підключений до входу 13.i контролера початку групи 8.i та другого входу елемента І 10.i, вихід якого пов'язаний із першим входом елемента АБО 11.i, який своїм виходом підключений до входу 14.i блока переривань 4.i. Вихід 15.i блока переривань 4.i підведений до першого входу контролера кінця групи 9.i, вихід 16.i якого зв'язаний з входом 17.i i+1-го зовнішнього пристрою 2.(i+1). Вихід 16.n контролера кінця групи 9.n підключений до входу 17.1 контролеру кінця групи 9.1, а виходи 18.i контролерів кінця групи 9.i поєднані в єдину лінію і підключені до входів 19.i контролерів початку групи 8.i всіх n зовнішніх пристроїв 2.i. Вихід 20.i контролера початку групи 8.i підключений до другого входу елемента АБО 11.i. Другий вихід програмного інтерфейсу 5.i підключений до входу тригера кінця групи 7.i, який своїм виходом зв'язаний з другим входом контролера кінця групи 9.i. Таким чином, блоки переривань 4.i через контролери 8.i і 9.i та елемент АБО 11.i об'єднані у кільце, за рахунок управляючих сигналів, що надходять на управляючі входи контролерів початку групи 8.i та контролеру кінця групи 9.i, у склад кільця можуть входити різні зовнішні пристрої 4.i. У якості блоків переривань АЛ можуть використовуватися стандартні блоки розподілених систем переривань. Приклад логічної організації таких блоків показаний у вигляді функціональної схеми на Фіг.2. 5 Обчислювальна система працює наступним чином. У певний проміжок часу система обслуговує запити від визначеної кількості зовнішніх пристроїв 2.g, ...,2.k із складу зовнішніх пристроїв обчислювальної системи 2.1, ...,2.n. Таким чином за допомогою управляючої програми інтерфейс 5.g зовнішнього пристрою 2.g виставляє одиничний сигнал на тригері початку групи 6.g, а інтерфейс 5.k зовнішнього пристрою 2.k виставляє одиничний сигнал на тригері кінця групи 7.k. У кожний момент часу тільки в одному із тригерів 6.1,..., 6.n та тільки в одному із тригерів 7.1,...,7.n записана одиниця (наприклад, на початку обчислень - у тригері 6.1 та у тригері 7.n). Всі інші тригери встановлені в нуль. Сигнал обслуговування переривання ПП від процесора 1 буде поширюватись вздовж пріоритетного ланцюжка, що утворюють зовнішні пристрої поєднані у кільце розпочинаючи від зовнішнього пристрою 2.g і закінчуючи зовнішнім пристроєм 2.k. В обчислювальній системі застосовані фіксовані пріоритети зовнішніх пристроїв. Найвищій пріоритет має перший у ланцюжку зовнішній пристрій 2.g, тригер початку групи якого встановлений в одиницю. Готовий до обміну інформацією з процесором 1 будь який зовнішній пристрій 2.j ( j i ) із складу означеного ланцюжка зовнішніх пристроїв 2.g,...,2.k формує сигнал запиту переривання (ЗП.j) на виході 12.j. При наявності такого сигналу розривається приоритетний ланцюжок між входом 14.j та виходом 15.j блоку переривань 4.j (Фіг.2). Якщо є хоч один сигнал на виходах 12.1,..., 12.n, формується загальний сигнал вимоги переривань на вході ВП процесора 1. Після закінчення чергового циклу виконання команди процесор перериває виконання основної програми і у відповідь на сигнал ВП формує сигнал підтвердження переривання на виході ПП. Цей сигнал потрапляє у пріоритетний ланцюжок, замкнутий у кільце, починаючи з зовнішнього пристрою з найбільшим пріоритетом, так як відкритим є тільки один елемент І 10.g в цьому зовнішньому пристрої за рахунок одиничного сигналу на виході тригеру початку групи 6.g. Сигнал ПП розповсюджується по ланцюжку тільки до першого на його путі блока переривань 4.j, який виставив сигнал запиту переривання ЗП.j. В цьому блоці 4.j формується вектор переривання, який видається на загальну шину 3 та приймається в процесор 1 (див. Фіг.2). Після цього процесор починає виконувати програму обслуговування переривання і знімає сигнал ПП. Програмний інтерфейс управляється основною програмою зі сторони процесора, тобто значення тригерів початку і кінця групи встановлюються в програмному режимі відповідно до виконуваних обчислювальною системою функцій в даний час. Контролери початку групи 8.j в залежності від управляючого сигналу ПГ.j (Початок групи, див. Фіг.3) від тригеру початку групи 6.j j-го зовнішнього пристрою, переключаються або в стан наскрізної передачі сигналу по ланцюжку, у випадку якщо тригер 6.j встановлений в нульовий стан, і даний зовнішній пристрій розташований всередині кіль 55033 6 ця, або в стан початку ланцюжка, у випадку якщо тригер 6.j встановлений в одиничний стан, і даний зовнішній пристрій розташований на початку кільця. У першому випадку пріоритетний ланцюжок замикається між входом 17.j та виходом 20.j контролера початку групи, в другому - між входом 17.j та виходом 19.j контролера початку групи. Структурна схема контролеру початку групи наведена на Фіг.3. Контролери кінця групи 9.j в залежності від управляючого сигналу КГ.j (Кінець групи, див. Фіг.4) від тригеру кінця групи 7.j переключається або в стан наскрізної передачі сигналу по ланцюжку, у випадку якщо тригер 7.j встановлений в нульовий стан, і даний зовнішній пристрій розташований всередині кільця, або в стан кінця ланцюжка, у випадку якщо тригер 7.j встановлений в одиничний стан, і даний зовнішній пристрій розташований в кінці кільця. У першому випадку пріоритетний ланцюжок замикається між входом 15.j та виходом 16.j контролера кінця групи, в другому між входом 15.j та виходом 18.j контролера кінця групи. Структурна схема контролера кінця групи зображена на Фіг.4. Таким чином, в обчислювальній системі, що пропонується, забезпечується динамічне формування пріоритетного ланцюжка, що забезпечує виключення пасивних зовнішніх пристроїв із складу таких, що обпитуються, за рахунок чого зменшити час обробки переривань в обчислювальній системі. Порівняємо відому систему та систему, що пропонується, за ефективністю реалізації переривань. Ефективність системи переривань можна оцінити по величині часу затримки початку обслуговування. Взаємодію зовнішніх пристроїв (ЗП) із процесором при реалізації переривань можна розглядати як замкнену мережу масового обслуговування. У обчислювальній системі з одним пріоритетним ланцюжком зовнішні пристрої мають пріоритети, що визначаються їх позиціями в ланцюжку (ЗП 2.1g має найвищий, а ЗП 2.k - найнижчий пріоритет). Будемо вважати, що заявки мають відносні пріоритети, потік заявок є стаціонарним, а час обслуговування для всіх заявок однаковий. Тоді середній час чекання обслуговування складе: n 2 j j j1 j 1 ti 2 1 Ri j jt j 1 (1) , 1 Ri де - завантаження системи обслуговуванням заявок j-го пріоритету ( j - інтенсивність потоку заявок j-го пріоритету, tj - час обслуговування заявок); i 1 Ri 1 i k i Ri k - сумарне завантаження системи обслуговуванням заявок відповідно k 1 k 1 (i - 1) і i старших пріоритетів; j -середній час об слуговування заявок j-го пріоритету; j - коефіці 7 55033 єнт варіації, що визначає відношення середньоквадратичного відхилення тривалості обслуговування до його математичного чекання [3]. Для визначеності будемо вважати, що час обслуговування заявок у даному випадку постійний і дорівнює ржимо ti (коефіцієнти варіації R , 2 1 Ri 1 1 Ri j = 0), з (1) оде(2) n R j j 1 де - сумарне завантаження системи, причому R

ДивитисяДодаткова інформація

Назва патенту англійськоюComputing system

Автори англійськоюZhabin Valerii Ivanovych, Zhukov Ihor Anatoliiovych, Klymenko Iryna Anatoliivna, Tkachenko Valentyna Vasylivna

Назва патенту російськоюВычислительная система

Автори російськоюЖабин Валерий Иванович, Жуков Игорь Анатольевич, Клименко Ирина Анатольевна, Ткаченко Валентина Васильевна

МПК / Мітки

МПК: G06F 15/16

Мітки: система, обчислювальна

Код посилання

<a href="https://ua.patents.su/6-55033-obchislyuvalna-sistema.html" target="_blank" rel="follow" title="База патентів України">Обчислювальна система</a>

Попередній патент: Двигун внутрішнього згоряння

Наступний патент: Мобільний проекційно-звуковий комплекс

Випадковий патент: Спосіб лікування рака молочної залози