Пристрій для визначення інтенсивності спекулярної складової кольору

Номер патенту: 59965

Опубліковано: 10.06.2011

Автори: Друзюк Богдан Анатолійович, Романюк Олександр Никифорович, Ляшенко Юрій Леонідович

Формула / Реферат

Пристрій для визначення інтенсивності спекулярної складової кольору, який містить шість регістрів, чотири блоки множення, блок інверторів, два мультиплексори, блок керування, комбінаційний суматор, блок постійної пам'яті, вихід якого підключено до першого входу першого блока множення, вихід першого регістра з'єднано з першим інформаційним входом першого мультиплексора, інформаційний вхід - з першим інформаційним входом пристрою, а керуючий вхід - з першим керуючим входом пристрою, вихід блока інверторів з'єднано з першим інформаційним входом комбінаційного суматора, другий вхід якого підключено до четвертого інформаційного входу пристрою, а вихід з'єднано з інформаційним входом третього регістра, вихід якого підключено до першого інформаційного входу першого мультиплексора, інформаційні входи четвертого, п'ятого і шостого регістрів підключено відповідно до п'ятого, шостого і сьомого інформаційних входів пристрою, п'ятий, шостий і сьомий керуючі входи якого з'єднані відповідно з керуючими входами четвертого, п'ятого і шостого регістрів, вихід другого мультиплексора з'єднано з другим входом першого блока множення, вихід якого з'єднано з входом блока інверторів, вихід першого мультиплексора підключено до входу блока постійної пам'яті, перший, другий і третій входи блока керування з'єднано відповідно з першим, другим і третім керуючими входами пристрою, другий інформаційний та четвертий керуючі входи якого підключені відповідно до інформаційного та керуючого входів другого регістра, вихід якого з'єднано з першим інформаційним входом другого мультиплексора, другий інформаційний вхід якого підключено до третього інформаційного входу пристрою, керуючий вихід пристрою підключено до третього виходу блока керування, другий вихід якого з'єднано з керуючим входом третього регістра, керуючий вхід другого мультиплексора підключено до першого виходу блока керування, який містить три D-тригери, елемент І, три елементи І-HI, інвертор, вхід якого підключено до третього входу першого елемента І-HI, першого входу другого елемента І-HI і другого входу блока керування, третій вхід якого з'єднано з другим входом елемента І, R-входами другого і третього тригерів, S-входи яких підключено до D- і S-входів першого тригера і виходу логічної одиниці, С-входи другого і третього D-тригерів з'єднано з виходом інвертора, прямий вихід першого тригера підключено до D-входу другого тригера, прямий вихід якого з'єднано з D-входом третього тригера і другим входом першого елемента I-HI, вихід якого підключено до першого входу третього елемента І-HI і першого входу елемента І, вихід якого з'єднано з R-входом першого тригера, інверсний вихід другого D-тригера підключено до другого входу другого елемента І-HI, третій вхід якого з'єднано з першим виходом блока керування і третім входом другого елемента І-HI, вихід якого підключено до другого входу третього елемента І-HI і третього виходу блока керування, перший вхід якого з'єднано з С-входом першого тригера, а другий вихід - з виходом третього елемента І-HI, який відрізняється тим, що введено п'ятий блок множення та другий блок пам'яті, вхід якого підключений до виходу другого регістра, а вихід - до другого входу п'ятого блока множення, перший вхід якого з'єднаний з виходом третього регістра, другий вхід - з виходом другого блока пам'яті, а вихід з першими входами другого, третього і четвертого блоків множення.

Текст

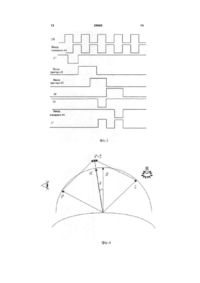

Пристрій для визначення інтенсивності спекулярної складової кольору, який містить шість регістрів, чотири блоки множення, блок інверторів, два мультиплексори, блок керування, комбінаційний суматор, блок постійної пам'яті, вихід якого підключено до першого входу першого блока множення, вихід першого регістра з'єднано з першим інформаційним входом першого мультиплексора, інформаційний вхід - з першим інформаційним входом пристрою, а керуючий вхід - з першим керуючим входом пристрою, вихід блока інверторів з'єднано з першим інформаційним входом комбінаційного суматора, другий вхід якого підключено до четвертого інформаційного входу пристрою, а вихід з'єднано з інформаційним входом третього регістра, вихід якого підключено до першого інформаційного входу першого мультиплексора, інформаційні входи четвертого, п'ятого і шостого регістрів підключено відповідно до п'ятого, шостого і сьомого інформаційних входів пристрою, п'ятий, шостий і сьомий керуючі входи якого з'єднані відповідно з керуючими входами четвертого, п'ятого і шостого регістрів, вихід другого мультиплексора з'єднано з другим входом першого блока множення, вихід якого з'єднано з входом блока інверторів, вихід першого мультиплексора підключено до входу блока постійної пам'яті, перший, другий і третій входи блока керування з'єднано відповідно з першим, другим і третім керуючими входами пристрою, другий інформаційний та четвертий керуючі входи якого підключені відповідно до інформацій U 2 (19) 1 3 59965 4 лючено до інформаційного входу пристрою, а вилючено до третього інформаційного входу приходи підключено до входу першого суматора та до строю, керуючий вихід пристрою підключено до першого входу схеми порівняння, вхід першого третього виходу блоку керування, другий вихід суматора підключено до виходу зсувного регістра, якого з'єднано з керуючим входом третього регіста вихід з'єднано із другим входом схеми порівнянра, керуючий вхід другого мультиплексора підклюня та із першим входом другого суматора, перший чено до першого виходу блока керування. вхід другого суматора підключено до виходу перБлок керування містить три D-тригери, елешого суматора, другий вхід - до рівня логічної одимент І, три елементи І-НІ, інвертор, вхід якого підкниці, а вихід підключено до обох входів першого лючено до третього входу першого елемента І-НІ, блока множення, обидва входи першого блока першого входу другого елемента І-HI і другого множення підключено до виходу другого суматора, входу блоку керування, третій вхід якого з'єднано з а вихід підключено до обох входів другого блока другим входом елемента І, R-входами другого і множення, обидва входи другого блока множення третього тригерів, S-входи яких підключено до D- і підключено до виходу першого блока множення, а S-входів першого тригера і виходу логічної одинивихід з'єднано із першим входом мультиплексора, ці, С-входи другого і третього D-тригерів з'єднано з перший вхід схеми порівняння з'єднано з зсувним виходом інвертора, прямий вихід першого тригера регістром, другий вхід із виходом першого суматопідключено до D-входу другого тригера, прямий ра, а вихід підключено до стробового входу мульвихід якого з'єднано з D-входом третього тригера і типлексора, перший вхід мультиплексора підклюдругим входом першого елемента І-HI, вихід якого чено до виходу другого блоку множення, другий підключено до першого входу третього елемента Івхід заземлено, стробовий вхід підключено до виHI і першого входу елемента І, вихід якого з'єднано ходу схеми порівняння, а вихід підключено до виз R-входом першого тригера, інверсний вихід друходу пристрою.(патент №5739820 США, МПК6 гого D-тригера підключено до другого входу другоG06Т 15/50,1998, Фіг.7C, 7D). го елемента І-HI, третій вхід якого з'єднано з перНедолік пристрою полягає в низькій точності шим виходом блоку керування і третім входом відтворення зони затухання відблиску через різке другого елемента І-HI, вихід якого підключено до спадання функції та невідповідність розрахунків другого входу третього елемента I-HI і третього закону збереження енергії. виходу блоку керування, перший вхід якого з'єднаНайбільш близьким до технічного рішення, що но з С-входом першого тригера, а другий вихід - з заявляється, є пристрій для визначення інтенсиввиходом третього елемента І-НІ. (патент України ності спекулярної складової кольору, який включає №22802, М.КЛ. G06Т 15/50, Бюл. №5, 2007 р.). шість регістрів, чотири блоки множення, блок інНедоліком пристрою є низька реалістичність верторів, два мультиплексори, блок керування, відтворення спекулярної складової кольору, оскікомбінаційний суматор, блок постійної пам'яті, вильки при обчисленнях не виконується закон збехід якого підключено до першого входу першого реження енергії. блоку множення, вихід першого регістра з'єднано з В основу корисної моделі поставлено задачу першим інформаційним входом першого мультипстворення пристрою для визначення інтенсивності лексора, інформаційний вхід - з першим інформаспекулярної складової кольору, у якому за рахунок ційним входом пристрою, а керуючий вхід - з первведення нових елементів і зв'язків, а також, викошим керуючим входом пристрою, вихід блока ристання нової функціональної залежності досягаінверторів з'єднано з першим інформаційним вхоється підвищення реалістичності визначення спедом комбінаційного суматора, другий вхід якого кулярної складової кольору за рахунок підключено до четвертого інформаційного входу дотримання закону збереження енергії. пристрою, а вихід з'єднано з інформаційним вхоПоставлена задача досягається тим, що в дом третього регістра, вихід якого підключено до пристрій для визначення спекулярної складової першого інформаційного входу першого мультипкольору, який містить шість регістрів, чотири блоки лексора і перших входів другого, третього і четвемноження, блок інверторів, два мультиплексори, ртого блоків множення, другі входи яких з'єднані блок керування, комбінаційний суматор, блок посвідповідно з виходами четвертого, п'ятого і шостотійної пам'яті, вихід якого підключено до першого го регістрів, інформаційні входи яких підключено входу першого блока множення, вихід першого відповідно до п'ятого, шостого і сьомого інформарегістра з'єднано з першим інформаційним входом ційних входів пристрою, п'ятий, шостий і сьомий першого мультиплексора, інформаційний вхід - з керуючі входи якого з'єднані відповідно з керуючипершим інформаційним входом пристрою, а керуми входами четвертого, п'ятого і шостого регістрів, ючий вхід - з першим керуючим входом пристрою, вихід другого мультиплексора з'єднано з другим вихід блока інверторів з'єднано з першим інфорвходом першого блока множення, вихід якого з'єдмаційним входом комбінаційного суматора, другий нано з входом блока інверторів, вихід першого вхід якого підключено до четвертого інформаціймультиплексора підключено до входу блока посного входу пристрою, а вихід з'єднано з інформатійної пам'яті, перший, другий і третій входи блока ційним входом третього регістра, вихід якого підккерування з'єднано відповідно з першим, другим і лючено до першого інформаційного входу першого третім керуючими входами пристрою, другий інмультиплексора, інформаційні входи четвертого, формаційний та четвертий керуючий входи якого п'ятого і шостого регістрів підключено відповідно підключені відповідно до інформаційного та керудо п'ятого, шостого і сьомого інформаційних входів ючого входів другого регістра, вихід якого з'єднано пристрою, п'ятий, шостий і сьомий керуючі входи з першим інформаційним входом другого мультиякого з'єднані відповідно з керуючими входами плексора, другий інформаційний вхід якого підкчетвертого, п'ятого і шостого регістрів, вихід друго 5 59965 6 го мультиплексора з'єднано з другим входом перПристрій включає відповідно перший-шостий шого блока множення, вихід якого з'єднано з вхо1, 2, 9-12 регістри, перший та другий 3, 4 мультипдом блока інверторів, вихід першого мультиплеклексори, перший та другий 5, 38 блоки постійної сора підключено до входу блоку постійної пам'яті, пам'яті, перший-п'ятий 6, 13-15, 39 блоки множенперший, другий і третій входи блоку керування ня, блок інверторів 7, комбінаційний суматор 8, з'єднано відповідно з першим, другим і третім кеблок керування 16, перший-сьомий 17-23 інфорруючими входами пристрою, другий інформаціймаційні входи пристрою, перший-третій 24-26 інний та четвертий керуючі входи якого підключені формаційні виходи пристрою, перший-восьмий 27відповідно до інформаційного та керуючого входів 29, 30-34 керуючі входи та керуючий вихід 35 придругого регістра, вихід якого з'єднано з першим строю. інформаційним входом другого мультиплексора, Перший вхід керування 16 з'єднано з першим другий інформаційний вхід якого підключено до керуючим входом 27 пристрою, другий вхід з'єднатретього інформаційного входу пристрою, керуюно з другим керуючим входом 28 пристрою, третій чий вихід пристрою підключено до третього виходу вхід з'єднано із третім 29 керуючим входом приблока керування, другий вихід якого з'єднано з строю, перший вихід 36 підключено до керуючих керуючим входом третього регістра, керуючий вхід входів першого 3 та другого 4 мультиплексорів, другого мультиплексора підключено до першого другий вихід 37 підключено до керуючого входу виходу блока керування, який містить три Dтретього 9 регістра, а третій вихід з'єднано з керутригери, елемент І, три елементи І-НІ, інвертор, ючим входом 35 пристрою. вхід якого підключено до третього входу першого Блок 16 керування включає елемент І 40, перелемента І-HI, першого входу другого елемента Іший-третій 41-43 D-тригери, інвертор 44, першийHI і другого входу блока керування, третій вхід третій 45-47 елементи І-НІ. якого з'єднано з другим входом елемента І, RПерший інформаційний вхід 17 пристрою підквходами другого і третього тригерів, S-входи яких лючено до інформаційного входу регістра 1. Керупідключено до D- і S-входів першого тригера і виючий вхід пристрою з'єднано з керуючим входом ходу логічної одиниці, С-входи другого і третього першого регістра 1 і першим 27 входом блока 16 D-тригерів з'єднано з виходом інвертора, прямий керування. Вихід регістра 1 підключено до першовихід першого тригера підключено до D-входу друго входу першого мультиплексора 3, вихід якого гого тригера, прямий вихід якого з'єднано з Dз'єднано з входом першого блока 5 постійної павходом третього тригера і другим входом першого м'яті, а другий вхід з виходом третього регістра 9, елемента I-HI, вихід якого підключено до першого вихід третього 9 регістра з'єднано з першим вховходу третього елемента І-HI і першого входу дам п'ятого 39 блоку множення. Другий вхід п'ятоелемента І, вихід якого з'єднано з R-входом перго 39 блока множення з'єднано з виходом другого шого тригера, інверсний вихід другого D-тригера 38 блока постійної пам'яті, а вихід з першими вхопідключено до другого входу другого елемента Ідами другого 13, третього 14 і п'ятого 15 блоків HI, третій вхід якого з'єднано з першим виходом множення, виходи яких підключено відповідно до блока керування і третім входом другого елемента першого 24, другого 25 і третього 26 інформаційІ-HI, вихід якого підключено до другого входу трених виходів пристрою. П'ятий 21, шостий 22, сьотього елемента І-HI і третього виходу блока керумий 23 інформаційні входи пристрою підключені вання, перший вхід якого з'єднано з С-входом до інформаційних входів відповідно четвертого 10, першого тригера, а другий вихід - з виходом треп'ятого 11 і шостого 12 регістрів, керуючі входи тього елемента І-HI, введено п'ятий блок множеняких з'єднано відповідно з п'ятим 31, шостим 32 і ня та другий блок пам'яті, вхід якого підключений сьомим 33 керуючими входами пристрою. Виходи до виходу другого регістра, а вихід - до другого регістрів 10, 11, 12 підключено відповідно до друвходу п'ятого блока множення, перший вхід якого гих входів другого 13, третього 14 і четвертого 15 з'єднаний з виходом третього регістра, другий вхід блоків множення. Перший і другий входи першого - з виходом другого блока пам'яті, а вихід з перблока множення 6 з'єднано відповідно з виходом шими входами другого, третього і четвертого блоблока 5 постійної пам'яті і виходом другого мульків множення. типлексора 4, а вихід - з входом блока 7 інвертоНа Фіг.1 зображено схему пристрою. рів. Перший інформаційний вхід комбінаційного На Фіг.2 зображено схему блоку 16 керування. суматора 8 підключено до виходу блока 7 інвертоНа Фіг.3 зображено часову діаграму роботи рів. На другий вхід 20 комбінаційного суматора 8 блока 16 керування. подається операнд, який дорівнює одиниці. НайНа Фіг.4 зображено хід променів для моделі простіше це зробити монтажним шляхом, наприосвітлення Бліна. клад, подавши на перший розряд інформаційного На Фіг.5 зображено графіки інтеграла по повевходу 20 одиницю, а всі старші розряди заземлирхні для дистрибутивної функції відбивної здатноти. Вхід переносу 34 суматора 8 підключено до сті (ДФВЗ) поверхні, згідно моделі Бліна та для виходу логічної одиниці. Підключення до цього апроксимаційної функції з нормалізаційним коефірівня обумовлено тим, що суматор 8 працює в цієнтом, що пропонується. режимі віднімання. Вихід комбінаційного суматора На Фіг.6 зображено графік інтеграла по повер8 з'єднано з інформаційним входом третього регісхні для ДФВЗ, яка використовується у пристрої тра 9, керуючий вхід якого підключено до другого прототипі та показано, що його значення переви37 виходу блока 16 керування, перший вихід 36 щують 1. якого з'єднано з керуючим входом першого мульНа Фіг.7 зображено параметри ДФВЗ. типлексора 3 і керуючим входом другого мультиплексора 4, перший інформаційний вхід якого підк 7 59965 8 лючено до виходу другого регістра 2, вихід другого L та V та нормалізації отриманого вектору (див. регістра 2 підключено до першого інформаційного Фіг.4). входу другого мультиплексора 4 та до входу друУ пристрої використовується наступна апрокгого блока постійної пам'яті 38. Другий інформасимація дистрибутивної функції. ційний вхід 18 пристрою підключено до інформаЗапишемо функцію у еквівалентному виді: ційного входу другого регістра 2, керуючий вхід cosn 2nlog2 (cos ) , (3) якого з'єднано з четвертим 30 керуючим входом В останньому виразі позначимо n log2 (cos ) пристрою. Другий 28 і третій 29 керуючі входи пристрою підключені відповідно до другого і третього через х, тобто: входів блока 16 керування, вихід якого з'єднано з 2nlog2 (cos ) 2x. керуючим виходом 35 пристрою. На третій вхід 19 х Знайдемо наближеня функції 2 функцією виду пристрою, який з'єднано з другим інформаційним f(x)=Alog2(1-х)+В на проміжку [-1,0]. входом другого мультиплексора 4, подається знаЗнайдемо невідомі А і В. чення ½. Це можна здійснити, наприклад, монтажПри х=0 ною комутацією. 1=Alog2(1)+B. Другий вхід блока 16 керування з'єднано з З останнього рівняння знаходимо, що B=1. входом інвертора 44, третім входом першого еле1 мента І-HI 45 і першим входом другого елемента ІПри х=-1 отримуємо таке рівняння = Alog2(2) НІ 46. Вихід першого елемента І-НІ 45 з'єднано з 2 першим входом третього елемента І-НІ 47 і пер1 + B. Враховуючи, що В=1, знаходимо, що А=- . шим входом елемента І 40, другий вхід якого підк2 лючено до третього входу блока 16 керування і Rх 1 Таким чином 2 1- log2(1-х). входів другого 42 і третього 43 D-тригерів. Прямий 2 вихід другого D-тригера 42 з'єднано з D-входом З урахуванням отриманої формули запишемо третього D-тригера 43 і другим входом першого вираз (3) таким чином: елемента І-HI 45, перший вхід якого підключено до 1 інверсного виходу третього D-тригера 43. Інверсcosn 2nlog2 (cos ) 1 log2(1 n log2 cos ). (5) 2 ний вихід другого D-тригера 42 підключено до друНа Фіг.6 зображено графік відповідного інтеггого входу другого елемента І-HI 46, третій вхід рала, який показує, що для апроксимаційної модеякого з'єднано із прямим виходом третього Dлі не виконується закон збереження енергії. тригера 43 і першим виходом блока 16 керування. Закон збереження енергії стосовно ДФВЗ пеС-входи другого 42 і третього 43 D-тригерів підкредбачає, що кількість світла, яке відбилось від лючено до виходу інвертора 44. D-вхід першого Dповерхні не може перевищувати кількість світла, тригера 41, S-входи першого 41, другого 42 і треяке потрапило на поверхню. У сферичних коордитього 43 D-тригерів з'єднано з виходом логічної натах умова справедливості закону збереження одиниці. Прямий вихід першого D-тригера 41 підкенергії запишеться так: лючено до D-входу другого D-тригера 42. Вихід елемента І-HI 46 підключено до другого входу тре2 тього елемента І-НІ 47 і до третього виходу 35 0 02 BRDF(S V ) cos sin dd 1 , (6) блока 16 керування, другий вихід 37 якого з'єднано де з виходом третього елемента І-HI 47.Вихід елемеі - зенітний (полярний) кут вхідного променя; нта І 40 підключено до R-входу першого D-тригера к - зенітний (полярний) кут відбитого променя; 41. і - азимутальний кут вхідного променя; При зафарбовуванні за методом Фонга інтенк - азимутальний кут відбитого променя; сивність спекулярної складової кольору визначаdwi sin ididi ; ють за формулою: n , (I) dwr sin r dr dr ; I Ilk s cos S - напрямок на джерело світла; де Il - інтенсивність джерела світла, ks - коеV - напрямок на спостерігача; фіцієнт дзеркального відбиття, n - коефіцієнт спеПерераховані кути зображено на Фіг.7. кулярності поверхні, який знаходиться в діапазоні Знайдемо в загальному випадку значення ін [1-1000], - кут між вектором нормалі N до повертеграла (6) для функції (5): /2 n2 хні в заданій точці і вектором півшляху H, cosn 2 (2nlog(cos(x )2) ) cos( x ) sin x dx 0 2 дистрибутивна функція відбивної здатності повер Таким чином, нормалізаційний коефіцієнт для хні (BRDF). Вектор H розраховується за формукосинус-квадратичної апроксимаційної функції у лою (2). загальному вигляді такий: LV 2 H , (2) LV n2 На Фіг.5 зображено графіки інтеграла по пове Вектори L та V - одиничні вектори, що вирхні для дистрибутивної функції відбивної здатнозначають відповідно місце розташування джерела сті поверхні (ДФВЗ) згідно моделі Бліна та для світла та спостерігача. Як видно з формули (1), апроксимаційної функції з нормалізаційним коефівектор Н знаходиться шляхом додавання векторів цієнтом, що пропонується. Пристрій працює наступним чином. 9 59965 10 На другий керуючий вхід 28 пристрою постугістр 9, для чого на виході 37 блока 16 керування пає опорна імпульсна послідовність, на третій 29 формують імпульс запису. Як зазначалося раніше, керуючий вхід пристрою подається імпульс устаn 1 1- Iog2(1-n·log2cos)cos . новки в заданий стан. Сигнал, який поступає на 2 перший 27 керуючий вхід пристрою для запису Для кожного n у другому блоці 38 постійної операнду в перший регістр 1, є одночасно сигнапам'яті зберігається нормалізаційний коефіцієнт, лом початку роботи пристрою. який введено для забезпечення виконання закону У початковий момент часу в другий регістр 2 збереження енергії. Значення n із виходу другого заноситься значення коефіцієнта спекулярності n. регістра 2 подається на другий блок 38 постійної Для цього його значення від зовнішнього пристрою пам'яті, на виході якого формується коефіцієнт виставляється на другий 18 інформаційний вхід 2 , який подається на другий вхід п'ятого блока пристрою, а на четвертий керуючий вхід 30 приn2 строю подається передній фронт сигналу запису. 2 1 На перший інформаційний вхід 17 пристрою множення 39, утворене значення (1- Iog2(12 n2 виставляється значення cos, яке записується в n n·log2cos))cos з виходу якого подається на перший регістр 1 переднім фронтом сигналу запиперші входи другого 13, третього 14 та четвертого су, який подається на перший 27 керуючий вхід 15 блоків множення. пристрою. Вказаний фронт сигналу, який також У регістрах 10, 11, 12 зберігаються відповідно поступає на перший вхід блока 16 керування, визначення R, G, В складових інтенсивності кольору, значає початок перетворень. Оскільки на першому які перемножуються з апроксимованим значенням керуючому виході 36 блока 16 керування, який n cos , і утворюють складові спекулярної інтенсивз'єднано з керуючим входом першого мультиплекності кольору. сора З, формується рівень логічного нуля, то знаБлок 16 керування працює наступним чином. У чення cos з виходу першого регістра 1 через пепочатковий момент часу на третій керуючий вхід рший мультиплексор 3 подається на вхід першого 29 пристрою поступає імпульс інверсної полярносблока 5 постійної пам'яті. На виході вказаного блоті, під дією якого перший 42 і другий 43 D-тригери ка формується операнд log2 cos , який поступає обнуляються. Оскільки при цьому на виході перна другий вхід першого блока 6 множення. Оскільшого елемента І-HI 45 присутній рівень логічної ки на керуючому вході другого мультиплексора 4 одиниці, то імпульс зі входу 29, пройшовши через присутній рівень логічного нуля, то значення коеелемент І 40, обнулить і перший D-тригер 41. Тафіцієнта спекулярності n з виходу другого регістра ким чином, під дією імпульсу установки в заданий 2 через другий мультиплексор 4 подається на друстан, всі D-тригери блока 16 керування знаходятьгий вхід першого блока 6 множення, на виході якося в нульовому стані. го формується значення n·log2cos. На виході Переднім фронтом імпульсу запису операнду комбінаційного суматора 8 знаходять різницю 1в перший регістр 1, який подається на перший кеn·log2cos. Для цього з використанням блока 7 . руючий вхід 27 пристрою, в одиничний стан буде інверторів значення n log2 cos інвертують, а на переведено D-тригер 41. Переднім фронтом імпудругий вхід комбінаційного суматора подають знальсної послідовності, яка формується на виході 28 чення одиниці. Оскільки відніманню виконують у інвертора 44, у одиничний стан буде переведено доповняльному коді, то на вхід переносу комбінадругий D-тригер 42, а через період і третій Dційного суматора 8 подають рівень логічної одинитригер 43. Перший 45 і другий 46 елементи І-HI ці. виділяють проміжки часу між одиничним і нульоЗначення 1-n·log2cos заносять в третій ревим станом відповідних D-тригерів і пропускають гістр 9, для чого на другому виході 37 блока 16 за цей час всього один одиничний імпульс від опокерування формують сигнал запису в третій рерної імпульсної послідовності, яка поступає на гістр 3. керуючий вхід 28 пристрою. Імпульс інверсної поПісля виконання зазначених дій на виході 36 лярності, який формується на виході першого блока керування формується рівень логічної одиелемента І-HI 45 обнулить перший D-тригер 41. Це ниці, під дією якого на виходи першого 3 і другого призведе до того, що спочатку обнулиться другий 4 мультиплексорів передаються операнди з їх друD-тригер 42, а через такт і третій D-тригер 43. Два гих інформаційних входів. імпульси інверсної полярності, які формуються зі Значення 1-n·log2cos з виходу третього 9 резміщенням в один період імпульсної послідовності, гістра через перший мультиплексор 3 подається яка поступає на другий керуючий вхід 28 прина вхід першого блока 5 постійної пам'яті, на вихострою, об'єднуються з використанням третього ді якого формується операнд log2(1-n·log2cos). елемента І-HI 47. Передній фронт імпульсу на кеОскільки через другий мультиплексор 4 на другий руючому вході 35 пристрою сигналізує, що на вхід першого блока 6 множення подається значенпершому 24 другому 25 і третьому 26 інформаційня ½, то на виході першого блока 6 множення фоних виходах сформовано спекулярну складову 1 кольору. рмується значення Iog2(1-n·log2cos), яке інвер2 У запропонованому пристрої введено норматується блоком 7 інверторів. лізаційні коефіцієнти для кожного значення n. ТаНа виході комбінаційного суматора 8, який ким чином підвищено реалістичність відтворення працює у режимі віднімання, формується значення спекулярної складової кольору, оскільки обчислене значення відповідає закону збереження енергії. 1 1- Iog2(1-n·log2cos), яке записують в третій ре2 11 59965 12 13 59965 14 15 59965 16 17 Комп’ютерна верстка А. Рябко 59965 Підписне 18 Тираж 24 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for determination of specular component color intensity

Автори англійськоюRomaniuk Oleksandr Nykyforovych, Liashenko Yurii Leonidovych, Druziuk Bohdan Anatoliiovtch

Назва патенту російськоюУстройство для определения интенсивности спекулярной составляющей цвета

Автори російськоюРоманюк Александр Никифорович, Ляшенко Юрий Леонидович, Друзюк Богдан Анатольевич

МПК / Мітки

МПК: G06T 15/00

Мітки: складової, пристрій, визначення, спекулярної, інтенсивності, кольору

Код посилання

<a href="https://ua.patents.su/9-59965-pristrijj-dlya-viznachennya-intensivnosti-spekulyarno-skladovo-koloru.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення інтенсивності спекулярної складової кольору</a>

Попередній патент: Двотактний симетричний підсилювач струму

Наступний патент: Генератор імпульсів тиску релейної диференціальної дії

Випадковий патент: Спосіб імпульсної гальванізації ранових поверхонь розчином вітаміну в1