Система автоматичного контролю параметрів газотурбінного двигуна

Формула / Реферат

Система автоматичного контролю параметрів газотурбінного двигуна, яка містить блок формувачів, обчислювач, з'єднаний з виходом кожного з двох операційних блоків, та послідовно з'єднані блок нормалізаторів, комутатор та аналого-цифровий перетворювач, другий вхід комутатора з'єднаний з другим виходом першого операційного блока, яка відрізняється тим, що додатково введені блок контролю вхідних ланцюгів, блок еталонів, другий комутатор, блок узгодження, другий блок нормалізаторів, третій комутатор, другий аналого-цифровий перетворювач, блок комутації частоти, блок керованих узгоджуючих пристроїв, джерело напруги, блок конденсаторів, блок компараторів, блок одновібраторів, блок сигналізаторів, генератор еталонної частоти, елемент АБО та блок елементів І, перший вхід системи через блок узгодження та другий комутатор з'єднаний з першим та другим блоками нормалізаторів, вихід блока узгодження через блок контролю вхідних ланцюгів також з'єднаний з другим комутатором і двома операційними блоками, останній вхід другого комутатора з'єднаний з виходом блока еталонів, другий блок нормалізаторів через третій комутатор та другий аналого-цифровий перетворювач з'єднаний з входом другого операційного блока, входи блока конденсаторів з'єднані з другими входами системи, при цьому один його вхід з'єднаний з виходом джерела напруги, а другий - із входом блока керованих узгоджуючих пристроїв, вихід якого через блок компараторів та блок одновібраторів з'єднаний з елементом АБО та блоком елементів І, другий вхід блока компараторів з'єднаний з виходом джерела напруги, другий вихід блока одновібраторів з'єднаний з першим та другим операційними блоками, вихід блока конденсаторів через блок формувачів та блок комутації частоти з'єднаний з першим та другим операційними блоками, другий вихід блока формувачів через блок сигналізаторів та елемент АБО з'єднаний з другим входом блока комутації частоти, останній вхід якого з'єднаний з генератором еталонної частоти, другий вихід блока сигналізаторів через блок елементів І з'єднаний з першим та другим операційними блоками, вихід першого аналого-цифрового перетворювача з'єднаний з першим операційним блоком, останні виходи якого з'єднані з блоком контролю вхідних ланцюгів та входом другого операційного блока, останній вхід третього комутатора з'єднаний з другим операційним блоком, останні входи першого операційного блока та блока керованих узгоджуючих пристроїв з’єднані з відповідними виходами другого операційного блока, вихід обчислювача є виходом системи.

Текст

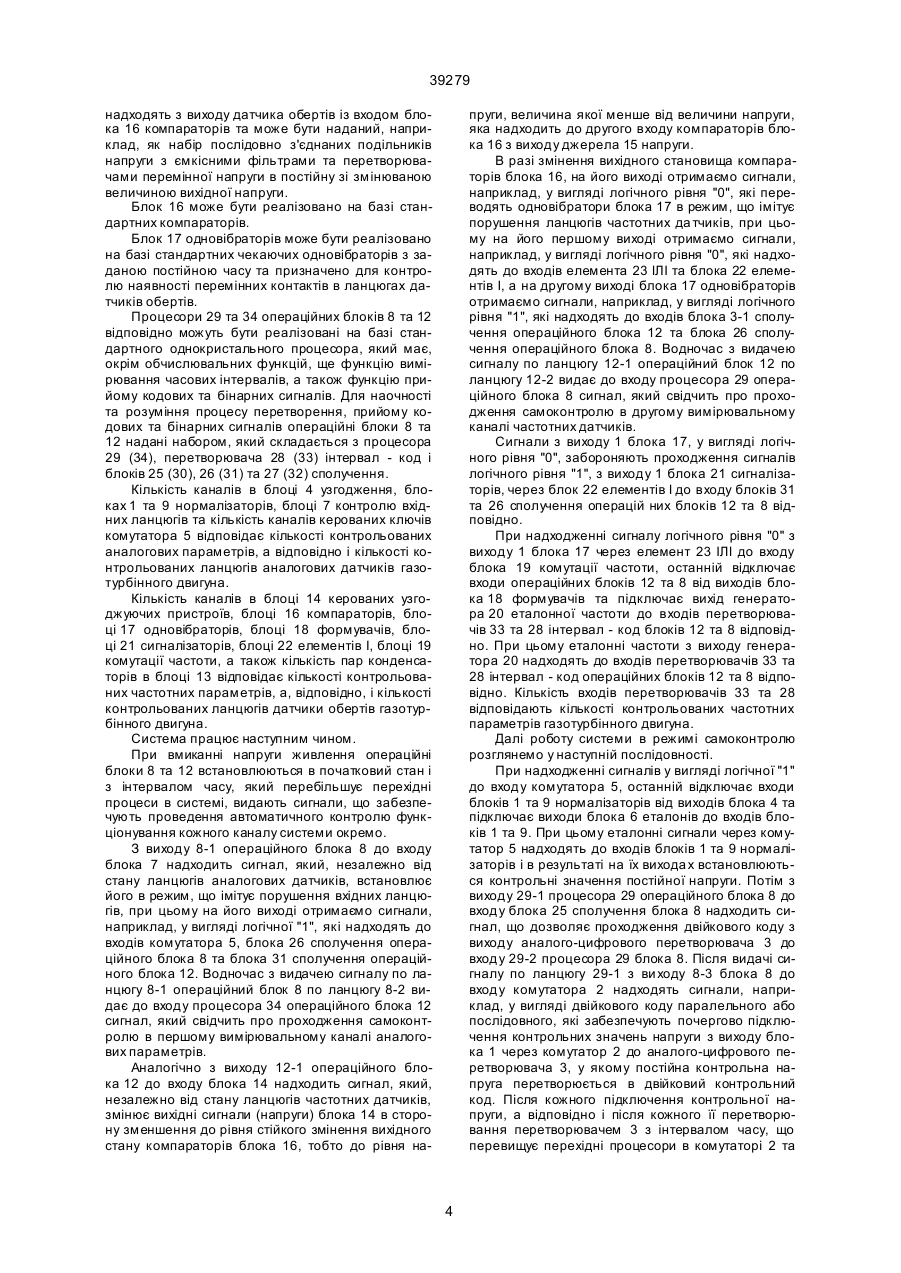

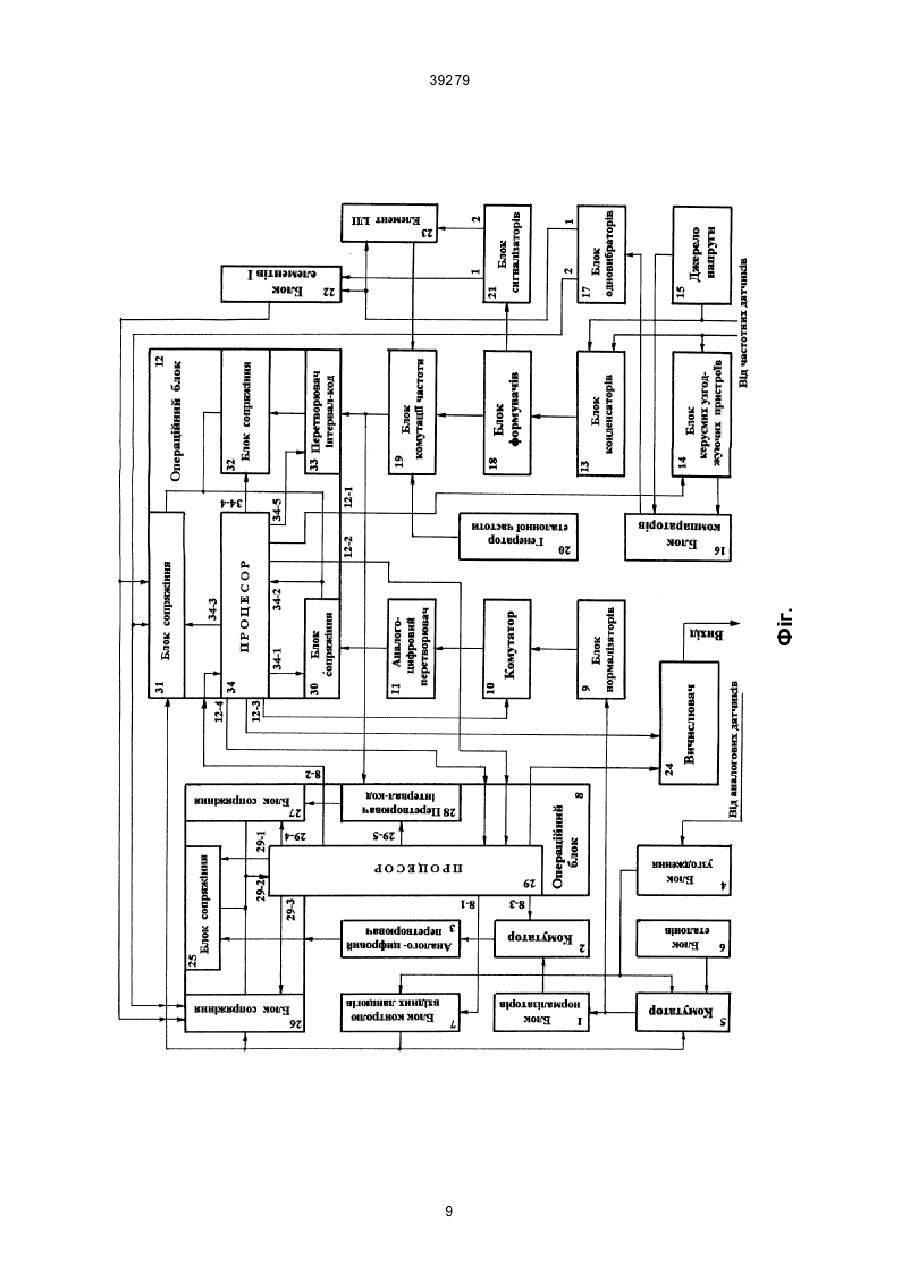

Система автоматичного контролю параметрів газотурбінного двигуна, яка містить блок формувачів, обчислювач, з'єднаний з виходом кожного з двох операційних блоків, та послідовно з'єднані блок нормалізаторів, комутатор та аналогоцифровий перетворювач, другий вхід комутатора з'єднаний з другим виходом першого операційного блока, яка відрізняється тим, що додатково введені блок контролю вхідних ланцюгів, блок еталонів, другий комутатор, блок узгодження, другий блок нормалізаторів, третій комутатор, др угий аналого-цифровий перетворювач, блок комутації частоти, блок керованих узгоджуючи х пристроїв, джерело напруги, блок конденсаторів, блок компараторів, блок одновібраторів, блок сигналізаторів, генератор еталонної частоти, елемент ІЛІ та блок елементів І, перший вхід системи через блок узгодження та другий комутатор з'єднаний з першим та другим блоками нормалізаторів, вихід блока узгодження через блок контролю вхідних ланцюгів також з'єднаний з другим комутатором і двома операційними блоками, останній вхід другого комутатора з'єднаний з виходом блока еталонів, другий блок нормалізаторів через третій комутатор А (54) СИСТЕМА АВТОМАТИЧНОГО КОНТРОЛЮ ПАРАМЕТРІВ ГАЗОТУРБІННОГО ДВИГУНА 39279 будуть напруги мінімальні чи максимальні які не відображають фізичний стан параметрів контрольованого агрегату. Найближчою за технічною суттю та е фектом, що досягається, до технічного рішення за винаходом є "Система автоматичного контролю параметрів газотурбінного двигуна" (див.: А.с. СРСР № 786434, кл. F02C9/28, G06F15/46), яка має формувач, обчислювач, з'єднаний з виходом кожного з двох програмних (операційних) блоків та послідовно з'єднані блок нормалізаторів, комутатор та аналого-цифровий перетворювач. Вказана система має наступні недоліки: відсутній контроль порушення вхідних ланцюгів системи; недостатня достовірність контролю параметрів внаслідок відсутності контролю функціонування; недостатня надійність та завадостійкість внаслідок відсутності контролю функціонування при порушенні вхідних ланцюгів, так як при порушенні вхідних ланцюгів по каналу аналогових датчиків на виході блоку нормалізаторів будуть напруги мінімальні або максимальні, а при порушенні вхідних ланцюгів по каналу частотних да тчиків в їхніх лініях зв'язку будуть наводитися сигнали перешкоди від електромагнітного впливу електроагрегатів газотурбінного двигуна, що не відображає фізичного стану його параметрів; низька функціональна надійність системи внаслідок відсутності резервного накопичування інформації в кожному вимірювальному тракті в цілому про стан параметрів газотурбінного двигуна. Передбачений винахід направлено для утворення системи, яка має високу функціональну надійність (забезпечується оптимальним поблоковим резервуванням вимірювальних трактів з накопичуванням в кожному каналі повної інформації про стан газотурбінного двигуна), завадостійкість та достовірність контролю параметрів (забезпечується автоматичним контролем функціонування, з видачею контрольних кодів, при порушеннях вхідних ланцюгів датчиків). Метою винаходу є підвищення функціональної надійності, достовірності контролю та завадостійкості, розширення функціональних можливостей системи за допомогою введення поблокового резервування вимірювальних каналів з накопичуванням інформації в кожному каналі в цілому про стан газотурбінного двигуна та автоматичного контролю функціонування при порушенні вхідних ланцюгів (ланцюгів датчиків) системи. Поставлена мета досягається тим, що у відому систему, яка містить блок формувачів, обчислювач, з'єднаний з виходом кожного з двох операційних блоків та послідовно з'єднані блок нормалізаторів, комутатор та аналого-цифровий перетворювач, другий вхід комутатора з'єднаний з другим виходом першого операційного блока, додатково введені блок контролю вхідних ланцюгів, блок еталонів, другий комутатор, блок узгодження, другий блок нормалізаторів, третій комутатор, другий аналого-цифровий перетворювач, блок комутації частоти, блок керованих узгоджуючи х пристроїв, джерело напруги, блок конденсаторів, блок компараторів, блок одновібраторів, блок сигналізаторів, генератор еталонної частоти, елемент ІЛІ та блок елементів І, перший вхід системи через блок узгодження та другий комутатор з'єднаний з першим та другим блоками нормалізаторів, вихід блока узгодження через блок контролю вхідних ланцюгів також з'єднаний з другим комутатором та двома операційними блоками, останній вхід другого комутатора з'єднаний з виходом блока еталонів, другий блок нормалізаторів через третій комутатор та другий аналого-цифровий перетворювач з'єднаний з входом другого операційного блока, входи блока конденсаторів з'єднані з другими входами системи, при цьому один його вхід з'єднаний з виходом джерела напруги, а другий - з входом блока керованих узгоджуючих пристроїв, вихід якого через блок компараторів та блок одновібраторів з'єднаний з елементом ІЛІ та блоком елементів І, другий вхід блока компараторів з'єднаний з виходом джерела напруги, другий вихід блока одновібраторів з'єднаний з першим та другим операційними блоками, вихід блока конденсаторів через блок формувачів та блок комутацій частоти з'єднаний з першим та другим операційними блоками, другий ви хід блока формувачів через блок сигналізаторів та елемент ІЛІ з'єднаний з другим входом блока комутації частоти, останній вхід якого з'єднаний з генератором еталонної частоти, др угий вихід блока сигналізаторів через блок елементів І з'єднаний з першим та другим операційними блоками, вихід першого аналого-цифрового перетворювача з'єднаний з першим операційним блоком, останні виходи якого з'єднані з блоком контролю вхідних ланцюгів та входом другого операційного блока, останній вхід третього комутатора з'єднаний з другим операційним блоком, останні входи першого операційного блока та блока керованих узгоджуючи х пристроїв з'єднані з відповідними виходами другого операційного блока, вихід обчислювача є ви ходом системи. Введення в систему додаткових ознак, а саме - блока контролю вхідних ланцюгів, блока еталонів, другого комутатора, блока узгодження, другого блока нормалізаторів, третього комутатора, другого аналого-цифрового перетворювача, блока комутації частоти, блока керованих узгоджуючих пристроїв, джерела напруги, блока конденсаторів, блока компараторів, блока одновібраторів, блока сигналізаторів, генератора еталонної частоти, елемента ІЛІ та блока елементів І - дозволяє забезпечити: високу функціональну надійність системи, за допомогою поблокового резервування та забезпечення, за рахунок цього, накопичування повної інформації в кожному вимірювальному каналі, яка характеризує стан параметрів газотурбінного двигуна; високу завадостійкість та достовірність контролю параметрів за рахунок автоматичного контролю функціонування, з видачею контрольних кодів, при порушеннях вхідних ланцюгів (ланцюгів датчиків) системи. Як видно з вищевказаного, запропоноване технічне рішення має суттєві ознаки, які дозволяють забезпечити високу функціональну надійність системи, завадостійкість та достовірність контролю параметрів за допомогою поблокового резервування та забезпеченням, за рахунок цього, накопичування повної інформації в кожному вимірювальному каналі, яка характеризує стан параметрів газотурбінного двигуна та автоматичного контролю функціонування, з видачею контрольних кодів, при порушенні вхідних ланцюгів (ланцюгів да 2 39279 тчиків) системи та за рахунок цього розширити функціональні можливості системи. Принцип роботи системи пояснюється кресленням (фіг.). Система містить блок 1 нормалізаторів, перший комутатор 2, перший аналого-цифровий перетворювач 3, блок 4 узгодження, другий комутатор 5, блок 6 еталонів, блок 7 контролю вхідних ланцюгів, перший операційний блок 8, другий блок 9 нормалізаторів, третій комутатор 10, другий аналого-цифровий перетворювач 11, другий операційний блок 12, блок 13 конденсаторів, блок 14 керованих узгоджуючих пристроїв, джерело 15 напруги, блок 16 компараторів, блок 17 одновібраторів, блок 18 формувачів, блок 19 комутації частоти, генератор 20 еталонної частоти, блок 21 сигналізаторів, блок 22 елементів І, елемент 23 ІЛІ та обчислювач 24. Перший операційний блок 8 містить блок 25 сполучення, блок 26 сполучення, блок 27 сполучення, перетворювач 28 інтервал - код та процесор 29. Другий операційний блок 12 містить блок 30 сполучення, блок 31 сполучення, блок 32 сполучення, перетворювач 33 інтервал - код та процесор 34. Блок 1 нормалізаторів через комутатор 2, аналого-цифровий перетворювач 3 з'єднаний з операційним блоком 8, вхід блоку 1 нормалізаторів через комутатор 5 та блок 4 узгодження з'єднаний з першим входом системи, окрім того, ви хід блока 4 узгодження через блок 7 контролю вхідних ланцюгів з'єднаний з операційними блоками 8 та 12 та комутатором 5, третій вхід якого з'єднаний з блоком 6 еталонів, виходи операційного блока 8 підключені до комутатора 2, блока 7 контролю вхідних ланцюгів, операційного блока 12 та обчислювача 24, вихід якого є виходом системи, вихід комутатора 5 через другий блок 9 нормалізаторів, третій комутатор 10 та другий аналого-цифровий перетворювач 11 з'єднаний з операційним блоком 12, входи блока 13 конденсаторів з'єднані з другими входами системи, при цьому один його вхід з'єднаний з виходом джерела 15 напруги, а другий - з входом блока 14 керованих узгоджуючих пристроїв, вихід якого через блок 16 компараторів та блок 17 одновібраторів з'єднаний з елементом 23 ІЛІ та блоком 22 елементів І, другий вхід блока 16 компараторів з'єднаний з виходом джерела 15 напруги, другий ви хід блока 17 одновібраторів з'єднаний з першим та другим операційними блоками 8 та 12, вихід блока 13 конденсаторів через блок 18 формувачів та блок 19 комутації частоти з'єднаний з першим та другим операційними блоками 8 та 12, другий вихід блока 18 формувачів через блок 21 сигналізаторів та елемент 23 ІЛІ з'єднаний з другим входом блока 19 комутації частоти, останній вхід якого з'єднаний з генератором 20 еталонної частоти, др угий вихід блока 21 сигналізаторів через блок 22 елементів І з'єднаний з першим та другим операційними блоками 8 та 12, останні входи комутатора 10, операційного блока 8 та блока 14 керованих узгоджуючи х пристроїв з'єднані з відповідними виходами операційного блока 12. Процесор 29 операційного блока 8 виходами з'єднаний з комутатором 2, обчислювачем 24, бло ком 7 контролю вхідних ланцюгів, операційним блоком 12 та блоками 25, 26, 27 сполучення та перетворювачем 28 інтервал - код операційного блока 8, виходи блоків 25, 26 та 27 з'єднані між собою та підключені до входу процесора 29, вихід перетворювача 28 з'єднаний із входом блока 27 сполучено останній вихід блока 25 сполучення з'єднаний з виходом аналого-цифрового перетворювача 3, входи блока сполучення 26 з'єднані з виходами блока 7 контролю вхідних ланцюгів, блока 22 елементів І та блока 17 одновібраторів. Перетворювач 33 інтервал - код операційного блока 12 по входу з'єднаний з виходом блока 19 комутації частоти, а по виходу - з блоком 32 сполучення процесор 34 операційного блока 12 виходами з'єднаний з обчислювачем 24, комутатором 10, операційним блоком 8, блоком 14 керованих узгоджуючих пристроїв, блоками 30, 31, 32 сполучення та перетворювачем 33 інтервал - код, виходи блоків 30, 31 та 32 з'єднані між собою та підключені до входу процесора 34, останні входи блока 30 сполучення з'єднані з виходом аналогоцифрового перетворювача 11, блока 31 сполучення - з виходами блока 7 контролю вхідних ланцюгів, блока 17 одновібраторів та блока 22 елементів І. Джерелами інформації, що характеризують стан параметрів газотурбінного двигуна, для системи, можуть бути: датчики тиску, які контролюють величину тиску в масляних, паливних, газодинамічних та повітряних магістралях газотурбінного двигуна; датчики температури, які контролюють величину температури в масляних, паливних, газодинамічних та повітряних магістралях газотурбінного двигуна; потенціометричні датчики, які контролюють положення ручки управління двигуном (РУД); датчики обертів ротора високого тиску, ротора низького тиску, турбостартера, коробки літакових агрегатів і т.д. Блок 4 узгодження призначено для узгодження вихідних опорів датчиків, що забезпечують їх тарирувальні характеристики та може являти собою, наприклад, набір прецезійних резисторів, подільників напруги, перетворювачів перемінної напруги в постійну, резистивно-ємнісних фільтрів бортових завад і т.д. Блок 6 еталонів може бути наданий як набір еталонних джерел напруги та стр уму, еталонних резисторів і т.д. Комутатори 5 та блока 19 можуть бути реалізовані на базі стандартних одноканальних керованих ключів. Блок 7 контролю вхідних ланцюгів може бути реалізовано на базі стандартних компараторів для контролю стійких порушень вхідних ланцюгів та чекаючих одновібраторів для контролю наявності перемінних контактів у вхідних ланцюгах. В операційних блоках 8 та 12 стандартні однокристальні процесори 29 та 34 можуть використовувати як внутрішню, так і зовнішню пам'ять (на кресленні не показано). Блоки 25, 26 та 27 сполучення операційного блока 8 та блоки 30, 31 та 32 сполучення операційного блока 12 можуть бути реалізовані на стандартних мікросхемах з трьома станами. Блок 14 керованих узгоджуючи х пристроїв призначено для узгодження рівня напруги, що 3 39279 надходять з виходу датчика обертів із входом блока 16 компараторів та може бути наданий, наприклад, як набір послідовно з'єднаних подільників напруги з ємкісними фільтрами та перетворювачами перемінної напруги в постійну зі змінюваною величиною вихідної напруги. Блок 16 може бути реалізовано на базі стандартних компараторів. Блок 17 одновібраторів може бути реалізовано на базі стандартних чекаючих одновібраторів з заданою постійною часу та призначено для контролю наявності перемінних контактів в ланцюгах датчиків обертів. Процесори 29 та 34 операційних блоків 8 та 12 відповідно можуть бути реалізовані на базі стандартного однокристального процесора, який має, окрім обчислювальних функцій, ще функцію вимірювання часових інтервалів, а також функцію прийому кодових та бінарних сигналів. Для наочності та розуміння процесу перетворення, прийому кодових та бінарних сигналів операційні блоки 8 та 12 надані набором, який складається з процесора 29 (34), перетворювача 28 (33) інтервал - код і блоків 25 (30), 26 (31) та 27 (32) сполучення. Кількість каналів в блоці 4 узгодження, блоках 1 та 9 нормалізаторів, блоці 7 контролю вхідних ланцюгів та кількість каналів керованих ключів комутатора 5 відповідає кількості контрольованих аналогових параметрів, а відповідно і кількості контрольованих ланцюгів аналогових датчиків газотурбінного двигуна. Кількість каналів в блоці 14 керованих узгоджуючих пристроїв, блоці 16 компараторів, блоці 17 одновібраторів, блоці 18 формувачів, блоці 21 сигналізаторів, блоці 22 елементів І, блоці 19 комутації частоти, а також кількість пар конденсаторів в блоці 13 відповідає кількості контрольованих частотних параметрів, а, відповідно, і кількості контрольованих ланцюгів датчики обертів газотурбінного двигуна. Система працює наступним чином. При вмиканні напруги живлення операційні блоки 8 та 12 встановлюються в початковий стан і з інтервалом часу, який перебільшує перехідні процеси в системі, видають сигнали, що забезпечують проведення автоматичного контролю функціонування кожного каналу системи окремо. З виходу 8-1 операційного блока 8 до входу блока 7 надходить сигнал, який, незалежно від стану ланцюгів аналогових датчиків, встановлює його в режим, що імітує порушення вхідних ланцюгів, при цьому на його виході отримаємо сигнали, наприклад, у вигляді логічної "1", які надходять до входів комутатора 5, блока 26 сполучення операційного блока 8 та блока 31 сполучення операційного блока 12. Водночас з видачею сигналу по ланцюгу 8-1 операційний блок 8 по ланцюгу 8-2 видає до входу процесора 34 операційного блока 12 сигнал, який свідчить про проходження самоконтролю в першому вимірювальному каналі аналогових параметрів. Аналогічно з виходу 12-1 операційного блока 12 до входу блока 14 надходить сигнал, який, незалежно від стану ланцюгів частотних датчиків, змінює вихідні сигнали (напруги) блока 14 в сторону зменшення до рівня стійкого змінення вихідного стану компараторів блока 16, тобто до рівня на пруги, величина якої менше від величини напруги, яка надходить до другого входу компараторів блока 16 з виходу джерела 15 напруги. В разі змінення вихідного становища компараторів блока 16, на його виході отримаємо сигнали, наприклад, у вигляді логічного рівня "0", які переводять одновібратори блока 17 в режим, що імітує порушення ланцюгів частотних да тчиків, при цьому на його першому виході отримаємо сигнали, наприклад, у вигляді логічного рівня "0", які надходять до входів елемента 23 ІЛІ та блока 22 елементів І, а на другому виході блока 17 одновібраторів отримаємо сигнали, наприклад, у вигляді логічного рівня "1", які надходять до входів блока 3-1 сполучення операційного блока 12 та блока 26 сполучення операційного блока 8. Водночас з видачею сигналу по ланцюгу 12-1 операційний блок 12 по ланцюгу 12-2 видає до входу процесора 29 операційного блока 8 сигнал, який свідчить про проходження самоконтролю в другому вимірювальному каналі частотних датчиків. Сигнали з виходу 1 блока 17, у вигляді логічного рівня "0", забороняють проходження сигналів логічного рівня "1", з виходу 1 блока 21 сигналізаторів, через блок 22 елементів I до входу блоків 31 та 26 сполучення операцій них блоків 12 та 8 відповідно. При надходженні сигналу логічного рівня "0" з виходу 1 блока 17 через елемент 23 ІЛІ до входу блока 19 комутації частоти, останній відключає входи операційних блоків 12 та 8 від виходів блока 18 формувачів та підключає вихід генератора 20 еталонної частоти до входів перетворювачів 33 та 28 інтервал - код блоків 12 та 8 відповідно. При цьому еталонні частоти з виходу генератора 20 надходять до входів перетворювачів 33 та 28 інтервал - код операційних блоків 12 та 8 відповідно. Кількість входів перетворювачів 33 та 28 відповідають кількості контрольованих частотних параметрів газотурбінного двигуна. Далі роботу системи в режимі самоконтролю розглянемо у наступній послідовності. При надходженні сигналів у вигляді логічної "1" до входу комутатора 5, останній відключає входи блоків 1 та 9 нормалізаторів від виходів блока 4 та підключає виходи блока 6 еталонів до входів блоків 1 та 9. При цьому еталонні сигнали через комутатор 5 надходять до входів блоків 1 та 9 нормалізаторів і в результаті на їх вихода х встановлюються контрольні значення постійної напруги. Потім з виходу 29-1 процесора 29 операційного блока 8 до входу блока 25 сполучення блока 8 надходить сигнал, що дозволяє проходження двійкового коду з виходу аналого-цифрового перетворювача 3 до входу 29-2 процесора 29 блока 8. Після видачі сигналу по ланцюгу 29-1 з ви ходу 8-3 блока 8 до входу комутатора 2 надходять сигнали, наприклад, у вигляді двійкового коду паралельного або послідовного, які забезпечують почергово підключення контрольних значень напруги з виходу блока 1 через комутатор 2 до аналого-цифрового перетворювача 3, у якому постійна контрольна напруга перетворюється в двійковий контрольний код. Після кожного підключення контрольної напруги, а відповідно і після кожного її перетворювання перетворювачем 3 з інтервалом часу, що перевищує перехідні процесори в комутаторі 2 та 4 39279 аналого-цифровому перетворювачі 3 процесор 29 блока 8 через блок 25 сполучення блока 8 по входу 29-2 записує до своєї пам'яті значення контрольного коду (при відсутності у вимірювальному тракті відмов). Після перетворювання контрольних сигналів з виходу блока 1 та запису контрольних кодів до пам'яті процесора 29 блока 8 знімається сигнал з виходу 29-1 процесора 29 блока 8. Із заданим інтервалом часу, після зняття сигналу з виходу 29-1 процесора 29 блока 8 та припинення надання кодових комбінацій по ланцюгу 8-3 до комутатора 2, видається сигнал по ланцюгу 29-3 до входу блока 29 сполучення блока 8, що дозволяє проходження через нього сигналів у вигляді логічної "1" до входу 29-2 процесора 29 операційного блока 8. Водночас з вищеописаним алгоритмом проведення контролю функціонування вимірювального каналу сигналів аналогових датчиків, а саме - після видачі блоком 8 сигналу по ланцюгу 8-2 до входу процесора 34 блока 12 з інтервалом часу, що перевищує перехідні процеси пов'язані з отриманням контрольних рівнів напруги на виході нормалізаторів блока 9 здійснюється контроль функціонування другого вимірювального каналу сигналів частотних датчиків. З ви ходу 34-1 процесора 34 операційного блока 12 до входу блока 30 сполучення блока 12 надходить сигнал, дозволяючий проходження двійкового коду з виходу аналогоцифрового перетворювача 11 до входу 34-2 процесора 34 блока 12. Після видачі сигналу по ланцюгу 34-1 з виходу 12-3 блока 12 до входу комутатора 10 надходять сигнали, наприклад, у вигляді двійкового коду паралельного або послідовного, які забезпечують почергово підключення контрольних значень напруги з виходу блока 9 через комутатор 10 до аналого-цифрового перетворювача 11, у якому постійна контрольна напруга перетворюється на двійковий контрольний код. Після кожного підключення контрольної напруги, а, відповідно, і після кожного її перетворювання перетворювачем 11 з інтервалом часу, що перевищує перехідні процеси в комутаторі 10 та аналогоцифровому перетворювачі 11 процесор 34 блока 12 через блок 30 сполучення блока 12 по входу 34-2 записує до своєї пам'яті значення контрольного коду (при відсутності відмов у вимірювальному каналі). Після перетворення контрольних сигналів з виходу блока 9 та запису контрольних кодів до пам'яті процесора 34 блока 12 знімається сигнал з виходу 34-1 процесора 34 блока 12. Із заданим інтервалом часу, після зняття сигналу з виходу 34-1 процесора 34 блока 12 та припинення подачі кодових комбінацій по ланцюгу 12-3 до комутатора 10, видається сигнал по ланцюгу 34-3 до входу блока 41 сполучення блока 12, що дозволяє проходження через нього сигналів у вигляді логічної "1" до входу 34-2 процесора 34 операційного блока 12. Після запису до пам'яті процесора 29 блока 8 та процесора 34 блока 12 сигналів з виходу блока 7 контролю вхідних ланцюгів та виходу 2 блока 17 одновібраторів процесор 29 блока 8 з виходу 29-3 та процесор 34 блока 12 з виходу 34-3 знімає сигнал та забороняє функціонування блока 26 блока 8 та блока 31 блока 12 відповідно, а зняття сигналу з ви ходу 8-1 блока 8 призводить до пере воду блока 7 в режим контролю ланцюгів аналогових датчиків. При наявності на виході блока 7, а, відповідно, і на вході комутатора 5, сигналів у вигляді логічного рівня "0", після зняття сигналу з виходу 8-1 блока 8, комутатор 5 відключає блок 6 еталонів та підключає блок 4 до нормалізаторів блоків 1 і 9. Потім з виходу 29-4 процесора 29 операційного блока 8 до входу блока 27 сполучення блока 8 надходить сигнал, що дозволяє проходження двійкового коду з виходу перетворювача 28 інтервал код операційного блока 8 до входу 29-2 процесора 29 блока 8. Після видачі сигналу по ланцюгу 294 з виходу 29-5 процесора 29 до входу перетворювача 28 інтервал - код блока 8 надходять сигнали, які забезпечують почергово підключення для перетворення еталонних частот, що надходять з виходу генератора 20 через блок 19 комутації частоти, в перетворювачі 28 на контрольний двійковий код. Перетворювач 28 інтервал - код має внутрішній комутатор для комутації вхідних частот. Після кожного підключення вхідної частоти, а, відповідно, і після кожного її перетворення перетворювачем 28 з інтервалом часу, що перевищує цикл перетворення періоду вхідної частоти процесор 29 блока 8 через блок 27 сполучення по входу 29-2 записує до своєї пам'яті значення контрольного коду. Після перетворення еталонних частот та запису контрольних кодів до пам'яті процесора 29 блока 8 припиняється подач а сигналів по ланцюгу 29-5 та знімається сигнал з виходу 29-4 процесора 29, що забороняє функціонування блока 27 сполучення блока 8. Водночас з проведенням контролю функціонування перетворювача 28 вимірювального каналу сигналів аналогових датчиків продовжується контроль функціонування вимірювального каналу сигналів частотних датчиків, а саме - з виходу 34-4 процесора 34 операційного блока 12 до входу блока 32 сполучення блока 12 надходить сигнал, що дозволяє проходження двійкового коду з виходу перетворювача 33 інтервал-код операційного блока 12 до входу 34-2 процесора 34 блока 12. Після видачі сигналу по ланцюгу 34-4 з виходу 34-5 процесора 34 до входу перетворювача 33 інтервал код блока 12 надходять сигнали, які забезпечують почергове підключення для перетворення еталонних частот, що надходять з виходу генератора 20 через блок 19 комутації частоти, в перетворювачі 33 на контрольний двійковий код. Перетворювач 33 інтервал – код, так само, як і перетворювач 28 блока 8, має внутрішній комутатор для комутації вхідних частот. Після кожного підключення вхідної частоти, а, відповідно, і після кожного її перетворення перетворювачем 33 з інтервалом часу, що перевищує цикл перетворення періоду вхідної частоти процесор 34 блока 12 через блок 32 сполучення по входу 34-2 записує до своєї пам'яті значення контрольного коду. Після перетворення еталонних частот та запису контрольних кодів до пам'яті процесора 34 блока 12 припиняється подача сигналів по ланцюгу 34-5 та знімається сигнал з виходу 34-4 процесора 34, що забороняє функціонування блока 32 сполучення блока 12. Потім з виходу 12-1 знімається сигнал і блок 14 керованих узгоджуючи х пристроїв переходить в режим контролю вхідних ланцюгів частотних датчиків, що, в 5 39279 свою чергу, забезпечує повернення компараторів блока 16 до первісного стану. Повернення компараторів блока 16 до первісного стану призводить також повернення до первісного стану і одновібраторів блока 17, при цьому з виходу 1 знімається сигнал у вигляді логічної "1", а з ви ходу 2 - сигнал у вигляді логічного рівня "0". У зв'язку з тим, що контроль проводиться перед запуском газотурбінного двигуна сигнали з частотних датчиків не надходять, тоді на виході формувачів блока 18 імпульси відсутні, а відповідно не надходять до блока 21 сигналізаторів та блока 19 комутації частоти. Відсутність імпульсів на вході блока 21 призводить до появи на виході 2 сигналу логічного рівня "0", а на виході 1 - сигналу логічного рівня "1". Наявність сигналу логічного рівня "1" з виходу 1 блока 17 одновібраторів на вході блока 22 елементів І дозволяє проходження через нього сигналу логічного рівня "1" з виходу 1 блока 21 сигналізаторів, який свідчить про відсутність частотних сигналів з датчиків обертів, до входів блоків 31 та 26 для реєстрації в пам'яті процесорів 34 та 29 операційних блоків 12 та 8 відповідно при проведенні режиму самоконтролю. Сигнали логічного рівня "0" з виходу 2 блока 21 сигналізаторів надходять через елемент 23 ІЛІ до входу блока 19 комутації частоти, що забезпечує підключення еталонних частот генератора 20 до входу перетворювачів 33 та 28 блоків 12 та 8 відповідно. Цей режим контролю здійснюється після зняття сигналу з виходу 12-2 і видачі сигналу по ланцюгу 12-4 операційного блока 12 до входу процесора 29 операційного блока 8. Зняття сигналу по ланцюгу 12-2, а відповідно і видача сигналу по ланцюгу 12-4 здійснюється після зняття сигналу по ланцюгу 12-1 операційного блока 12 з інтервалом часу, що перевищують час перехідних процесів, пов'язаних з поверненням блоків 14, 16 та 17 до режиму контролю порушення ланцюгів частотних да тчиків. Після видачі сигналу по ланцюгу 12-4 і надходження його до входу процесора 29 операційні блоки 8 та 12 переходять до режиму продовження самоконтролю. При цьому процесори 29 та 34 по ланцюгах 29-3 та 34-3 видають до блоків 26 та 31 відповідно сигнали, які дозволяють запис до пам'яті процесорів 29 та 34 сигналів з виходу блока 22 елементів І. Із заданим інтервалом часу після видачі сигналів по ланцюгах 29-3 та 34-3 процесори 29 та 34 по входах 29-2 та 34-2 відповідно реєструють у своїй пам'яті сигнали у вигляді логічного рівня "1", які свідчать про відсутність сигналів з датчиків обертів. Після завершення запису до пам'яті процесорів 29 та 34 сигналів операційних блоків 8 та 12 з виходу блока 22 знімаються сигнали з виходів 29-3 та 34-3 і видаються сигнали з виходів 29-4 та 34-4 процесорів 29 та 34 до блоків 27 та 32 сполучення операційних блоків 8 та 12 відповідно. Далі цикл перетворення еталонних частот, що надходять з виходу блока 19, у двійковий код із записом до пам'яті процесорів 29 та 34 здійснюється за описаним вище алгоритмом. Після перетворення еталонних частот та запису контрольних кодів до пам'яті процесорів 29 та 34 операційних блоків 8 та 12 відповідно знімається сигнал з виходу 12-4 операційного блока 12. Потім процесори 29 та 34 операційних блоків 8 та 12 відповідно починають аналізувати раніше записану до пам'яті контрольну інформацію і, якщо вона відповідає заданим контрольним параметрам, процесори 29 та 34, а відповідно і операційні блоки 8 та 12 видають сигнал справності, якщо вона не відповідає заданим контрольним параметрам, тоді процесори 29 та 34, а, відповідно, і операційні блоки 8 та 12 видають сигнали несправності до обчислювача 24. Наявність сигналу несправності у деякому з каналів потребує ремонту системи. Після завершення аналізу контрольної інформації операційними блоками 8 та 12 і видачі сигналів справності, система переходить до режиму вимірювання сигналів з датчиків, що характеризують стан параметрів газотурбінного двигуна. Контроль функціонування системи може здійснюватись також за запитами, наприклад, як з місця бортінжера, так і автоматичної системи контролю параметрів літака за описаним вище алгоритмом. При відсутності порушень ланцюгів аналогових датчиків системи з виходу блока 7 до входу комутатора 5 надходять сигнали у вигляді логічного рівня "0", які підключають виходи блока 4 до нормалізаторів блоків 1 та 9. Сигнали від аналогових датчиків контрольованих параметрів газотурб иного двигуна (на кресленні не показані) надходять до блока 4 узгодження, де здійснюється узгодження вихідних характеристик датчиків із входами блока 7 та через комутатор 5 - із входами блоків 1 та 9 нормалізаторів. Кількість каналів в блоці 4 відповідає кількості датчиків, що підключаються до його входу. З ви ходу блока 4 узгодження сигнали, величини яких пропорційні сигналам з датчиків (порушення вхідних ланцюгів відсутнє), надходять до блока 7 з виходу якого до входів блока 26 сполучення блока 8, блока 31 сполучення блока 12 та комутатора 5 надходять сигнали логічного рівня "0", які свідчать про відсутність порушення вхідних ланцюгів. Окрім того, сигнали з виходу блока 4 через комутатор 5 надходять також до блоків 1 та 9 нормалізаторів, де нормалізуються у постійну напругу, зручну для перетворення у цифрову форму. Кількість нормалізаторів у блоках 1 та 9 відповідає кількості контрольованих параметрів. Величини напруг на виходах блоків 1 та 9 змінюються пропорційно зміненню контрольованих параметрів. Процес вимірювання, обробки та видачі інформації про стан параметрів газотурбінного двигуна здійснюється у наступному порядку. З виходу 29-1 процесора 29 операційного блока 8 до входу блока 25 сполучення блока 8 надходить сигнал, дозволяючий проходження двійкового коду з виходу аналого-цифрового перетворювача 3 до входу 29-2 процесора 29 блока 8. Після видачі сигналу по ланцюгу 29-1 з виходу 8-3 блока 8 до входу комутатора 2 надходять сигнали, які забезпечують почергове підключення нормалізованих напруг з виходу блока 1 через комутатор 2 до аналого-цифрового перетворювача 3, в якому постійна напруга перетворюється на двійковий код, величина якого пропорційна значенню контрольованого параметра. Після кожного підключення нормалізованої напруги, а відповідно і після кожного її перетворення перетворювачем 3 з інтервалом часу, що перещує перехідні процеси в комутаторі 2 та аналого-цифровому перетворю-вачі 3 процесор 29 блока 8 через блок 25 спо 6 39279 лучення блока 8 по входу 29-2 записує до своєї пам'яті значення двійкового коду, що характеризуює фізичний стан параметрів газотурбінного двигуна. Після завершення перетворення сигналів з блока 1 та запису результатів перетворення до пам'яті процесора 29 блока 8 знімається сигнал з виходу 29-1 процесора 29 блока 8 та припинення подачі кодових комбінацій по ланцюгу 8-3 з блока 8 до комутатора 2, видається сигнал по ланцюгу 29-3 до входу блока 26 сполучення блока 8, дозволяючий проходження через нього сигналів у вигляді логічної "1" (при порушеннях ланцюгів датчиків) з виходів блоків 7, 17 та 22 до входу 29-2 процесора 29 блока 8. Після запису сигналів через блок 26 до процесора 29 блока 8 знімається сигнал з виходу 29-3 та видається сигнал з виходу 29-4 процесора 29 до входу блока 27 сполучення блока 8, що дозволяє проходження двійкового коду з виходу перетворювача 28 до входу 29-2 процесора 29 блока 8. В результаті функціонування блока 8 за описаним вище алгоритмом, при проведенні самоконтролю, будуть перетворюватись періоди, присутніх на вході перетворювача 28 з виходу блока. 19, імпульсних послідовностей у двійковий код, який фіксується у пам'яті процесора 29 блока 8 та характеризуючий фізичний стан обертання різних частин газотурбінного двигуна. Після запису до пам'я ті процесора 29 блока 8 двійкового коду з виходу блока 27 процесора 29, а, відповідно, і блок 8 формує кадр, який складається з інформації, що характеризує стан параметрів газотурбінного двигуна та ланцюгів датчиків системи і видає до входу обчислювача 24, наприклад, у вигляді послідовного адресного коду для обробки за завданими алгоритмами, наприклад, контроль за перевищенням завданого значення (аварійного, попереджувального) параметра (допусковий контроль параметрів) та цикл вимірювання і перетворення сигналів блоком 8, що характеризують стан параметрів газотурбінного двигуна, повторюється. Водночас з функціонуванням вимірювального каналу аналогових параметрів з операційним блоком 8 по вимірюванню параметрів газотурбінного двигуна функціонує і вимірювальний канал частотних параметрів з операційним блоком 12 у наступному порядку. Сигнали від частотних датчиків контрольованих параметрів (на кресленні не показані) у вигляді перемінної напруги, періоди проходження яких пропорційні числам обертів частин газотурбінного двигуна, що обертаються, надходять через блок 13 конденсаторів до блока 18 формувачів, де і перетворюються в імпульси прямокутної форми. З блоку 18 формувачів прямокутні імпульси надходять до блока 19 комутації частоти та блока 21 сигналізаторів. При наявності імпульсів сигналізатори блока 21 сигналами у вигляді логічної "1" з виходу 2 через елемент 10 ІЛІ, впливаючи на комутатори блока 19 комутації частоти, дозволяють проходження прямокутних імпульсів з виходу блока 18 формувачів до входу перетворювача 33 інтервал-код блока 12 та перетворювача 28 інтервал - код блока 29. Сигналізатори блока 21 призначені для контролю працездатності вхідного ланцюга частотних датчиків системи при працюючому газотурбінному двигуні. При короткому зами канні в ланцюгах частотних датчиків або відмові одного з каналів у блоці 13 чи 18 на відповідному вході блока 21 прямокутні імпульси зникають, що тягне за собою видачу по виходу 1, сигналу логічного рівня "1", а по виходу 2 - сигналу логічного рівня "0". Сигнал логічного рівня "0", впливаючи через елемент 23 на відповідний комутатор блока 19, відключає вихід відповідного формувача блока 18 та підключає до відповідного входу перетворювача 33 блока 12 і перетворювача 28 блока 8 генератор 20 еталонної частоти. Внаслідок підключення контрольної частоти до відповідного входу перетворювачів 33 та 28 у пам'яті процесорів 34 та 29 відповідно буде зареєстрований контрольний код. Окрім того, сигнал логічного рівня "1" через блок 22 елементів І, на другому вході якого присутній сигнал логічного рівня "1" так як відсутній обрив ланцюга відповідного датчика обертів буде також зареєстрований в пам'яті процесора 34 блока 12 та процесора 29 блока 8. При відсутності відмов у ланцюгах частотних датчиків на вході перетворювачів 33 та 28 блоків 12 та 8 відповідно присутні послідовності прямокутних імпульсів, періоди яких пропорційні числу обертів частин газотурбінного двигуна, що обертаються. Внаслідок функціонування операційного блока 12 за описаним вище алгоритмом, при проведенні самоконтролю будуть перетворюватися аналогові сигнали, які надходять з виходу блока 9 через комутатор 10 та перетворювач 11 до входу блока 30 блока 12, у двійковий код, імпульсні послідовності, які надходять з виходу блока 19, у двійковий код, а також сигнали, які свідчать про порушення в ланцюгах аналогових та частотних датчиків і відмовах у блоках 13 та 18, з виходів блоків 7, 17 та 22, які фіксуються у пам'яті процесора 34 операційного блока 12. Після проведення циклу реєстрації у пам'яті процесора 34 операційного блока 12 результатів перетворення вхідних аналогових та частотних сигналів, а також стан вхідних ланцюгів і відмов у блоках 13 та 18 процесор 34, а відповідно і блок 12 формує кадр, що має інформацію, що характеризує технічний стан газотурбінного двигуна, ланцюги його датчиків та технічний стан самої системи і видає до входу обчислювача 24, наприклад, у вигляді послідовного двійкового адресного коду, і цикл вимірювання параметрів повторюється. При справних ланцюгах датчиків струм від джерела 15 обтікає ланцюг датчиків та видає високий рівень постійної напруги (з незначними пульсаціями від перемінної напруги датчиків обертів) на виході блока 14 керованих узгоджуючих пристроїв. Цей рівень напруги передається до входу компараторів блока 16 і, так як він перевищує величину опорної напруги, що надходить до другого його входу з виходу джерела 15, тоді на виході блока 16 присутній сигнал логічного рівня "І", який не змінює вихідного становища одновібраторів блока 17. Струми, які протікають по ланцюгам датчиків, не впливають на роботу формувачів блока 18 у зв'язку із наявністю між ними розділительних конденсаторів блока 13. При наявності несправності типу "обрив" у ланцюгу будь-якого датчика обертів відбудеться зникнення напруги на виході відповідного керованого узгоджуючого пристрою блока 14, що призведе до 7 39279 змінення вихідного становища відповідного компаратора блока 16, а, відповідно, і появі на його виході логічного рівня "0". Сигнал логічного рівня "0", з виходу блока 16, збуджує відповідний одновібратор блока 17, внаслідок на виході 1 з'являється сигнал логічного рівня "0", а на виході 2 - сигнал логічного рівня "1". Сигнал з виходу 1 блока 17 забороняє проходження сигналу логічного рівня "1" з виходу 1 блока 21 через блок 22 елементів І у зв'язку з відсутністю на одному з виходів блока 21 імпульсної послідовності, так як порушений ланцюг одного з датчиків обертів. Окрім того, сигнал логічного рівня "0" з виходу 1 блока 17 через елемент 23 ІЛІ, впливаючи на відповідний комутатор блока 19, відключає формувач блока 18 несправного ланцюга датчика та підключає еталонну частоту генератора 20 до входу перетворювача 33 блока 12 та перетворювача 28 блока 8. Внаслідок перетворення контрольної частоти у пам'яті процесора 34 блока 12 фіксується контрольний код, що свідчить про справність вимірювального каналу та несправність ланцюга відповідного датчика обертів. Відсутність контрольного коду по каналу порушення ланцюга датчика обертів свідчить про відмову вимірювального каналу, а отримана інформація по даному каналу з обробки знімається і фіксується відмова системи. Сигнал логічного рівня "1" з виходу 2 блока 17 надходить до операційних блоків 12 та 8 і реєструється у пам'яті процесорів 34 та 29, що свідчить про наявність несправності у ланцюгу датчика обертів. При наявності несправності типу "перемінний контакт" відбудеться зникнення напруги на виході відповідного пристрою блока 14 під час порушення ланцюга датчика обертів. Напруга на другому вході відповідного компаратора блока 16, яка надходить від джерела 15, за величиною більша, ніж напруга, яка надходить з виходу відповідного узгоджуючого пристрою блока 14 під час порушення ланцюга датчика обертів. Відповідно на виході відповідного компаратора блока 16 отримаємо сигнал логічного рівня "0", збуджуючий відповідний одновібратор блока 17, внаслідок чого, як оговорювалося вище, при порушенні ланцюга датчика обертів, на виході 1 блока 17 отримаємо сигнал логічного рівня "0", а на виході 2 - сигнал логічного рівня "1", який свідчить про порушення ланцюга датчика обертів. Причому сигнали на виходах 1 та 2 блока 17, в режимі збудження одновібраторів, утримуються на величину часу, рівн у постійній часу одновібраторів. Постійна часу одновібраторів блока 17 обирається з розрахунку максимально можливого інтервалу між порушеннями ланцюга датчика обертів, але не менш як 2-3 періоди частоти вхідного сигналу. Це необхідно для того, щоб після закінчення порушення ланцюга датчика обертів виключити реєстрацію інформації, по каналу порушення вхідного ланцюга, у пам'яті процесорів 34 та 29 блоків 12 та 8 відповідно. При віднов ленні ланцюга датчика обертів напруга на виході відповідного узгоджуючого пристрою блока 14 відновлюється до номінального рівня, що перевищує рівень напруги з джерела 15, внаслідок чого на виході відповідного компаратора блока 16 сигнал логічного рівня "0" зникає і з'являється сигнал логічного рівня "1". Як що відбуде ться повторне порушення ланцюга датчика обертів відносно першого (при перемінному контакті в ланцюгу датчика обертів) та на виході відповідного компаратора блока 16 повторно з'явиться сигнал логічного рівня "0", при чому за часом менш ніж постійна часу одновібраторів блока 17, стан збудженого одновібратора блока 17 не зміниться і буде реєстр уватися сигнал порушення ланцюга датчика обертів у пам'яті процесорів 34 та 29 блоків 12 та 8 відповідно. Інформація у ви гляді послідовного двійкового адресного коду, що характеризує те хнічний стан газотурбінного двигуна, ланцюгів датчиків і те хнічний стан самої системи надходить до обчислювача 24 з виходу поопераційного блока 8 по одному ланцюгу і з виходу операційного блока 12 по другому. Обчислювач 24 контролює інформацію, що надходить, наприклад, за структурою кадрів, що надходять, інтервалами між кадрами і т.д. та може обирати той чи інший вхід для використання інформації, що надходить, а також за результатами контролю вхідної інформації формує сигнал справності каналів системи. Обчислювач за своєю структурою може бути як одноканальним, так і багатоканальним (резервованим) залежно від вимог по надійності, що висуваються. У обчислювачі 24 отримана інформація обробляється за завданими алгоритмами, наприклад, здійснюється допусковий контроль параметрів та формування керованих команд на вмикання (вимикання) різних агрегатів газотурбінного двигуна. Окрім того, отримана інформація може реєструватися, наприклад, на експлуатаційному накопичувані обчислювача 24 для формування банку даних з метою її використання при експлуатації газотурбінного двигуна за технічним станом. Запропоноване технічне рішення дозволяє забезпечити: високу функціональну надійність системи, використовуючи поблокове резервування та забезпечення, за рахунок цього, накопичування повної інформації у кожному вимірювальному каналі, що характеризує стан параметрів та ланцюгів датчиків газотурбінного двигуна і технічний стан вимірювальних каналів; високу завадостійкість та достовірність контролю параметрів за рахунок автоматичного контролю функціонування, з видачею контрольних кодів, при порушеннях вхідних ланцюгів (ланцюгів датчиків) системи. Як видно з вищевказаного, запропоноване технічне рішення має високу функціональну надійність, достовірність контролю параметрів, завадостійкість та розширені функціональні можливості. 8 Фіг. 39279 9 39279 __________________________________________________________ ДП “Український інститут промислової власності (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2001 р. Формат 60х84 1/8. Обсяг ______ обл.-вид.арк. Тираж 50 прим. Зам._______ ____________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 ___________________________________________________________ 10

ДивитисяДодаткова інформація

Назва патенту англійськоюSystem for automated control of parameters of gas-turbine engine

Автори англійськоюBezschastnyi Vasyl Oleksiiovych

Назва патенту російськоюСистема автоматического контроля параметров газотурбинного двигателя

Автори російськоюБессчастный Василий Алексеевич

МПК / Мітки

МПК: F02C 9/28

Мітки: контролю, газотурбінного, двигуна, автоматичного, система, параметрів

Код посилання

<a href="https://ua.patents.su/10-39279-sistema-avtomatichnogo-kontrolyu-parametriv-gazoturbinnogo-dviguna.html" target="_blank" rel="follow" title="База патентів України">Система автоматичного контролю параметрів газотурбінного двигуна</a>

Попередній патент: Пристрій для очистки трубопроводу

Наступний патент: Свердловинний заряд

Випадковий патент: Спосіб транссептального доступу до клиноподібної пазухи