Пристрій для визначення інтенсивності спекулярної складової кольору при формуванні шорстких поверхонь

Номер патенту: 60139

Опубліковано: 10.06.2011

Автори: Войтко Вікторія Володимирівна, Романюк Оксана Володимирівна, Романюк Олександр Никифорович

Формула / Реферат

Пристрій для визначення інтенсивності спекулярної складової кольору при формуванні шорстких поверхонь, що містить блок постійної пам'яті, чотири блоки множення, п'ять регістрів, два суматори, вихід другого блока множення підключено до першого виходу пристрою, вихід третього блока множення підключено до другого виходу пристрою, вихід четвертого блока множення підключено до третього виходу пристрою, керуючий вхід першого регістра підключено до першого керуючого входу пристрою, а інформаційний вхід підключено до першого інформаційного входу пристрою, керуючий вхід другого регістра підключено до другого керуючого входу пристрою, а інформаційний вхід підключено до другого інформаційного входу пристрою, керуючий вхід третього регістра підключено до третього керуючого входу пристрою, а інформаційний вхід підключено до третього інформаційного входу пристрою, а вихід з'єднано із другим входом другого блока множення, керуючий вхід четвертого регістра підключено до четвертого керуючого входу пристрою, а інформаційний вхід підключено до четвертого інформаційного входу пристрою, а вихід з'єднано із другим входом третього блока множення, керуючий вхід п'ятого регістра підключено до п'ятого керуючого входу пристрою, а інформаційний вхід підключено до п'ятого інформаційного входу пристрою, а вихід з'єднано із другим входом четвертого блока множення, який відрізняється тим, що у нього введено чотири мультиплексори, п'ять регістрів, суматор, блок керування, тригер, інформаційний вхід якого підключено до сьомого інформаційного входу пристрою, керуючий вхід якого підключено до сьомого керуючого входу пристрою, а вихід - до керуючих входів першого суматора та четвертого мультиплексора, інформаційний вхід шостого регістра підключено до шостого інформаційного входу пристрою, керуючий вхід якого підключено до шостого керуючого входу пристрою, а вихід - до першого інформаційного входу другого мультиплексора та другого інформаційного входу третього мультиплексора, вихід сьомого регістра підключено до другого інформаційного входу другого мультиплексора, вихід восьмого регістра підключено до першого інформаційного входу першого суматора, інверсний вихід дев'ятого регістра підключено до першого інформаційного входу четвертого мультиплексора, вихід якого підключено до другого інформаційного входу першого суматора, вихід якого підключено до третього інформаційного входу першого мультиплексора, вихід десятого регістра підключено до перших входів другого, третього та четвертого блоків множення та до інформаційного входу другого суматора, керуючий вхід якого підключено до рівня логічної одиниці, а вихід - до четвертих інформаційних входів першого та другого мультиплексорів, інформаційні входи восьмого, дев'ятого та десятого регістрів підключено до виходу першого блока множення, перший інформаційний вхід якого підключено до виходу першого мультиплексора, а другий - до виходу другого мультиплексора, перший інформаційний вхід третього суматора підключено до прямого виходу дев'ятого регістра, другий інформаційний вхід підключено до рівня логічної одиниці, вхід переносу - до рівня логічного нуля, а вихід з'єднано з другим інформаційним входом четвертого мультиплексора, вихід першого регістра підключено до першого входу першого мультиплексора та першого інформаційного входу третього мультиплексора, вихід якого підключено до входу блока постійної пам'яті, вихід якого підключено до інформаційного входу сьомого регістра та другого інформаційного входу першого мультиплексора, кожний (і+1)-й розряд виходу другого регістра підключено до і-го розряду третього інформаційного входу другого мультиплексора, перший вхід блока керування з'єднано з входом початкової установки, а другий - з входом "Пуск", перший вихід підключено до виходу ознаки достовірності, другий вихід - до виходу "Кінець", третій вихід - до перших керуючих входів першого та другого мультиплексорів, четвертий вихід - до других керуючих входів першого та другого мультиплексорів, п'ятий вихід - до керуючого входу третього мультиплексора, шостий вихід - до керуючого входу сьомого регістра, сьомий вихід - до керуючого входу восьмого регістра, восьмий вихід - до керуючого входу дев'ятого регістра, дев'ятий вихід - до керуючого входу десятого регістра, крім цього блок керування містить два елементи І, генератор імпульсів, два D-тригера, лічильник та блок постійної пам'яті, перший вхід блока керування підключено до першого входу першого елемента І, другий вхід якого з'єднано з дев'ятим виходом блока постійної пам'яті, вихід першого елемента І підключено до входів обнулення першого та другого D-тригерів та до входу обнулення лічильника, другий вхід блока керування з'єднано з входом синхронізації першого D-тригера, інформаційний вхід якого підключено до рівня логічної одиниці, а вихід якого підключено до інформаційного входу другого D-тригера, вхід синхронізації якого з'єднано з інверсним виходом генератора імпульсів, прямий вихід якого підключено до першого входу другого елемента І, другий вхід якого з'єднано з виходом другого D-тригера, а вихід підключено до входу синхронізації лічильника, виходи якого підключено до входів блока постійної пам'яті, перший вихід якого підключено до третього виходу, другий - до четвертого виходу, третій - до п'ятого виходу, четвертий - до шостого виходу, п'ятий - до сьомого виходу, шостий - до восьмого виходу, сьомий - до дев'ятого виходу, восьмий - до першого виходу та дев'ятий - до другого виходу блока керування.

Текст

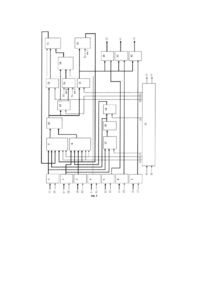

Пристрій для визначення інтенсивності спекулярної складової кольору при формуванні шорстких поверхонь, що містить блок постійної пам'яті, чотири блоки множення, п'ять регістрів, два суматори, вихід другого блока множення підключено до першого виходу пристрою, вихід третього блока множення підключено до другого виходу пристрою, вихід четвертого блока множення підключено до третього виходу пристрою, керуючий вхід першого регістра підключено до першого керуючого входу пристрою, а інформаційний вхід підключено до першого інформаційного входу пристрою, керуючий вхід другого регістра підключено до другого керуючого входу пристрою, а інформаційний вхід підключено до другого інформаційного входу пристрою, керуючий вхід третього регістра підключено до третього керуючого входу пристрою, а інформаційний вхід підключено до третього інформаційного входу пристрою, а вихід з'єднано із другим входом другого блока множення, керуючий вхід четвертого регістра підключено до четвертого керуючого входу пристрою, а інформаційний вхід підключено до четвертого інформаційного входу пристрою, а вихід з'єднано із другим входом третього блока множення, керуючий вхід п'ятого регістра підключено до п'ятого керуючого входу пристрою, а інформаційний вхід підключено до п'ятого інформаційного входу пристрою, а вихід з'єднано із другим входом четвертого блока множення, який відрізняється тим, що у нього введено чотири мультиплексори, п'ять регістрів, суматор, блок керування, тригер, інформаційний вхід якого підключено до сьомого інформаційного входу пристрою, керуючий вхід якого підключено до сьомого керуючого входу пристрою, а вихід - до керуючих входів першого суматора та четвертого мультиплексора, інформаційний вхід шостого регістра підключено до шостого інформаційного входу при 2 (19) 1 3 60139 4 до керуючого входу третього мультиплексора, шостий вихід - до керуючого входу сьомого регістра, сьомий вихід - до керуючого входу восьмого регістра, восьмий вихід - до керуючого входу дев'ятого регістра, дев'ятий вихід - до керуючого входу десятого регістра, крім цього блок керування містить два елементи І, генератор імпульсів, два Dтригера, лічильник та блок постійної пам'яті, перший вхід блока керування підключено до першого входу першого елемента І, другий вхід якого з'єднано з дев'ятим виходом блока постійної пам'яті, вихід першого елемента І підключено до входів обнулення першого та другого D-тригерів та до входу обнулення лічильника, другий вхід блока керування з'єднано з входом синхронізації першого D-тригера, інформаційний вхід якого підключено до рівня логічної одиниці, а вихід якого підключено до інформаційного входу другого D-тригера, вхід синхронізації якого з'єднано з інверсним виходом генератора імпульсів, прямий вихід якого підключено до першого входу другого елемента І, другий вхід якого з'єднано з виходом другого D-тригера, а вихід підключено до входу синхронізації лічильника, виходи якого підключено до входів блока постійної пам'яті, перший вихід якого підключено до третього виходу, другий - до четвертого виходу, третій - до п'ятого виходу, четвертий - до шостого виходу, п'ятий - до сьомого виходу, шостий - до восьмого виходу, сьомий - до дев'ятого виходу, восьмий - до першого виходу та дев'ятий - до другого виходу блока керування. Корисна модель відноситься до автоматики та обчислювальної техніки і призначена для формування в системах комп'ютерної графіки спекулярної (дзеркальної) складової кольору при формуванні реалістичних зображень шорстких поверхонь. Відомий пристрій для визначення інтенсивності спекулярної складової кольору, який містить блок постійної пам'яті, перший блок множення, перший вхід якого з'єднано із виходом блока постійної пам'яті та другий, третій та четвертий блоки множення, виходи яких підключено до першого, другого та третього виходів пристрою відповідно, перший регістр, вихід якого підключено до блока постійної пам'яті, керуючий вхід якого підключено до першого керуючого входу пристрою, а інформаційний вхід підключено до першого інформаційного входу пристрою, другий регістр, вихід якого підключено до обох входів п'ятого блока множення, до входу блока інверторів та до другого інформаційного входу другого суматора, керуючий вхід другого регістра підключено до другого керуючого входу пристрою, а інформаційний вхід підключено до другого інформаційного входу пристрою, п'ятий блок множення, обидва входи якого підключено до виходу другого регістра, а вихід з'єднано із першим інформаційним входом першого суматора, вихід блока інверторів з'єднано із другим інформаційним входом першого суматора, вхід переносу якого підключено до рівня логічної одиниці, а вихід до другого входу першого блока множення, до першого інформаційного входу другого суматора підключено вихід першого блока множення, керуючий вхід підключено до рівня логічного нуля, а вихід з'єднано із першими входами другого, третього та четвертого блоків множення, третій регістр, керуючий вхід якого підключено до третього керуючого входу пристрою, інформаційний вхід підключено до третього інформаційного входу пристрою, а вихід з'єднано із другим входом другого блока множення, четвертий регістр, керуючий вхід якого підключено до четвертого керуючого входу пристрою, інформаційний вхід підключено до четвертого інформаційного входу пристрою, а вихід з'єднано із другим входом третього блока множення, п'ятий регістр, керуючий вхід якого підключено до п'ятого керуючого входу пристрою, інформаційний вхід підключено до п'ятого інформаційного входу пристрою, а вихід з'єднано із другим входом четвертого блока множення. [Патент України на корисну модель № 20998 МПК G06T 15/50, опубл. у бюл. № 2, 2007 p.]. Недоліками пристрою є недостатня якість відтворення спекулярної складової кольору в зоні затухання, що обумовлює обмежену область застосування пристрою, оскільки він може використовуватись лише для певної групи поверхонь, наприклад, з високим показником коефіцієнта спекулярності. Найбільш близьким до технічного рішення, що заявляється, є пристрій для визначення інтенсивності спекулярної складової кольору, який містить блок постійної пам'яті, п'ять регістрів, п'ять блоків множення, вихід третього блока множення підключено до першого виходу пристрою, вихід четвертого блока множення підключено до другого виходу пристрою, вихід п'ятого блока множення підключено до третього виходу пристрою, керуючий вхід першого регістра підключено до першого керуючого входу пристрою, а інформаційний вхід підключено до першого інформаційного входу пристрою, вихід другого регістра підключено до блока постійної пам'яті, керуючий вхід якого підключено до другого керуючого входу пристрою, а інформаційний вхід підключено до другого інформаційного входу пристрою, керуючий вхід третього регістра підключено до третього керуючого входу пристрою, інформаційний вхід підключено до третього інформаційного входу пристрою, а вихід з'єднано із першим входом третього блока множення, керуючий вхід четвертого регістра підключено до четвертого керуючого входу пристрою, інформаційний вхід підключено до четвертого інформаційного входу пристрою, а вихід з'єднано із першим входом четвертого блока множення, керуючий вхід п'ятого регістра підключено до п'ятого керуючого входу пристрою, інформаційний вхід підключено до п'ятого інформаційного входу пристрою, а вихід 5 з'єднано із першим входом п'ятого блока множення, крім того містить два суматори, схему порівняння, блок ключів, перший вхід першого суматора з'єднано із виходом першого регістра, кожний розряд другого входу під'єднано до рівня логічної одиниці, а вхід переносу заземлено, перший вхід першого блока множення з'єднано із виходом першого суматора, другий вхід - із виходом другого регістра, перший вхід другого суматора підключено до виходу першого блока множення, другий вхід заземлено, а вхід переносу під'єднано до рівня логічної одиниці, обидва входи другого блока множення підключено до виходу другого суматора, перший і другий входи схеми порівняння з'єднано із виходом другого блока множення і виходом блока постійної пам'яті відповідно, до входів блока ключів підключено вихід другого блока множення та вихід схеми порівняння, а вихід підключено до других входів третього, четвертого та п'ятого блоків множення. [Патент України на корисну модель № 30041, (51) МПК (2006) G06T 15/50, опубл. 11.02.2008 р. у Бюл. № 3, 2008р.]. Недоліком пристрою є недостатня якість формування реалістичних зображень шорстких поверхонь. В основу корисної моделі поставлено задачу створення пристрою для визначення інтенсивності спекулярної складової кольору при формуванні шорстких поверхонь, у якому за рахунок введення нових блоків і зв'язків досягається підвищення реалістичності графічних зображень. Поставлена задача досягається тим, що в пристрій для визначення інтенсивності спекулярної складової кольору при формуванні шорстких поверхонь, який містить блок постійної пам'яті, чотири блоки множення, п'ять регістрів, два суматори, вихід другого блока множення підключено до першого виходу пристрою, вихід третього блока множення підключено до другого виходу пристрою, вихід четвертого блока множення підключено до третього виходу пристрою, керуючий вхід першого регістра підключено до першого керуючого входу пристрою, а інформаційний вхід підключено до першого інформаційного входу пристрою, керуючий вхід другого регістра підключено до другого керуючого входу пристрою, а інформаційний вхід підключено до другого інформаційного входу пристрою, керуючий вхід третього регістра підключено до третього керуючого входу пристрою, а інформаційний вхід підключено до третього інформаційного входу пристрою, а вихід з'єднано із другим входом другого блока множення, керуючий вхід четвертого регістра підключено до четвертого керуючого входу пристрою, а інформаційний вхід підключено до четвертого інформаційного входу пристрою, а вихід з'єднано із другим входом третього блока множення, керуючий вхід п'ятого регістра підключено до п'ятого керуючого входу пристрою, а інформаційний вхід підключено до п'ятого інформаційного входу пристрою, а вихід з'єднано із другим входом четвертого блока множення, введено чотири мультиплексори, п'ять регістрів, суматор, блок керування, тригер, інформаційний вхід якого підключено до сьомого інформаційного входу пристрою, керуючий вхід якого підключено 60139 6 до сьомого керуючого входу пристрою, а вихід - до керуючих входів першого суматора та четвертого мультиплексора, інформаційний вхід шостого регістра підключено до шостого інформаційного входу пристрою, керуючий вхід якого підключено до шостого керуючого входу пристрою, а вихід - до першого інформаційного входу другого мультиплексора та другого інформаційного входу третього мультиплексора, вихід сьомого регістра підключено до другого інформаційного входу другого мультиплексора, вихід восьмого регістра підключено до першого інформаційного входу першого суматора, інверсний вихід дев'ятого регістра підключено до першого інформаційного входу четвертого мультиплексора, вихід якого підключено до другого інформаційного входу першого суматора, вихід якого підключено до третього інформаційного входу першого мультиплексора, вихід десятого регістра підключено до перших входів другого, третього та четвертого блоків множення та до інформаційного входу другого суматора, керуючий вхід якого підключено до рівня логічної одиниці, а вихід - до четвертих інформаційних входів першого та другого мультиплексорів, інформаційні входи восьмого, дев'ятого та десятого регістрів підключено до виходу першого блока множення, перший інформаційний вхід якого підключено до виходу першого мультиплексора, а другий - до виходу другого мультиплексора, перший інформаційний вхід третього суматора підключено до прямого виходу дев'ятого регістра, другий Інформаційний вхід підключено до рівня логічної одиниці, вхід переносу - до рівня логічного нуля, а вихід з'єднано з другим інформаційним входом четвертого мультиплексора, вихід першого регістра підключено до першого входу першого мультиплексора та першого інформаційного входу третього мультиплексора, вихід якого підключено до входу блока постійної пам'яті, вихід якого підключено до інформаційного входу сьомого регістра та другого інформаційного входу першого мультиплексора, кожний і+1-й розряд виходу другого регістра підключено до і-го розряду третього інформаційного входу другого мультиплексора, перший вхід блока керування з'єднано з входом початкової установки, а другий - з входом «Пуск», перший вихід підключено до виходу ознаки достовірності, другий вихід - до виходу «Кінець», третій вихід - до перших керуючих входів першого та другого мультиплексорів, четвертий вихід - до других керуючих входів першого та другого мультиплексорів, п'ятий вихід до керуючого входу третього мультиплексора, шостий вихід - до керуючого входу сьомого регістра, сьомий вихід - до керуючого входу восьмого регістра, восьмий вихід - до керуючого входу дев'ятого регістра, дев'ятий вихід - до керуючого входу десятого регістра. На фігурі 1 зображено структурну схему пристрою; на фігурі 2 зображено принципову схему блока керування; на фігурі 3 наведено часову діаграму роботи блока керування; на фігурі 4 наведено таблицю карти прошивки блока постійної пам'яті блока керування. Пристрій для визначення інтенсивності спекулярної складової кольору при формуванні шорст 7 ких поверхонь (фіг.1) включає тригер 4, блок 18 постійної пам'яті, блок 23 керування, відповідно перший÷десятий регістри 1, 3, 5÷7, 2, 19, 11÷43, відповідно перший, другий та третій суматори 15, 16 та 31, відповідно перший÷четверий блоки 10, 20÷22 множення, відповідно перший÷четверий мультиплексори 8, 9, 17 та 14, відповідно перший÷сьомий інформаційні входи 55, 59, 32, 34, 36, 57, 61 пристрою, відповідно перший÷дев'ятий керуючі входи 56, 60, 33, 35, 37, 58, 62, 38, 39 пристрою, відповідно перший÷третій інформаційні виходи 40÷42 пристрою, відповідно перший та другий керуючі виходи 43 та 44 пристрою. Вихід другого блока 20 множення підключено до першого виходу 40 пристрою, вихід третього блока 21 множення підключено до другого виходу 41 пристрою, вихід четвертого блока 22 множення підключено до третього виходу 42 пристрою, керуючий вхід першого регістра 1 підключено до першого керуючого входу 56 пристрою, а інформаційний вхід підключено до першого інформаційного входу 24 пристрою, керуючий вхід другого регістра 3 підключено до другого керуючого входу 60 пристрою, а інформаційний вхід підключено до другого інформаційного входу 59 пристрою, керуючий вхід третього регістра 5 підключено до третього керуючого входу 33 пристрою, а інформаційний вхід підключено до третього інформаційного входу 32 пристрою, а вихід з'єднано із другим входом другого блока 20 множення, керуючий вхід четвертого регістра 6 підключено до четвертого керуючого входу 35 пристрою, а інформаційний вхід підключено до четвертого інформаційного входу 34 пристрою, а вихід з'єднано із другим входом третього блока 21 множення, керуючий вхід п'ятого регістра 7 підключено до п'ятого керуючого входу 37 пристрою, а інформаційний вхід підключено до п'ятого інформаційного входу 36 пристрою, а вихід з'єднано із другим входом четвертого блока 22 множення, інформаційний вхід тригера 4 підключено до сьомого інформаційного входу 61 пристрою, керуючий вхід якого підключено до сьомого керуючого входу 62 пристрою, а вихід - до керуючих входів першого суматора 15 та четвертого мультиплексора 14, інформаційний вхід шостого регістра 2 підключено до шостого інформаційного входу 57 пристрою, керуючий вхід якого підключено до шостого керуючого входу 58 пристрою, а вихід - до першого інформаційного входу другого мультиплексора 9 та другого інформаційного входу третього мультиплексора 17, вихід сьомого регістра 19 підключено до другого інформаційного входу другого мультиплексора 9, вихід восьмого регістра 11 підключено до першого інформаційного входу першого суматора 15, інверсний вихід дев'ятого регістра 12 підключено до першого інформаційного входу четвертого мультиплексора 14, а прямий вихід - до першого інформаційного входу третього суматора 31, другий інформаційний вхід 54 якого підключено до рівня логічної одиниці, вхід переносу 53 - до рівня логічного нуля, а вихід з'єднано з другим інформаційним входом четвертого мультиплексора, вихід якого підключено до другого інформаційного входу першого суматора 15, вихід якого підключено до третього 60139 8 інформаційного входу першого мультиплексора 8, вихід десятого регістра 13 підключено до перших входів другого 20, третього 21 та четвертого 22 блоків множення та до інформаційного входу другого суматора 16, керуючий вхід 52 якого підключено до рівня логічної одиниці, а вихід - до четвертих інформаційних входів першого та другого мультиплексорів 8 та 9, інформаційні входи восьмого, дев'ятого та десятого регістрів 11, 12 та 13 підключено до виходу першого блока 10 множення, перший інформаційний вхід якого підключено до виходу першого мультиплексора 8, а другий до виходу другого мультиплексора 9, вихід першого регістра 1 підключено до першого входу першого мультиплексора 8 та першого інформаційного входу третього мультиплексора 17, вихід якого підключено до входу блока 18 постійної пам'яті, вихід якого підключено до інформаційного входу сьомого регістра 19 та другого інформаційного входу першого мультиплексора 8, кожний і+1-й розряд виходу другого регістра 3 підключено до іго розряду третього інформаційного входу другого мультиплексора 9, перший вхід блока 23 керування з'єднано з входом 38 початкової установки, а другий - з входом 39 «Пуск», перший вихід підключено до виходу 43 ознаки достовірності, другий вихід - до виходу 44 «Кінець», третій вихід 45 - до перший керуючих входів першого та другого мультиплексорів 8 та 9, четвертий вихід 46 - до других керуючих входів першого та другого мультиплексорів 8 та 9, п'ятий вихід 47 - до керуючого входу третього мультиплексора 17, шостий вихід 48 - до керуючого входу сьомого регістра 19, сьомий вихід 49 - до керуючого входу восьмого регістра 11, восьмий вихід 50 - до керуючого входу дев'ятого регістра 12, дев'ятий вихід 51 - до керуючого входу десятого регістра 13. Блок 23 керування (фіг.2) включає перший елемент 24 І, генератор імпульсів 25, перший Dтригер 26, другий D-тригер 27, другий елемент 28 І, лічильник 29, блок 30 постійної пам'яті. Перший вхід 38 блока 23 керування підключено до першого входу першого елементу 24 І, другий вхід якого з'єднано з дев'ятим виходом 44 блока 30 постійної пам'яті. Вихід першого елементу 24 І підключено до входів обнулення першого та другого D-тригерів 26 та 27 та до входу обнулення лічильника 29. Другий вхід 39 блока 23 керування з'єднано з входом синхронізації першого D-тригера 26, інформаційний вхід 63 якого підключено до рівня логічної одиниці, а вихід якого підключено до інформаційного входу другого D-тригера 27, вхід синхронізації якого з'єднано з інверсним виходом генератора імпульсів 25, прямий вихід якого підключено до першого входу другого елемента 28 І, другий вхід якого з'єднано з виходом другого Dтригера 27, а вихід підключено до входу синхронізації лічильника 29, виходи якого підключено до входів блока 30 постійної пам'яті, перший вихід якого підключено до третього виходу 45, другий до четвертого виходу 46, третій - до п'ятого виходу 47, четвертий - до шостого виходу 48, п'ятий - до сьомого виходу 49, шостий - до восьмого виходу 50, сьомий - до дев'ятого виходу 51, восьмий - до першого виходу 43 та дев'ятий - до другого виходу 9 60139 44 блока 23 керування. Для зафарбовування об'єктів, зазвичай, використовується модель освітлення Бліна, згідно з якою інтенсивність спекулярної складової кольору розраховується за формулою: n (1) I=Ilkscos , де Il - інтенсивність джерела світла, ks - коефіцієнт дзеркального відбиття, n - коефіцієнт спекулярності поверхні, який знаходить в діапазоні [1; 1000], - кут між вектором нормалі N до поверхні n в заданій точці і вектором півшляху H , cos - дистрибутивна функція відбивної здатності поверхні (BRDF). У пристрої-прототипі для апроксимації дисn трибутивної функції cos було використано функцію 2 n (2) cosn cos 1 1 , 2 У пристрої, що пропонується, функцію 2 n було модифіковано таким чи cos 1 1 2 ном, щоб її можна було використовувати при формуванні реалістичного відблиску на шорстких поверхнях. Традиційний бамп-меппінг передбачає збурення нормалей в кожній точці поверхні з метою імітації нерівностей на ній. Внаслідок збурення нормалі кут між вектором збуреної нормалі та вектором півшляху змінюється. Він може як зменшитись, так і збільшитись. Відповідно косинус цього кута також змінюється: чим менше кут, тим більше значення косинуса, і навпаки. Таким чином, можна імітувати нерівності на поверхні безпосередньо шляхом зміни кута між вектором нормалі та вектором півшляху на певну величину dy, яка зчитується з певної карти. Тоді дистрибутивна функція відбивної здатності (2) прийме вигляд: n cos d 1 1 2 2 n cos cos d sin sin d 1 1 2 2 , (3) З урахуванням формули (3) формула (1) прийме вигляд: 2 n (4) I Ilk s cos cos d sin sin d 1 1 , 2 Пристрій працює наступним чином. При включенні пристрою на вхід 38 початкової установки поступає рівень логічного нуля, який забезпечує установку пристрою в режим очікування сигналу прийому даних від зовнішнього пристрою. Параметр cos поступає на перший інформаційний вхід 55 пристрою і записується в перший регістр 1 активним рівнем сигналу на першому керуючому вході 56. Значення cosd заноситься в шостий регістр 2. Для цього на шостий інформаційний вхід 57 пристрою поступає операнд cosd, який записується в шостий регістр 2 активним рів 10 нем сигналу на шостому керуючому вході 58. На другий інформаційний вхід 59 пристрою поступає значення коефіцієнта спекулярності n, яке записується в другий регістр 3 активним рівнем сигналу на другому керуючому вході 60. У третій 5, четвертий 6 та п'ятий 7 регістри від зовнішнього пристрою записується відповідно значення інтенсивностей R, G, В складових кольору, помножених на коефіцієнт дзеркального відбиття поверхні ks. Для цього на третій 32, четвертий 34 та п'ятий 36 інформаційні входи пристрою подаються відповідно значення інтенсивності R-складової, G-складової та В-складової кольору, помножених на коефіцієнт дзеркального відбиття поверхні ks, а на третій 33, четвертий 35 та п'ятий 37 керуючі входи пристрою подається рівень логічної одиниці. У тригер 4 записується значення знаку приросту кута d, для цього значення знаку подається на сьомий 61 інформаційний вхід пристрою, та записується у тригер 4 активним значенням сигналу на сьомому 62 керуючому вході пристрою. Визначення інтенсивності дзеркальної складової кольору починається з моменту подачі на вхід 39 сигналу «Пуск», який подається після занесення операндів в блоки 1-7 пристрою. Відразу після надходження сигналу «Пуск» на виході 43 пристрою формується рівень логічного нуля, який сигналізує, що пристрій знаходиться в режимі формування інтенсивності дзеркальної складової кольору і не готовий до прийому операндів в блоки 1-7 пристрою. В початковий момент часу на третьому виході 45 та четвертому виході 46 блока 23 керування формуються рівні логічного нуля, під дією яких через перший мультиплексор 8 та другий мультиплексор 9 забезпечується передача значення cos з виходу першого регістра 1 та значення cosd з виходу шостого регістра 2 відповідно на перший та другий входи першого блока 10 множення. В цей же момент часу на п'ятому виході 47 блока 23 керування формується рівень логічного нуля, під дією якого через третій мультиплексор 17 забезпечується передача значення cos з виходу першого регістра 1 на вхід блока 18 постійної пам'яті. В наступний момент часу на сьомому виході 49 блока 23 керування формується рівень логічної одиниці, під дією якого у восьмий регістр 11 записується значення, що поступає з виходу першого блока 10 множення, а саме cos·cosd·. На шостому виході 48 блока 23 керування також формується рівень логічної одиниці, що забезпечує запис у сьомий регістр 19 значення з виходу блока 18 постійної пам'яті, а саме значення sin. У третій момент часу під дією активного сигналу на п'ятому виході 47 блока 23 керування забезпечується передача значення cosd з виходу шостого регістра 2 через третій мультиплексор 17 на вхід блока 18 постійної пам'яті. Рівень логічного нуля на третьому виході 45 та логічної одиниці на четвертому виході 46 блока 23 керування забезпечують передачу значення sind з виходу блока 18 постійної пам'яті через перший мультиплексор 8 та значення sin з виходу сьомого регістра 19 через другий мультиплексор 9 відповідно на перший та другий входи першого блока 10 множення. 11 У наступний момент часу активний сигнал на восьмому виході 50 блока 23 керування забезпечує запис значення sin·sind з виходу першого блока 10 множення в дев'ятий регістр 12. На керуючі входи четвертого мультиплексора 14 та першого суматора 15 поступає значення з виходу тригера 4. Якщо з виходу тригера 4 поступає рівень логічного нуля, то через четвертий мультиплексор 14 на другий інформаційний вхід першого суматора 15 передається значення з інверсного виходу дев'ятого регістра 12, якщо рівень логічної одиниці - з виходу третього суматора 31. Якщо знак приросту значення d додатній, тобто на виході тригера 4 формується рівень логічного нуля, то у першому суматорі 15 повинна виконуватись операція «cos·cosd-sin·sind-1». Доведено, що cos·cosd-sin·sind-1=Прямий код числа cos·cosd+Обернений код числа sin·sind, оскільки при додаванні до прямого коду числа А оберненого коду числа В отримуємо число, що на одиницю менше від результату операції А-В. В даному випадку необхідно отримати саме число, що на одиницю менше від результату cos·cosdsin·sind, тому на вхід переносу першого суматора 15 потрібно також подати рівень логічного нуля. Якщо з виходу тригера 4 поступає рівень логічної одиниці, то у першому суматорі 15 повинна виконуватись операція «cos·cosd-sin·sind-1». Для цього на вхід переносу першого суматора 15 подається рівень логічної одиниці з виходу тригера 4, на перший інформаційний вхід - значення cos·cosd з виходу восьмого регістра 11, а на другий інформаційний вхід - значення sin·sind-1 з виходу третього суматора 31 через четвертий мультиплексор 14. Значення sin·sind-1 формується таким чином. З прямого виходу дев'ятого регістра 12 на перший інформаційний вхід третього суматора 31 подається прямий код числа sin·sind, а на кожний розряд другого інформаційного входу 54 якого подається рівень логічної одиниці, що забезпечує віднімання від операнду значення 1. Дійсно, прямий код 1-000...01, обернений код 1111...10. Зрозуміло, що в молодшому розряді оберненого коду 1 завжди присутній «0». Щоб отримати доповнюючий код 1 потрібно до молодшого розряду додати 1, тобто доповнюючий код 1 дорівнює 111...11. На вхід переносу 53 третього суматора 31 подається рівень логічного нуля, що забезпечує формування на його виході значення sin·sind-1, яке поступає на другий вхід четвертого мультиплексора 14. У наступному такті на третьому виході 45 блока 23 керування формується рівень логічної одиниці, а на четвертому виході 46 блока 23 керування - рівень логічного нуля, що забезпечує передачу значення з виходу першого суматора 15 через перший мультиплексор 8 та значення з виходу другого регістра 3 через другий мультиплексор 9 відповідно на перший та другий входи першого блока 10 множення. При чому, кожний і+1-й розряд виходу другого регістра 3 підключено до іго розряду третього інформаційного входу другого мультиплексора 9, що забезпечує подачу на дру 60139 12 гий інформаційний вхід першого блока 10 множення значення n . 2 У шостий момент часу на дев'ятому виході 51 блока 23 керування формується активний сигнал, що забезпечує запис в десятий регістр 13 значенn ня cos cos d sin sin d 1 з виходу першо2 го блока 10 множення. Отримане значення з виходу десятого регістра 13 поступає на інформаційний вхід другого суматора 16, на керуючий вхід якого подано рівень логічної одиниці, що забезпечує виконання операції n cos cos d sin sin d 1 1 . 2 У наступний момент часу на третьому виході 45 та четвертому виході 46 блока 23 керування формуються рівні логічної одиниці, під дією яких через перший мультиплексор 8 та другий мультиплексор 9 забезпечується передача значення n cos cos d sin sin d 1 1 з виходу другого 2 суматора 16 відповідно на перший та другий входи першого блока 10 множення. На восьмому такті активний сигнал на дев'ятому виході 51 блока 23 керування забезпечує запис в десятий регістр 13 значення 2 n з виходу 2 cos cos d sin sin d 1 1 першого блока 10 множення. Отримане значення з виходу десятого регістра 13 поступає на перші входи другого 20, третього 21 та четвертого 22 блоків множення. На другі входи другого 20, третього 21 та четвертого 22 блоків множення подаються значення інтенсивностей R, G, В складових кольору, помножених на коефіцієнт дзеркального відбиття поверхні ks із виходів третього 5, четвертого 6 та п'ятого 7 регістрів відповідно. На першому 40, другому 41 та третьому 42 інформаційних виходах пристрою формуються R, G, В складові інтенсивностей кольору, які знайдено за формулою (4). У наступний момент часу на першому керуючому виході 43 пристрою формується активний сигнал, який сигналізує про те, що на інформаційних виходах пристрою отримано достовірні дані. На завершальному десятому такті на другому керуючому виході 44 пристрою формується сигнал від'ємної полярності, який поступає на другий вхід першого елементу 24 І. Під дією даного сигналу блок 23 керування переходить в початковий стан, а на першому керуючому виході 43 пристрою формується сигнал нульового рівня, який сигналізує, що пристрій визначив інтенсивності кольору поточної точки рядка растеризації і готовий до прийому нових операндів наступної точки рядка растеризації. У блоці 30 постійної пам'яті зберігається значення виходів 43÷51. Враховуючи, що для роботи пристрою необхідно 10 тактів, то кількість комірок блока 30 постійної пам'яті буде дорівнювати кількості тактів. В табл. 1 (фіг.4) наведено таблицю карти прошивки блока 30 постійної пам'яті. 15 60139 16 17 60139 18 19 Комп’ютерна верстка Л. Ціхановська 60139 Підписне 20 Тираж 24 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for determination of specular color component intensity in forming rough shape surface

Автори англійськоюRomaniuk Oksana Volodymyrivna, Romaniuk Oleksandr Nykyforovych, Voitko Viktoriia Volodymyrivna

Назва патенту російськоюУстройство для определения интенсивности спекулярной составлющей цвета при формировании шероховатых поверхностей

Автори російськоюРоманюк Оксна Владимировна, Романюк Александр Никифорович, Войтко Виктория Владимировна

МПК / Мітки

МПК: G06T 15/00

Мітки: пристрій, поверхонь, спекулярної, визначення, інтенсивності, складової, шорстких, формуванні, кольору

Код посилання

<a href="https://ua.patents.su/10-60139-pristrijj-dlya-viznachennya-intensivnosti-spekulyarno-skladovo-koloru-pri-formuvanni-shorstkikh-poverkhon.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення інтенсивності спекулярної складової кольору при формуванні шорстких поверхонь</a>

Попередній патент: Спосіб отримання спеченого твердого сплаву

Наступний патент: Спосіб фіксації обстановки і наслідків дтп

Випадковий патент: Пристрій для захисту електродвигуна від нездійсненого пуску