Імпульсний стабілізатор бекірова

Формула / Реферат

1. Імпульсний стабілізатор, що містить двотактний регульований силовий перетворювач із силовим вихідним трансформатором і попереднім двотранзисторним підсилювачем, пристрій керування, що складається з задавального генератора, формувача імпульсів керування, широтно-імпульсного модулятора і перетворювача зворотного зв'язку, при цьому задавальний генератор, виконаний у вигляді функціонального генератора, що складається з генератора трикутних імпульсів, виконаного за схемою інтегратора, і синхронізованого з ним генератора прямокутних імпульсів, виконаного за схемою компаратора, формувач імпульсів керування виконаний за схемою фазоінвертора і реалізований на цифрових мікросхемах, а широтно-імпульсний модулятор виконаний на операційному підсилювачі, який відрізняється тим, що додатково містить пристрій захисту по вихідному струму, пристрій захисту по вхідному струму і перевищенню вихідної напруги і зв'язаний з ним попередній стабілізатор напруги, силовий перетворювач виконаний за мостовою схемою, попередній підсилювач містить проміжний трансформатор, формувач імпульсів керування з'єднаний з виходом пристрою захисту по вихідному струму, на вході перетворювача зворотного зв'язку встановлений мостовий випрямляч напруги зворотного зв'язку, а силовий вихідний трансформатор підключений до блока мостових випрямлячів.

2. Імпульсний стабілізатор за п. 1, який відрізняється тим, що пристрій захисту по вихідному струму містить вузол мостового випрямляча, вхід якого з'єднаний з виходом трансформатора струму, а вихід вузла випрямляча з'єднаний із входом інвертувального вузла, порівняння й установки порога захисту, що являє собою компаратор, виконаний на операційному підсилювачі, прямий вхід якого з'єднаний із движком потенціометра резистивного подільника напруги, а вихід з'єднаний із входом S вузла пам'яті, вхід R якого з'єднаний з вузлом установки схеми в нуль, прямий вихід вузла пам'яті з'єднаний зі схемою імпульсного стабілізатора, інверсний вихід вузла пам'яті з'єднаний з вузлом індикації «перевантаження», виконаного на транзисторному підсилювальному каскаді зі світлодіодним індикатором, причому вузол пам'яті виконаний на чотирьох логічних елементах І, вузол установки схеми в нуль виконаний на послідовно з'єднаних резисторі і конденсаторі, середня точка яких підключена до входу R вузла пам'яті.

3. Імпульсний стабілізатор за п. 1, який відрізняється тим, що пристрій захисту по вхідному струму і перевищенню вихідної напруги містить датчик струму з транзистором захисту по струму, вузол порівняння, вузол пам'яті і вихідний вузол, причому вихід вузла порівняння підключений до S-входу вузла пам'яті, до R-входу якого підключений RC-ланцюжок установки в нуль вузла пам'яті, а вихід вузла пам'яті з'єднаний з вихідним вузлом, крім того, вузол порівняння виконаний на транзисторі, база якого через резистор з'єднана з виходом стабілізатора напруги, а колектор з'єднаний з першим входом логічного елемента І, другий вхід якого з'єднаний з колектором транзистора захисту по струму, при цьому вихід логічного елемента І через інвертор з'єднаний з S-входом вузла пам'яті, вузол пам'яті виконаний на двох логічних елементах І у вигляді RS-тригера, при цьому вихідний вузол виконаний на двокаскадному транзисторному підсилювачі, вхід якого з'єднаний з виходом вузла пам'яті, а вихід - з базою регулюючого транзистора стабілізатора напруги.

4. Імпульсний стабілізатор за п. 1, який відрізняється тим, що попередній стабілізатор напруги містить регулюючий і керуючий транзистори, L-C-VD-фільтр, вузол керування, при цьому регулюючий транзистор виконаний у вигляді двох складених транзисторів, причому в базовий ланцюг вихідного транзистора включений струмообмежувальний резистор, а вузол керування виконаний у вигляді компаратора, прямий вхід якого з'єднаний з резистивним подільником, включеним у вихідний ланцюг пристрою, у який також включений параметричний стабілізатор напруги, підключений до входу інвертувального компаратора, вихід якого через керуючий транзистор підключений до бази регулюючого транзистора.

5. Імпульсний стабілізатор за п. 1, який відрізняється тим, що силовий перетворювач виконаний за мостовою схемою і містить двотактний транзисторний регульований перетворювач із силовим вихідним трансформатором, причому входи попереднього двотранзисторного підсилювача з'єднані зі схемою керування, а виходи навантажені на бази силових транзисторів перетворювача через проміжний трансформатор, причому двотактний транзисторний регульований перетворювач виконаний за мостовою схемою на чотирьох силових транзисторах, ланцюги емітер - база яких зашунтовані діодами, а в базові ланцюги включені струмообмежувальні резистори, при цьому в колекторні ланцюги двох пар силових транзисторів включена первинна обмотка силового вихідного трансформатора.

6. Імпульсний стабілізатор за п. 1, який відрізняється тим, що блок мостових випрямлячів містить вісім силових мостових випрямлячів з згладжувальними фільтрами на дроселях і конденсаторах і малопотужний мостовий випрямляч із дроселем, інтегральним стабілізатором напруги і конденсаторним фільтром.

Текст

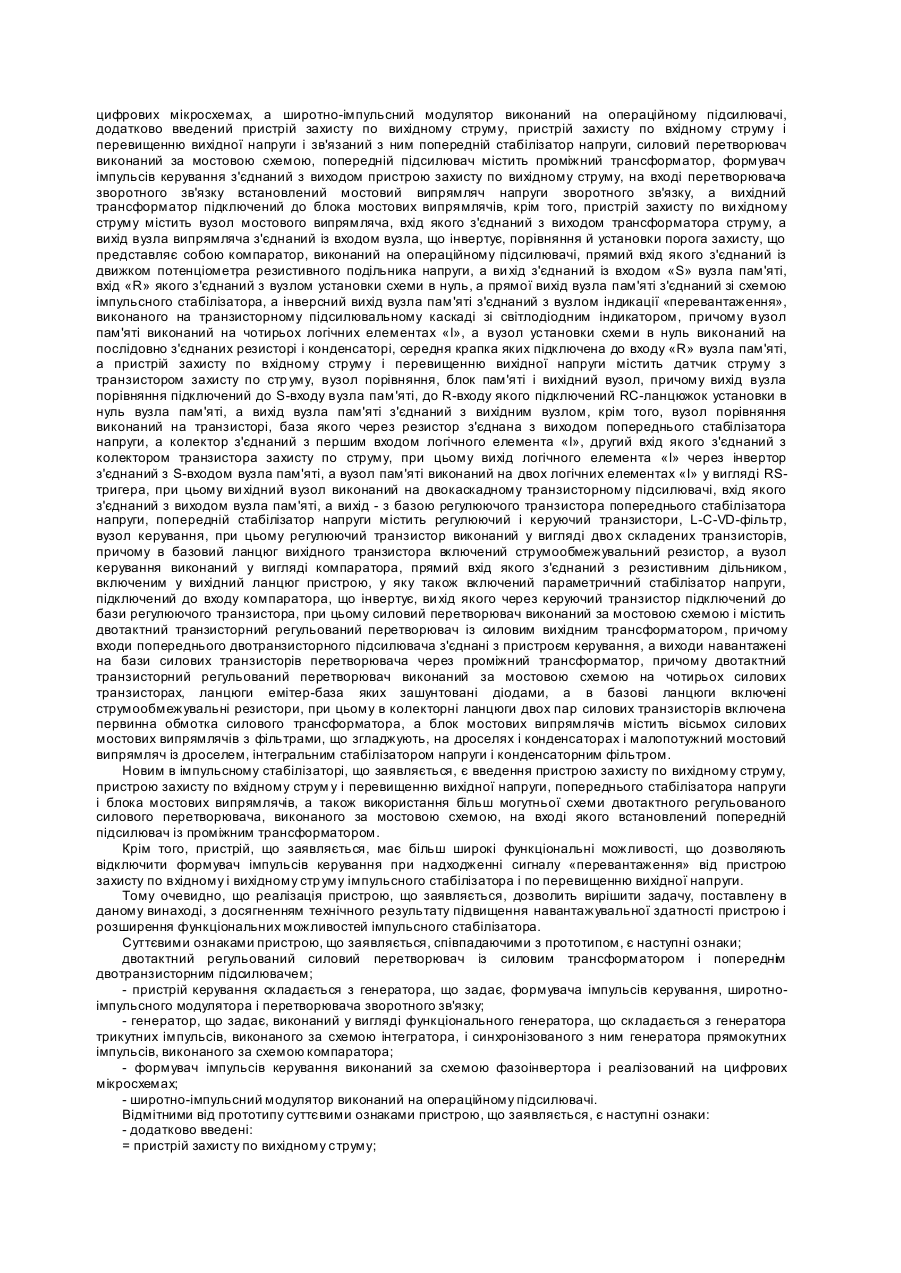

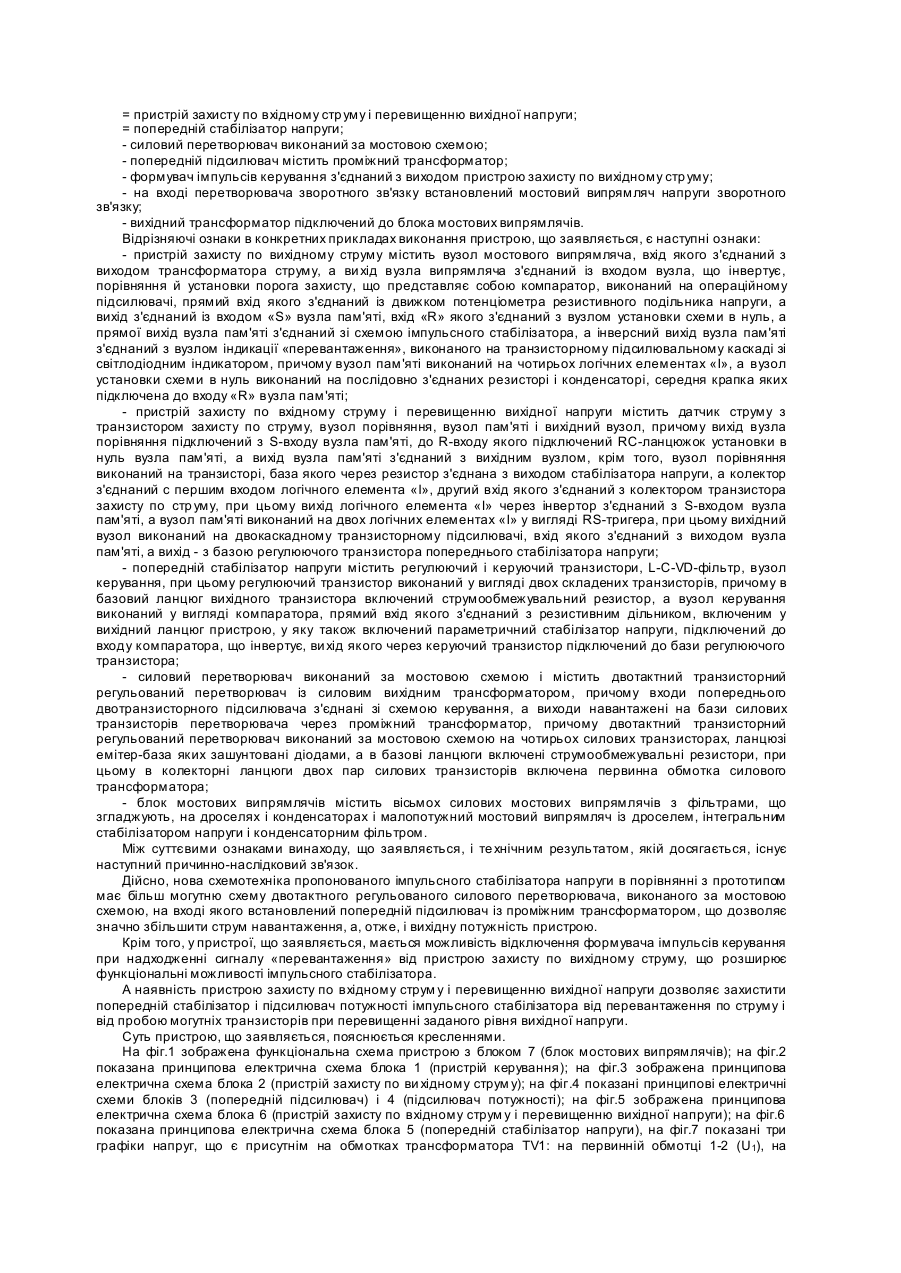

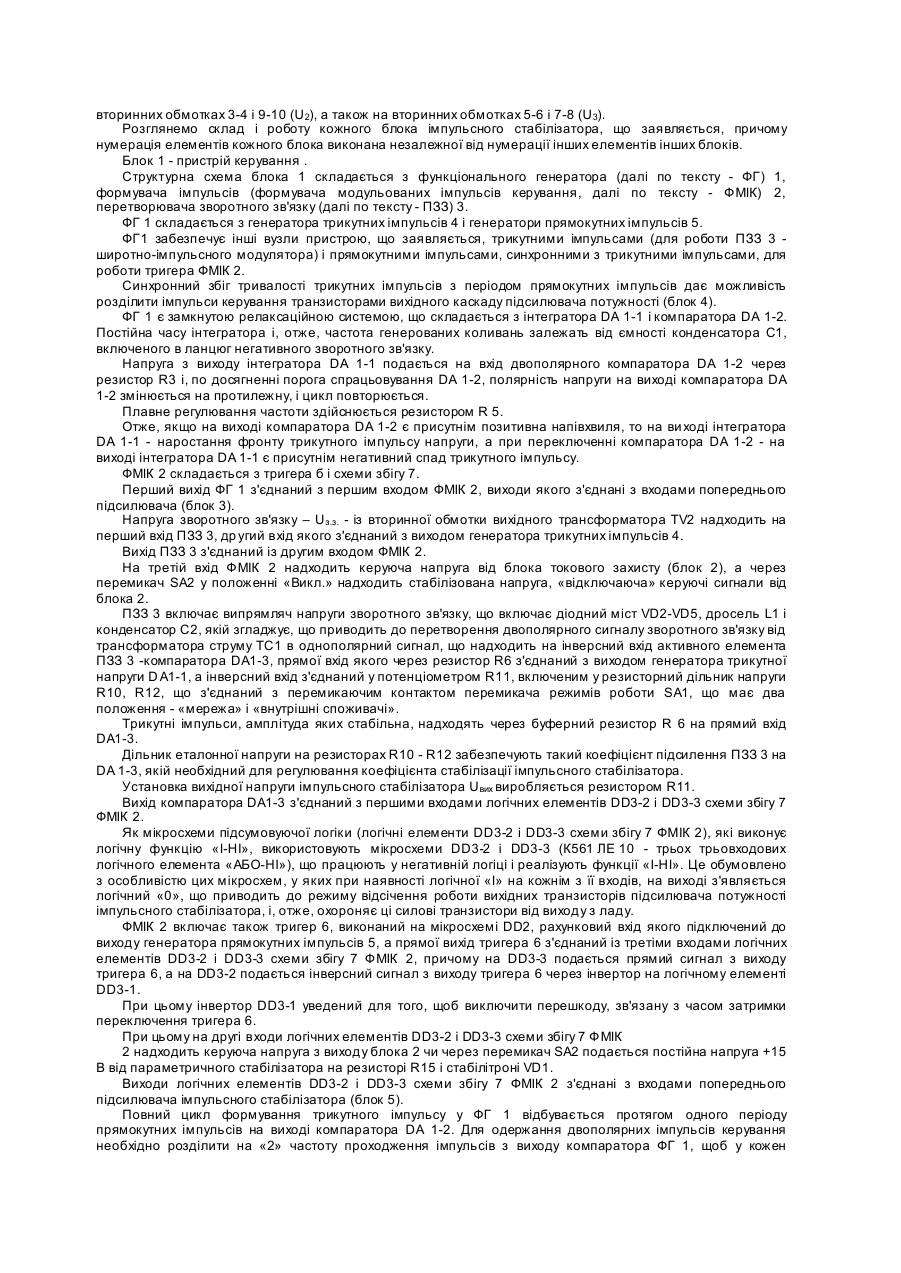

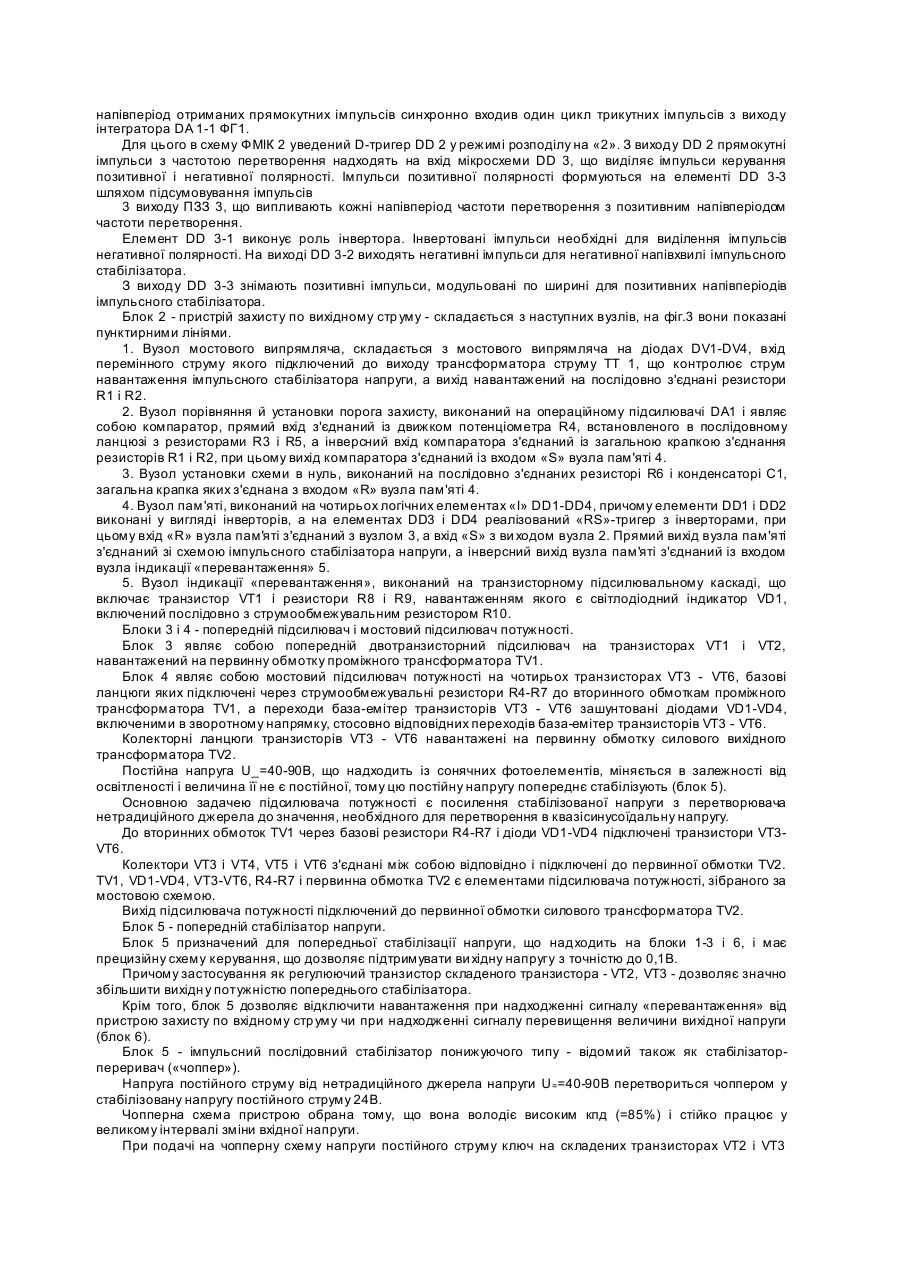

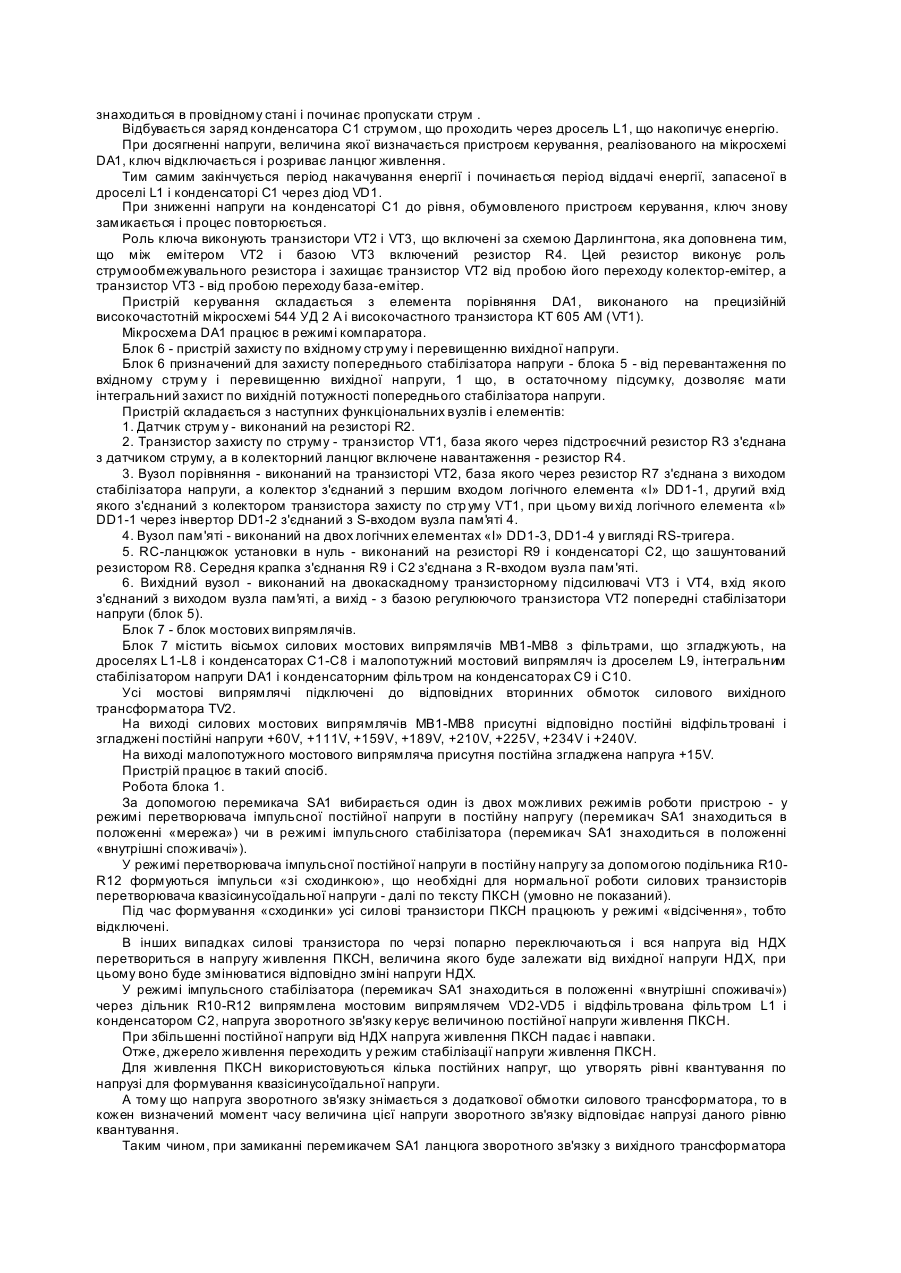

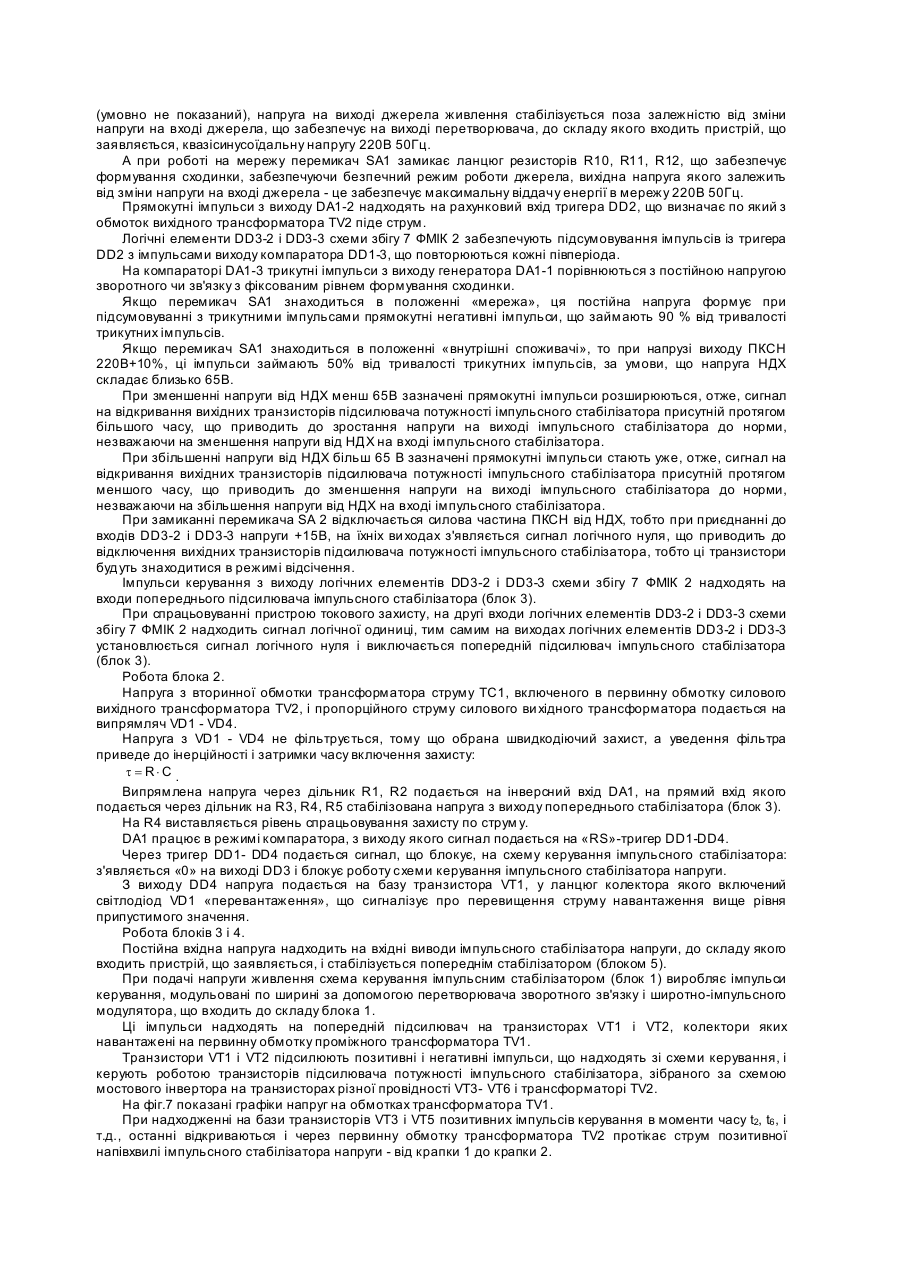

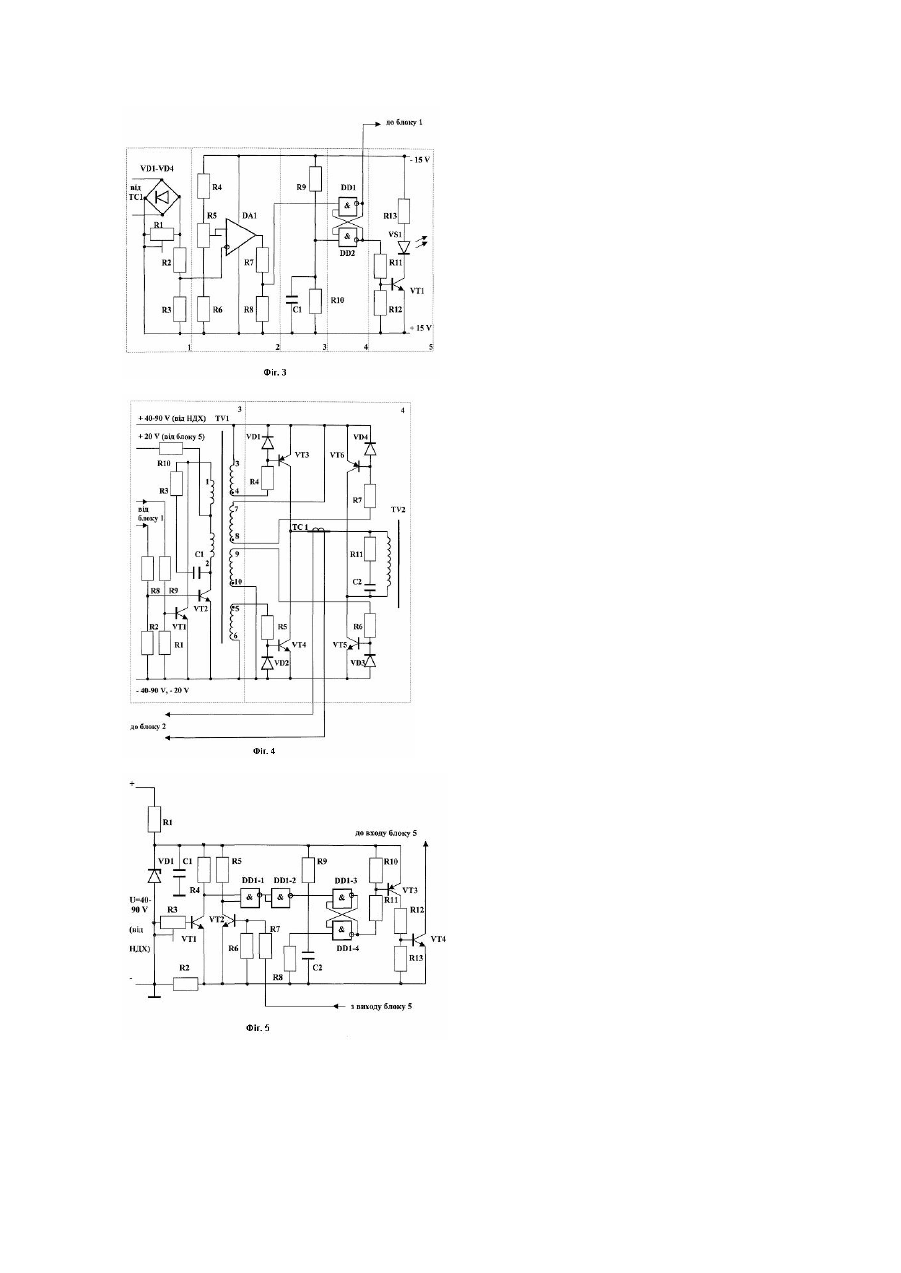

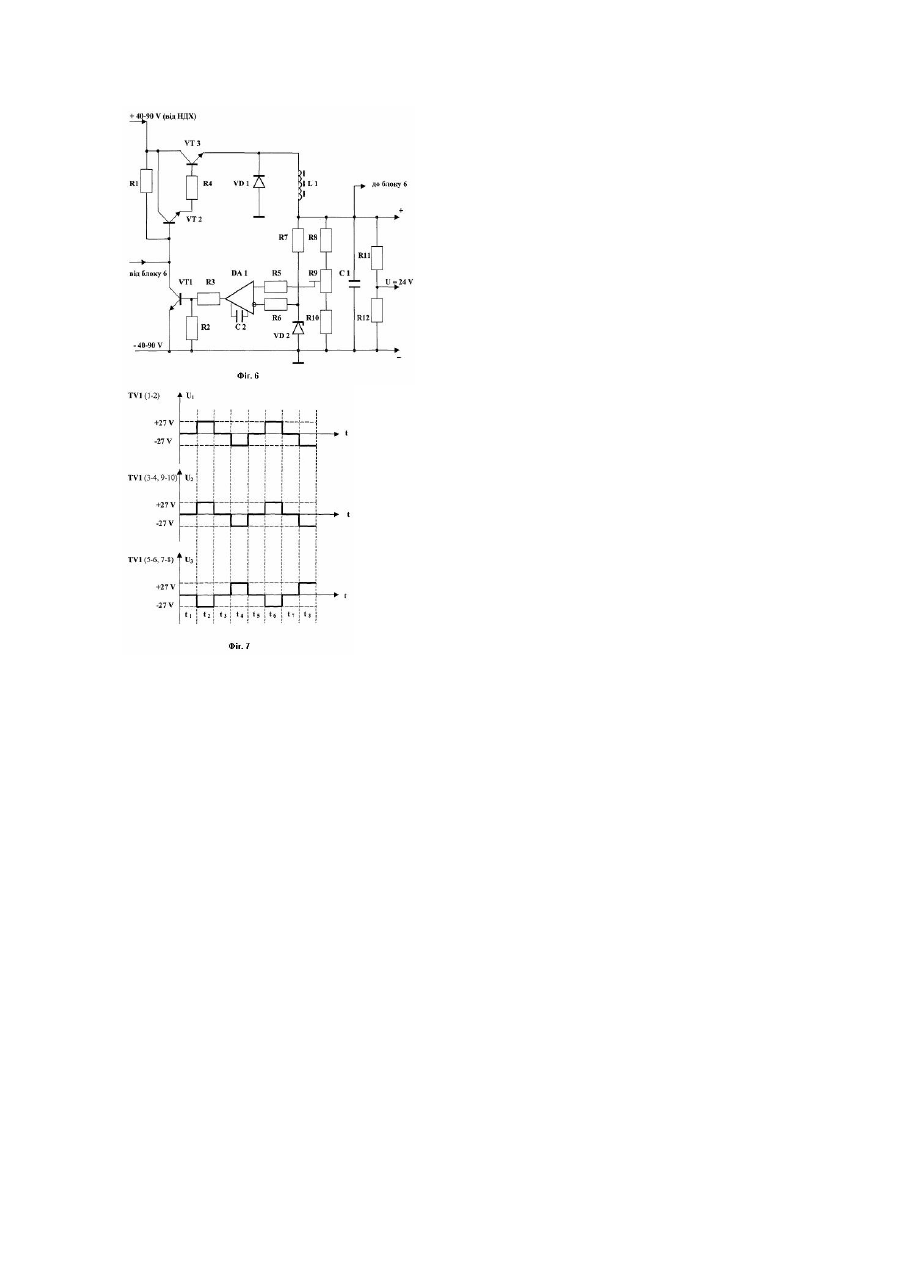

Винахід відноситься до області електротехніки, зокрема до пристроїв перетворення параметрів електричної енергії і може бути використаний для створення джерел вторинного електроживлення з безтрансформаторним входом і поліпшеною електромагнітною сумісністю, агрегатів безперебійного електроживлення і систем гарантованого електроживлення відповідальних споживачів, а також може бути використаний в складі перетворювача постійної напруги нетрадиційного джерела живлення (далі по тексту НДХ) у перемінну синусоїдальну напругу промислової частоти. Широко відомі однотактні імпульсні стабілізатори напруги послідовного і рівнобіжного типів (наприклад, «Джерела електроживлення РЭА», довідник під ред. Г.С. Найвельта, М., «Радіо і зв'язок», 1986 p., c.32-34; «Джерела вторинного електроживлення», довідковий посібник під ред. Ю.И. Конєва, М., «Радіо і зв'язок». 1983 р., с.79-81; С.А. Эраносян, «Мережні блоки живлення з високочастотними перетворювачами», Л., «Энергоатомиздат», 1991р., с.21-30). Цим стабілізаторам придатні наступні недоліки: - невеликий граничний коефіцієнт заповнення імпульсів напруги на силовому трансформаторі; - неповне використання силового трансформатора, тому що відомо, що силовий трансформатор (його сердечник) в однотактних каскадах перемагнічується не по повній петлі гістерезиса, що може привести до перегріву і ви ходу з ладу силового транзистора і, щоб усун ути цей недолік, звичайно значно ускладнюють схеми керування, запуску і вимикання. Відомий «Імпульсний стабілізатор постійної напруги» (a.c. CPCP №1067486, МПК-3 G 05 F 1/56, БВ-284p.), якій містить двотактний регульований перетворювач із силовим трансформатором, через вихідні випрямляч і фільтр зв'язаний з вихідними виводами, формувач імпульсів, виходами з'єднаний з керуючими входами перетворювача, а входами через повторювач імпульсів і безпосередньо - з виходом тригера, перший вхід якого з'єднаний з виходом ШІМ, один із входів якого через формувач пилкоподібної напруги зв'язаний з виходом генератора, що задає, інший вхід ШІМ з'єднаний з виходом підсилювача зворотного зв'язку, входи якого підключені до вихідних виводів і джерела опорної напруги відповідно, при цьому в стабілізатор уведені додатковий випрямляч з RC - фільтром, підключені до вихідної обмотки силового трансформатора і з'єднані з першим входом елемента, що порівнює, другий вхід якого підключений до виходу джерела опорної напруги, виходи елемента, що порівнює, і пилкоподібного пилкоподібної напруги підключені до відповідного входам уведеного компаратора, вихід якого з'єднаний із другим входом тригера. Недоліками цього пристрою є: - низька лінійність пилкоподібної напруги, зв'язана з зарядом конденсатора через елемент, що не забезпечує стабільного струму; - необхідність уведення ланцюгів синхронізації для симетрування перемагнічування осередка і наближення лінійності пилкоподібної напруги до ідеального приводить до ускладнення принципової схеми керування і зменшенню надійності в зв'язку зі збільшенням кількості елементів. Найбільш близьким по технічній сутності і результату, якій досягається, і обраним як прототип є «Імпульсний стабілізатор постійної напруги» (Патент України №54292, МПК-7 G 05 F 1/56, H 02 M 3/335, H 02 M 7/00, БИ-2 - 2003p.), що містить двотактний двотранзисторний регульований перетворювач із силовим трансформатором, вихідні випрямляч і фільтр, генератор, що задає, і формувач імпульсів, широтноімпульсний модулятор, перетворювач зворотного зв'язку, генератор, що задає, виконаний у вигляді функціонального генератора, що включає генератор трикутних імпульсів, виконаний за схемою інтегратора, і синхронізований з ним генератор прямокутних імпульсів, виконаний за схемою компаратора, формувач імпульсів виконаний за схемою фазоінвертора, виконаного на цифрових мікросхемах, широтно-імпульсний модулятор виконаний на операційному підсилювачі, а перетворювач зворотного зв'язку включає оптоелектронний перетворювач вихідного сигналу стабілізатора, транзисторний емітерний повторювач і підсилювач зворотного зв'язку на операційному підсилювачі, причому вихід генератора трикутних сигналів з'єднаний з першим входом генератора прямокутних імпульсів і з першим входом широтно-імпульсного модулятора, вихід генератора прямокутних імпульсів підключений до рахункового входу тригера фазоінвертора, вихід перетворювача зворотного зв'язку підключений до другого входу широтноімпульсного модулятора, вихід якого підключений до входів логічних елементів фазоінвертора, два виходи якого підключені до двох входів попереднього двотранзисторного підсилювача, виходи яких навантажені на бази силових транзисторів двотактного двотранзисторного регульованого перетворювача, а схема керування стабілізатора харчується від вхідного параметричного стабілізатора, крім того, вихідний випрямляч виконаний за мостовою схемою, а вихідний фільтр виконаний за схемою LC-фільтра зі штучною нульовою крапкою, при цьому вхідний параметричний стабілізатор виконаний за схемою зі штучною нульовою крапкою. Недоліком прототипу є низька навантажувальна здатність пристрою і відсутність можливості захисту з струму імпульсного стабілізатора. Задачею винаходу є розробка нової схемотехніки імпульсного стабілізатора з досягненням технічного результату - підвищення навантажувальної здатності пристрою і розширення функціональних можливостей імпульсного стабілізатора. Поставлена задача зважується тим, що в «Імпульсному стабілізаторі Бекірова», що містить двотактний регульований силовий перетворювач із силовим трансформатором і попереднім двотранзисторним підсилювачем, пристрій керування складається з генератора, що задає, формувача імпульсів керування, широтно-імпульсного модулятора і перетворювача зворотного зв'язку, при цьому генератор, що задає, виконаний у вигляді функціонального генератора, що складає з генератора трикутних імпульсів, виконаного за схемою інтегратора, і синхронізованого з ним генератора прямокутних імпульсів, виконаного за схемою компаратора, формувач імпульсів керування виконаний за схемою фазоінвертора і реалізований на цифрових мікросхемах, а широтно-імпульсний модулятор виконаний на операційному підсилювачі, додатково введений пристрій захисту по вихідному струму, пристрій захисту по вхідному струму і перевищенню вихідної напруги і зв'язаний з ним попередній стабілізатор напруги, силовий перетворювач виконаний за мостовою схемою, попередній підсилювач містить проміжний трансформатор, формувач імпульсів керування з'єднаний з виходом пристрою захисту по вихідному струму, на вході перетворювача зворотного зв'язку встановлений мостовий випрямляч напруги зворотного зв'язку, а вихідний трансформатор підключений до блока мостових випрямлячів, крім того, пристрій захисту по ви хідному струму містить вузол мостового випрямляча, вхід якого з'єднаний з виходом трансформатора струму, а вихід вузла випрямляча з'єднаний із входом вузла, що інвертує, порівняння й установки порога захисту, що представляє собою компаратор, виконаний на операційному підсилювачі, прямий вхід якого з'єднаний із движком потенціометра резистивного подільника напруги, а ви хід з'єднаний із входом «S» вузла пам'яті, вхід «R» якого з'єднаний з вузлом установки схеми в нуль, а прямої вихід вузла пам'яті з'єднаний зі схемою імпульсного стабілізатора, а інверсний вихід вузла пам'яті з'єднаний з вузлом індикації «перевантаження», виконаного на транзисторному підсилювальному каскаді зі світлодіодним індикатором, причому вузол пам'яті виконаний на чотирьох логічних елементах «І», а вузол установки схеми в нуль виконаний на послідовно з'єднаних резисторі і конденсаторі, середня крапка яких підключена до входу «R» вузла пам'яті, а пристрій захисту по вхідному струму і перевищенню вихідної напруги містить датчик струму з транзистором захисту по стр уму, вузол порівняння, блок пам'яті і вихідний вузол, причому вихід вузла порівняння підключений до S-входу вузла пам'яті, до R-входу якого підключений RC-ланцюжок установки в нуль вузла пам'яті, а вихід вузла пам'яті з'єднаний з вихідним вузлом, крім того, вузол порівняння виконаний на транзисторі, база якого через резистор з'єднана з виходом попереднього стабілізатора напруги, а колектор з'єднаний з першим входом логічного елемента «І», другий вхід якого з'єднаний з колектором транзистора захисту по струму, при цьому вихід логічного елемента «І» через інвертор з'єднаний з S-входом вузла пам'яті, а вузол пам'яті виконаний на двох логічних елементах «І» у вигляді RSтригера, при цьому ви хідний вузол виконаний на двокаскадному транзисторному підсилювачі, вхід якого з'єднаний з виходом вузла пам'яті, а вихід - з базою регулюючого транзистора попереднього стабілізатора напруги, попередній стабілізатор напруги містить регулюючий і керуючий транзистори, L-C-VD-фільтр, вузол керування, при цьому регулюючий транзистор виконаний у вигляді дво х складених транзисторів, причому в базовий ланцюг вихідного транзистора включений струмообмежувальний резистор, а вузол керування виконаний у вигляді компаратора, прямий вхід якого з'єднаний з резистивним дільником, включеним у вихідний ланцюг пристрою, у яку також включений параметричний стабілізатор напруги, підключений до входу компаратора, що інвертує, ви хід якого через керуючий транзистор підключений до бази регулюючого транзистора, при цьому силовий перетворювач виконаний за мостовою схемою і містить двотактний транзисторний регульований перетворювач із силовим вихідним трансформатором, причому входи попереднього двотранзисторного підсилювача з'єднані з пристроєм керування, а виходи навантажені на бази силових транзисторів перетворювача через проміжний трансформатор, причому двотактний транзисторний регульований перетворювач виконаний за мостовою схемою на чотирьох силових транзисторах, ланцюги емітер-база яких зашунтовані діодами, а в базові ланцюги включені струмообмежувальні резистори, при цьому в колекторні ланцюги двох пар силових транзисторів включена первинна обмотка силового трансформатора, а блок мостових випрямлячів містить вісьмох силових мостових випрямлячів з фільтрами, що згладжують, на дроселях і конденсаторах і малопотужний мостовий випрямляч із дроселем, інтегральним стабілізатором напруги і конденсаторним фільтром. Новим в імпульсному стабілізаторі, що заявляється, є введення пристрою захисту по вихідному струму, пристрою захисту по вхідному струм у і перевищенню вихідної напруги, попереднього стабілізатора напруги і блока мостових випрямлячів, а також використання більш могутньої схеми двотактного регульованого силового перетворювача, виконаного за мостовою схемою, на вході якого встановлений попередній підсилювач із проміжним трансформатором. Крім того, пристрій, що заявляється, має більш широкі функціональні можливості, що дозволяють відключити формувач імпульсів керування при надходженні сигналу «перевантаження» від пристрою захисту по вхідному і вихідному стр уму імпульсного стабілізатора і по перевищенню вихідної напруги. Тому очевидно, що реалізація пристрою, що заявляється, дозволить вирішити задачу, поставлену в даному винаході, з досягненням технічного результату підвищення навантажувальної здатності пристрою і розширення функціональних можливостей імпульсного стабілізатора. Суттєвими ознаками пристрою, що заявляється, співпадаючими з прототипом, є наступні ознаки; двотактний регульований силовий перетворювач із силовим трансформатором і попереднім двотранзисторним підсилювачем; - пристрій керування складається з генератора, що задає, формувача імпульсів керування, широтноімпульсного модулятора і перетворювача зворотного зв'язку; - генератор, що задає, виконаний у вигляді функціонального генератора, що складається з генератора трикутних імпульсів, виконаного за схемою інтегратора, і синхронізованого з ним генератора прямокутних імпульсів, виконаного за схемою компаратора; - формувач імпульсів керування виконаний за схемою фазоінвертора і реалізований на цифрових мікросхемах; - широтно-імпульсний модулятор виконаний на операційному підсилювачі. Відмітними від прототипу суттєвими ознаками пристрою, що заявляється, є наступні ознаки: - додатково введені: = пристрій захисту по вихідному струму; = пристрій захисту по вхідному стр уму і перевищенню вихідної напруги; = попередній стабілізатор напруги; - силовий перетворювач виконаний за мостовою схемою; - попередній підсилювач містить проміжний трансформатор; - формувач імпульсів керування з'єднаний з виходом пристрою захисту по вихідному стр уму; - на вході перетворювача зворотного зв'язку встановлений мостовий випрямляч напруги зворотного зв'язку; - вихідний трансформатор підключений до блока мостових випрямлячів. Відрізняючі ознаки в конкретних прикладах виконання пристрою, що заявляється, є наступні ознаки: - пристрій захисту по вихідному струму містить вузол мостового випрямляча, вхід якого з'єднаний з виходом трансформатора струму, а ви хід вузла випрямляча з'єднаний із входом вузла, що інвертує, порівняння й установки порога захисту, що представляє собою компаратор, виконаний на операційному підсилювачі, прямий вхід якого з'єднаний із движком потенціометра резистивного подільника напруги, а вихід з'єднаний із входом «S» вузла пам'яті, вхід «R» якого з'єднаний з вузлом установки схеми в нуль, а прямої вихід вузла пам'яті з'єднаний зі схемою імпульсного стабілізатора, а інверсний вихід вузла пам'яті з'єднаний з вузлом індикації «перевантаження», виконаного на транзисторному підсилювальному каскаді зі світлодіодним індикатором, причому вузол пам'яті виконаний на чотирьох логічних елементах «І», а вузол установки схеми в нуль виконаний на послідовно з'єднаних резисторі і конденсаторі, середня крапка яких підключена до входу «R» вузла пам'яті; - пристрій захисту по вхідному струму і перевищенню вихідної напруги містить датчик струму з транзистором захисту по струму, вузол порівняння, вузол пам'яті і вихідний вузол, причому вихід вузла порівняння підключений з S-входу вузла пам'яті, до R-входу якого підключений RC-ланцюжок установки в нуль вузла пам'яті, а вихід вузла пам'яті з'єднаний з вихідним вузлом, крім того, вузол порівняння виконаний на транзисторі, база якого через резистор з'єднана з виходом стабілізатора напруги, а колектор з'єднаний с першим входом логічного елемента «І», другий вхід якого з'єднаний з колектором транзистора захисту по стр уму, при цьому вихід логічного елемента «І» через інвертор з'єднаний з S-входом вузла пам'яті, а вузол пам'яті виконаний на двох логічних елементах «І» у вигляді RS-тригера, при цьому вихідний вузол виконаний на двокаскадному транзисторному підсилювачі, вхід якого з'єднаний з виходом вузла пам'яті, а вихід - з базою регулюючого транзистора попереднього стабілізатора напруги; - попередній стабілізатор напруги містить регулюючий і керуючий транзистори, L-C-VD-фільтр, вузол керування, при цьому регулюючий транзистор виконаний у вигляді двох складених транзисторів, причому в базовий ланцюг вихідного транзистора включений струмообмежувальний резистор, а вузол керування виконаний у вигляді компаратора, прямий вхід якого з'єднаний з резистивним дільником, включеним у вихідний ланцюг пристрою, у яку також включений параметричний стабілізатор напруги, підключений до входу компаратора, що інвертує, ви хід якого через керуючий транзистор підключений до бази регулюючого транзистора; - силовий перетворювач виконаний за мостовою схемою і містить двотактний транзисторний регульований перетворювач із силовим вихідним трансформатором, причому входи попереднього двотранзисторного підсилювача з'єднані зі схемою керування, а виходи навантажені на бази силових транзисторів перетворювача через проміжний трансформатор, причому двотактний транзисторний регульований перетворювач виконаний за мостовою схемою на чотирьох силових транзисторах, ланцюзі емітер-база яких зашунтовані діодами, а в базові ланцюги включені струмообмежувальні резистори, при цьому в колекторні ланцюги двох пар силових транзисторів включена первинна обмотка силового трансформатора; - блок мостових випрямлячів містить вісьмох силових мостових випрямлячів з фільтрами, що згладжують, на дроселях і конденсаторах і малопотужний мостовий випрямляч із дроселем, інтегральним стабілізатором напруги і конденсаторним фільтром. Між суттєвими ознаками винаходу, що заявляється, і те хнічним результатом, якій досягається, існує наступний причинно-наслідковий зв'язок. Дійсно, нова схемотехніка пропонованого імпульсного стабілізатора напруги в порівнянні з прототипом має більш могутню схему двотактного регульованого силового перетворювача, виконаного за мостовою схемою, на вході якого встановлений попередній підсилювач із проміжним трансформатором, що дозволяє значно збільшити струм навантаження, а, отже, і вихідну потужність пристрою. Крім того, у пристрої, що заявляється, мається можливість відключення формувача імпульсів керування при надходженні сигналу «перевантаження» від пристрою захисту по вихідному струму, що розширює функціональні можливості імпульсного стабілізатора. А наявність пристрою захисту по вхідному струм у і перевищенню вихідної напруги дозволяє захистити попередній стабілізатор і підсилювач потужності імпульсного стабілізатора від перевантаження по струму і від пробою могутніх транзисторів при перевищенні заданого рівня вихідної напруги. Суть пристрою, що заявляється, пояснюється кресленнями. На фіг.1 зображена функціональна схема пристрою з блоком 7 (блок мостових випрямлячів); на фіг.2 показана принципова електрична схема блока 1 (пристрій керування); на фіг.3 зображена принципова електрична схема блока 2 (пристрій захисту по ви хідному струм у); на фіг.4 показані принципові електричні схеми блоків 3 (попередній підсилювач) і 4 (підсилювач потужності); на фіг.5 зображена принципова електрична схема блока 6 (пристрій захисту по вхідному струм у і перевищенню вихідної напруги); на фіг.6 показана принципова електрична схема блока 5 (попередній стабілізатор напруги), на фіг.7 показані три графіки напруг, що є присутнім на обмотках трансформатора TV1: на первинній обмотці 1-2 (U1), на вторинних обмотках 3-4 і 9-10 (U2), а також на вторинних обмотках 5-6 і 7-8 (U3). Розглянемо склад і роботу кожного блока імпульсного стабілізатора, що заявляється, причому нумерація елементів кожного блока виконана незалежної від нумерації інших елементів інших блоків. Блок 1 - пристрій керування . Структурна схема блока 1 складається з функціонального генератора (далі по тексту - ФГ) 1, формувача імпульсів (формувача модульованих імпульсів керування, далі по тексту - ФМІК) 2, перетворювача зворотного зв'язку (далі по тексту - ПЗЗ) 3. ФГ 1 складається з генератора трикутних імпульсів 4 і генератори прямокутних імпульсів 5. ФГ1 забезпечує інші вузли пристрою, що заявляється, трикутними імпульсами (для роботи ПЗЗ 3 широтно-імпульсного модулятора) і прямокутними імпульсами, синхронними з трикутними імпульсами, для роботи тригера ФМІК 2. Синхронний збіг тривалості трикутних імпульсів з періодом прямокутних імпульсів дає можливість розділити імпульси керування транзисторами вихідного каскаду підсилювача потужності (блок 4). ФГ 1 є замкнутою релаксаційною системою, що складається з інтегратора DA 1-1 і компаратора DA 1-2. Постійна часу інтегратора і, отже, частота генерованих коливань залежать від ємності конденсатора С1, включеного в ланцюг негативного зворотного зв'язку. Напруга з виходу інтегратора DA 1-1 подається на вхід двополярного компаратора DA 1-2 через резистор R3 і, по досягненні порога спрацьовування DA 1-2, полярність напруги на виході компаратора DA 1-2 змінюється на протилежну, і цикл повторюється. Плавне регулювання частоти здійснюється резистором R 5. Отже, якщо на виході компаратора DA 1-2 є присутнім позитивна напівхвиля, то на ви ході інтегратора DA 1-1 - наростання фронту трикутного імпульсу напруги, а при переключенні компаратора DA 1-2 - на виході інтегратора DA 1-1 є присутнім негативний спад трикутного імпульсу. ФМІК 2 складається з тригера б і схеми збігу 7. Перший вихід ФГ 1 з'єднаний з першим входом ФМІК 2, виходи якого з'єднані з входами попереднього підсилювача (блок 3). Напруга зворотного зв'язку – Uз.з. - із вторинної обмотки вихідного трансформатора TV2 надходить на перший вхід ПЗЗ 3, др угий вхід якого з'єднаний з виходом генератора трикутних імпульсів 4. Вихід ПЗЗ 3 з'єднаний із другим входом ФМІК 2. На третій вхід ФМІК 2 надходить керуюча напруга від блока токового захисту (блок 2), а через перемикач SA2 у положенні «Викл.» надходить стабілізована напруга, «відключаюча» керуючі сигнали від блока 2. ПЗЗ 3 включає випрямляч напруги зворотного зв'язку, що включає діодний міст VD2-VD5, дросель L1 і конденсатор С2, якій згладжує, що приводить до перетворення двополярного сигналу зворотного зв'язку від трансформатора струму ТС1 в однополярний сигнал, що надходить на інверсний вхід активного елемента ПЗЗ 3 -компаратора DA1-3, прямої вхід якого через резистор R6 з'єднаний з виходом генератора трикутної напруги D A1-1, а інверсний вхід з'єднаний у потенціометром R11, включеним у резисторний дільник напруги R10, R12, що з'єднаний з перемикаючим контактом перемикача режимів роботи SA1, що має два положення - «мережа» і «внутрішні споживачі». Трикутні імпульси, амплітуда яких стабільна, надходять через буферний резистор R 6 на прямий вхід DA1-3. Дільник еталонної напруги на резисторах R10 - R12 забезпечують такий коефіцієнт підсилення ПЗЗ 3 на DA 1-3, якій необхідний для регулювання коефіцієнта стабілізації імпульсного стабілізатора. Установка вихідної напруги імпульсного стабілізатора Uвих виробляється резистором R11. Вихід компаратора DA1-3 з'єднаний з першими входами логічних елементів DD3-2 і DD3-3 схеми збігу 7 ФМІК 2. Як мікросхеми підсумовуючої логіки (логічні елементи DD3-2 і DD3-3 схеми збігу 7 ФМІК 2), які виконує логічну функцію «І-НІ», використовують мікросхеми DD3-2 і DD3-3 (К561 ЛЕ 10 - трьох трьовходових логічного елемента «АБО-НІ»), що працюють у негативній логіці і реалізують функції «І-НІ». Це обумовлено з особливістю цих мікросхем, у яких при наявності логічної «І» на кожнім з її входів, на виході з'являється логічний «0», що приводить до режиму відсічення роботи вихідних транзисторів підсилювача потужності імпульсного стабілізатора, і, отже, охороняє ці силові транзистори від виходу з ладу. ФМІК 2 включає також тригер 6, виконаний на мікросхемі DD2, рахунковий вхід якого підключений до виходу генератора прямокутних імпульсів 5, а прямої вихід тригера 6 з'єднаний із третіми входами логічних елементів DD3-2 і DD3-3 схеми збігу 7 ФМІК 2, причому на DD3-3 подається прямий сигнал з виходу тригера 6, а на DD3-2 подається інверсний сигнал з виходу тригера 6 через інвертор на логічному елементі DD3-1. При цьому інвертор DD3-1 уведений для того, щоб виключити перешкоду, зв'язану з часом затримки переключення тригера 6. При цьому на другі входи логічних елементів DD3-2 і DD3-3 схеми збігу 7 ФМІК 2 надходить керуюча напруга з виходу блока 2 чи через перемикач SA2 подається постійна напруга +15 В від параметричного стабілізатора на резисторі R15 і стабілітроні VD1. Виходи логічних елементів DD3-2 і DD3-3 схеми збігу 7 ФМІК 2 з'єднані з входами попереднього підсилювача імпульсного стабілізатора (блок 5). Повний цикл формування трикутного імпульсу у ФГ 1 відбувається протягом одного періоду прямокутних імпульсів на виході компаратора DA 1-2. Для одержання двополярних імпульсів керування необхідно розділити на «2» частоту проходження імпульсів з виходу компаратора ФГ 1, щоб у кожен напівперіод отриманих прямокутних імпульсів синхронно входив один цикл трикутних імпульсів з виходу інтегратора DA 1-1 ФГ1. Для цього в схему ФМІК 2 уведений D-тригер DD 2 у режимі розподілу на «2». З виходу DD 2 прямокутні імпульси з частотою перетворення надходять на вхід мікросхеми DD 3, що виділяє імпульси керування позитивної і негативної полярності. Імпульси позитивної полярності формуються на елементі DD 3-3 шляхом підсумовування імпульсів 3 виходу ПЗЗ 3, що випливають кожні напівперіод частоти перетворення з позитивним напівперіодом частоти перетворення. Елемент DD 3-1 виконує роль інвертора. Інвертовані імпульси необхідні для виділення імпульсів негативної полярності. На виході DD 3-2 виходять негативні імпульси для негативної напівхвилі імпульсного стабілізатора. З виходу DD 3-3 знімають позитивні імпульси, модульовані по ширині для позитивних напівперіодів імпульсного стабілізатора. Блок 2 - пристрій захисту по вихідному стр уму - складається з наступних вузлів, на фіг.3 вони показані пунктирними лініями. 1. Вузол мостового випрямляча, складається з мостового випрямляча на діодах DV1-DV4, вхід перемінного струму якого підключений до виходу трансформатора струму ТТ 1, що контролює струм навантаження імпульсного стабілізатора напруги, а вихід навантажений на послідовно з'єднані резистори R1 і R2. 2. Вузол порівняння й установки порога захисту, виконаний на операційному підсилювачі DA1 і являє собою компаратор, прямий вхід з'єднаний із движком потенціометра R4, встановленого в послідовному ланцюзі з резисторами R3 і R5, а інверсний вхід компаратора з'єднаний із загальною крапкою з'єднання резисторів R1 і R2, при цьому вихід компаратора з'єднаний із входом «S» вузла пам'яті 4. 3. Вузол установки схеми в нуль, виконаний на послідовно з'єднаних резисторі R6 і конденсаторі С1, загальна крапка яких з'єднана з входом «R» вузла пам'яті 4. 4. Вузол пам'яті, виконаний на чотирьох логічних елементах «І» DD1-DD4, причому елементи DD1 і DD2 виконані у вигляді інверторів, а на елементах DD3 і DD4 реалізований «RS»-тригер з інверторами, при цьому вхід «R» вузла пам'я ті з'єднаний з вузлом 3, а вхід «S» з ви ходом вузла 2. Прямий вихід вузла пам'яті з'єднаний зі схемою імпульсного стабілізатора напруги, а інверсний вихід вузла пам'яті з'єднаний із входом вузла індикації «перевантаження» 5. 5. Вузол індикації «перевантаження», виконаний на транзисторному підсилювальному каскаді, що включає транзистор VT1 і резистори R8 і R9, навантаженням якого є світлодіодний індикатор VD1, включений послідовно з струмообмежувальним резистором R10. Блоки 3 і 4 - попередній підсилювач і мостовий підсилювач потужності. Блок 3 являє собою попередній двотранзисторний підсилювач на транзисторах VT1 і VT2, навантажений на первинну обмотку проміжного трансформатора TV1. Блок 4 являє собою мостовий підсилювач потужності на чотирьох транзисторах VT3 - VT6, базові ланцюги яких підключені через струмообмежувальні резистори R4-R7 до вторинного обмоткам проміжного трансформатора TV1, а переходи база-емітер транзисторів VT3 - VT6 зашунтовані діодами VD1-VD4, включеними в зворотному напрямку, стосовно відповідних переходів база-емітер транзисторів VT3 - VT6. Колекторні ланцюги транзисторів VT3 - VT6 навантажені на первинну обмотку силового вихідного трансформатора TV2. Постійна напруга U_=40-90В, що надходить із сонячних фотоелементів, міняється в залежності від освітленості і величина її не є постійної, тому цю постійну напругу попереднє стабілізують (блок 5). Основною задачею підсилювача потужності є посилення стабілізованої напруги з перетворювача нетрадиційного джерела до значення, необхідного для перетворення в квазісинусоїдальну напругу. До вторинних обмоток TV1 через базові резистори R4-R7 і діоди VD1-VD4 підключені транзистори VT3VT6. Колектори VT3 і VT4, VT5 і VT6 з'єднані між собою відповідно і підключені до первинної обмотки TV2. TV1, VD1-VD4, VT3-VT6, R4-R7 і первинна обмотка TV2 є елементами підсилювача потужності, зібраного за мостовою схемою. Вихід підсилювача потужності підключений до первинної обмотки силового трансформатора TV2. Блок 5 - попередній стабілізатор напруги. Блок 5 призначений для попередньої стабілізації напруги, що надходить на блоки 1-3 і 6, і має прецизійну схему керування, що дозволяє підтримувати ви хідну напругу з точністю до 0,1В. Причому застосування як регулюючий транзистор складеного транзистора - VT2, VT3 - дозволяє значно збільшити вихідн у потужністю попереднього стабілізатора. Крім того, блок 5 дозволяє відключити навантаження при надходженні сигналу «перевантаження» від пристрою захисту по вхідному стр уму чи при надходженні сигналу перевищення величини вихідної напруги (блок 6). Блок 5 - імпульсний послідовний стабілізатор понижуючого типу - відомий також як стабілізаторпереривач («чоппер»). Напруга постійного струму від нетрадиційного джерела напруги U ==40-90В перетвориться чоппером у стабілізовану напругу постійного струму 24В. Чопперна схема пристрою обрана тому, що вона володіє високим кпд (=85%) і стійко працює у великому інтервалі зміни вхідної напруги. При подачі на чопперну схему напруги постійного струму ключ на складених транзисторах VT2 і VT3 знаходиться в провідному стані і починає пропускати струм . Відбувається заряд конденсатора С1 струмом, що проходить через дросель L1, що накопичує енергію. При досягненні напруги, величина якої визначається пристроєм керування, реалізованого на мікросхемі DA1, ключ відключається і розриває ланцюг живлення. Тим самим закінчується період накачування енергії і починається період віддачі енергії, запасеної в дроселі L1 і конденсаторі С1 через діод VD1. При зниженні напруги на конденсаторі С1 до рівня, обумовленого пристроєм керування, ключ знову замикається і процес повторюється. Роль ключа виконують транзистори VT2 і VT3, що включені за схемою Дарлингтона, яка доповнена тим, що між емітером VT2 і базою VT3 включений резистор R4. Цей резистор виконує роль струмообмежувального резистора і захищає транзистор VT2 від пробою його переходу колектор-емітер, а транзистор VT3 - від пробою переходу база-емітер. Пристрій керування складається з елемента порівняння DA1, виконаного на прецизійній високочастотній мікросхемі 544 УД 2 А і високочастного транзистора КТ 605 AM (VT1). Мікросхема DA1 працює в режимі компаратора. Блок 6 - пристрій захисту по вхідному стр уму і перевищенню вихідної напруги. Блок 6 призначений для захисту попереднього стабілізатора напруги - блока 5 - від перевантаження по вхідному струм у і перевищенню вихідної напруги, 1 що, в остаточному підсумку, дозволяє мати інтегральний захист по вихідній потужності попереднього стабілізатора напруги. Пристрій складається з наступних функціональних вузлів і елементів: 1. Датчик струм у - виконаний на резисторі R2. 2. Транзистор захисту по струму - транзистор VT1, база якого через підстроєчний резистор R3 з'єднана з датчиком струму, а в колекторний ланцюг включене навантаження - резистор R4. 3. Вузол порівняння - виконаний на транзисторі VT2, база якого через резистор R7 з'єднана з виходом стабілізатора напруги, а колектор з'єднаний з першим входом логічного елемента «І» DD1-1, другий вхід якого з'єднаний з колектором транзистора захисту по стр уму VT1, при цьому ви хід логічного елемента «І» DD1-1 через інвертор DD1-2 з'єднаний з S-входом вузла пам'яті 4. 4. Вузол пам'яті - виконаний на двох логічних елементах «І» DD1-3, DD1-4 у вигляді RS-тригера. 5. RC-ланцюжок установки в нуль - виконаний на резисторі R9 і конденсаторі С2, що зашунтований резистором R8. Середня крапка з'єднання R9 і С2 з'єднана з R-входом вузла пам'яті. 6. Вихідний вузол - виконаний на двокаскадному транзисторному підсилювачі VT3 і VT4, вхід якого з'єднаний з виходом вузла пам'яті, а вихід - з базою регулюючого транзистора VT2 попередні стабілізатори напруги (блок 5). Блок 7 - блок мостових випрямлячів. Блок 7 містить вісьмох силових мостових випрямлячів МВ1-МВ8 з фільтрами, що згладжують, на дроселях L1-L8 і конденсаторах С1-С8 і малопотужний мостовий випрямляч із дроселем L9, інтегральним стабілізатором напруги DA1 і конденсаторним фільтром на конденсаторах С9 і С10. Усі мостові випрямлячі підключені до відповідних вторинних обмоток силового вихідного трансформатора TV2. На виході силових мостових випрямлячів МВ1-МВ8 присутні відповідно постійні відфільтровані і згладжені постійні напруги +60V, +111V, +159V, +189V, +210V, +225V, +234V і +240V. На виході малопотужного мостового випрямляча присутня постійна згладжена напруга +15V. Пристрій працює в такий спосіб. Робота блока 1. За допомогою перемикача SA1 вибирається один із двох можливих режимів роботи пристрою - у режимі перетворювача імпульсної постійної напруги в постійну напругу (перемикач SA1 знаходиться в положенні «мережа») чи в режимі імпульсного стабілізатора (перемикач SA1 знаходиться в положенні «внутрішні споживачі»). У режимі перетворювача імпульсної постійної напруги в постійну напругу за допомогою подільника R10R12 формуються імпульси «зі сходинкою», що необхідні для нормальної роботи силових транзисторів перетворювача квазісинусоїдальної напруги - далі по тексту ПКСН (умовно не показаний). Під час формування «сходинки» усі силові транзистори ПКСН працюють у режимі «відсічення», тобто відключені. В інших випадках силові транзистора по черзі попарно переключаються і вся напруга від НДХ перетвориться в напругу живлення ПКСН, величина якого буде залежати від вихідної напруги НДХ, при цьому воно буде змінюватися відповідно зміні напруги НДХ. У режимі імпульсного стабілізатора (перемикач SA1 знаходиться в положенні «внутрішні споживачі») через дільник R10-R12 випрямлена мостовим випрямлячем VD2-VD5 і відфільтрована фільтром L1 і конденсатором С2, напруга зворотного зв'язку керує величиною постійної напруги живлення ПКСН. При збільшенні постійної напруги від НДХ напруга живлення ПКСН падає і навпаки. Отже, джерело живлення переходить у режим стабілізації напруги живлення ПКСН. Для живлення ПКСН використовуються кілька постійних напруг, що утворять рівні квантування по напрузі для формування квазісинусоїдальної напруги. А тому що напруга зворотного зв'язку знімається з додаткової обмотки силового трансформатора, то в кожен визначений момент часу величина цієї напруги зворотного зв'язку відповідає напрузі даного рівню квантування. Таким чином, при замиканні перемикачем SA1 ланцюга зворотного зв'язку з вихідного трансформатора (умовно не показаний), напруга на виході джерела живлення стабілізується поза залежністю від зміни напруги на вході джерела, що забезпечує на виході перетворювача, до складу якого входить пристрій, що заявляється, квазісинусоїдальну напругу 220В 50Гц. А при роботі на мережу перемикач SA1 замикає ланцюг резисторів R10, R11, R12, що забезпечує формування сходинки, забезпечуючи безпечний режим роботи джерела, вихідна напруга якого залежить від зміни напруги на вході джерела - це забезпечує максимальну віддачу енергії в мережу 220В 50Гц. Прямокутні імпульси з виходу DA1-2 надходять на рахунковий вхід тригера DD2, що визначає по який з обмоток вихідного трансформатора TV2 піде струм. Логічні елементи DD3-2 і DD3-3 схеми збігу 7 ФМІК 2 забезпечують підсумовування імпульсів із тригера DD2 з імпульсами виходу компаратора DD1-3, що повторюються кожні півперіода. На компараторі DA1-3 трикутні імпульси з виходу генератора DA1-1 порівнюються з постійною напругою зворотного чи зв'язку з фіксованим рівнем формування сходинки. Якщо перемикач SA1 знаходиться в положенні «мережа», ця постійна напруга формує при підсумовуванні з трикутними імпульсами прямокутні негативні імпульси, що займають 90 % від тривалості трикутних імпульсів. Якщо перемикач SA1 знаходиться в положенні «внутрішні споживачі», то при напрузі виходу ПКСН 220В+10%, ці імпульси займають 50% від тривалості трикутних імпульсів, за умови, що напруга НДХ складає близько 65В. При зменшенні напруги від НДХ менш 65В зазначені прямокутні імпульси розширюються, отже, сигнал на відкривання вихідних транзисторів підсилювача потужності імпульсного стабілізатора присутній протягом більшого часу, що приводить до зростання напруги на виході імпульсного стабілізатора до норми, незважаючи на зменшення напруги від НДХ на вході імпульсного стабілізатора. При збільшенні напруги від НДХ більш 65 В зазначені прямокутні імпульси стають уже, отже, сигнал на відкривання вихідних транзисторів підсилювача потужності імпульсного стабілізатора присутній протягом меншого часу, що приводить до зменшення напруги на виході імпульсного стабілізатора до норми, незважаючи на збільшення напруги від НДХ на вході імпульсного стабілізатора. При замиканні перемикача SA 2 відключається силова частина ПКСН від НДХ, тобто при приєднанні до входів DD3-2 і DD3-3 напруги +15В, на їхніх ви ходах з'являється сигнал логічного нуля, що приводить до відключення вихідних транзисторів підсилювача потужності імпульсного стабілізатора, тобто ці транзистори будуть знаходитися в режимі відсічення. Імпульси керування з виходу логічних елементів DD3-2 і DD3-3 схеми збігу 7 ФМІК 2 надходять на входи попереднього підсилювача імпульсного стабілізатора (блок 3). При спрацьовуванні пристрою токового захисту, на другі входи логічних елементів DD3-2 і DD3-3 схеми збігу 7 ФМІК 2 надходить сигнал логічної одиниці, тим самим на виходах логічних елементів DD3-2 і DD3-3 установлюється сигнал логічного нуля і виключається попередній підсилювач імпульсного стабілізатора (блок 3). Робота блока 2. Напруга з вторинної обмотки трансформатора струму ТС1, включеного в первинну обмотку силового вихідного трансформатора TV2, і пропорційного струму силового ви хідного трансформатора подається на випрямляч VD1 - VD4. Напруга з VD1 - VD4 не фільтрується, тому що обрана швидкодіючий захист, а уведення фільтра приведе до інерційності і затримки часу включення захисту: t = R× C . Випрямлена напруга через дільник R1, R2 подається на інверсний вхід DA1, на прямий вхід якого подається через дільник на R3, R4, R5 стабілізована напруга з виходу попереднього стабілізатора (блок 3). На R4 виставляється рівень спрацьовування захисту по струм у. DA1 працює в режимі компаратора, з виходу якого сигнал подається на «RS»-тpигep DD1-DD4. Через тригер DD1- DD4 подається сигнал, що блокує, на схему керування імпульсного стабілізатора: з'являється «0» на виході DD3 і блокує роботу схеми керування імпульсного стабілізатора напруги. З виходу DD4 напруга подається на базу транзистора VT1, у ланцюг колектора якого включений світлодіод VD1 «перевантаження», що сигналізує про перевищення струму навантаження вище рівня припустимого значення. Робота блоків 3 і 4. Постійна вхідна напруга надходить на вхідні виводи імпульсного стабілізатора напруги, до складу якого входить пристрій, що заявляється, і стабілізується попереднім стабілізатором (блоком 5). При подачі напруги живлення схема керування імпульсним стабілізатором (блок 1) виробляє імпульси керування, модульовані по ширині за допомогою перетворювача зворотного зв'язку і широтно-імпульсного модулятора, що входить до складу блока 1. Ці імпульси надходять на попередній підсилювач на транзисторах VT1 і VT2, колектори яких навантажені на первинну обмотку проміжного трансформатора TV1. Транзистори VT1 і VT2 підсилюють позитивні і негативні імпульси, що надходять зі схеми керування, і керують роботою транзисторів підсилювача потужності імпульсного стабілізатора, зібраного за схемою мостового інвертора на транзисторах різної провідності VT3- VT6 і трансформаторі TV2. На фіг.7 показані графіки напруг на обмотках трансформатора TV1. При надходженні на бази транзисторів VT3 і VT5 позитивних імпульсів керування в моменти часу t2, t6 , і т.д., останні відкриваються і через первинну обмотку трансформатора TV2 протікає струм позитивної напівхвилі імпульсного стабілізатора напруги - від крапки 1 до крапки 2. У такий спосіб формується позитивна напівхвиля вихідної напруги імпульсного стабілізатора. У моменти часу t4 , t 8 і т.д. на бази транзисторів VT3 і VT5 надходять негативні імпульси керування, транзистори VT3 і VT5 закриті, але відкриваються діоди VD1, VD3 і стр ум протікає через них і, відповідно, через обмотки 3-4 і 9-10 трансформатора TV1 і резистори R4 і R6, при цьому діоди VD1, VD3 захищають переходи 6-е транзисторів VT3 і VT5 від зворотної напруги U2. При надходженні на базу транзисторів VT4 і VT6 позитивних імпульсів керування в моменти часу t4, t8 і т.д., останні відкриваються і через первинну обмотку трансформатора TV2 протікає струм негативної напівхвилі імпульсного стабілізатора напруги - від крапки 2 до крапки 1. У такий спосіб формується негативна напівхвиля ви хідної напруги імпульсного стабілізатора. У моменти часу t2, t 6 і т.д. на бази транзисторів VT4 і VT6 надходять негативні імпульси керування і вони закриті, але відкриваються діоди VD2, VD4 і струм протікає через них і, відповідно, через обмотки 5-6 і 7-8 трансформатора TV1 і резистори R5 і R7, при цьому діоди VD2, VD4 захищають переходи б-е транзисторів VT4 і VT6 від зворотної напруги U3. Отже, трансформатор TV2 працює в двотактному режимі, без підмагнічування, по повній петлі гістерезиса. Резистори R4-R7 - буферні - і служать для захисту переходів б-э могутні х транзисторів VT3-VT6. З вторинної обмотки трансформатора TV2 знімається вихідна напруга імпульсного стабілізатора напруги. Використання мостової схеми підсилювача потужності дозволяє одержати вихідну потужність понад 1квт. Робота блока 5. При включенні чопперної схеми в мережу постійного струму складений ключ VT2, VT3 відкритий зсувом на базу транзистора VT2 через резистор R1. Через дросель L1 заряджається конденсатор С1 і на інверсному вході мікросхеми DA1 з'являється напруга 12В, стабілізоване стабілітроном VD2 через баластовий резистор R7. На прямому вході мікросхеми DA1 ця напруга продовжує рости, величина його визначається резистивним дільником R8, R8, R10 і пропорційна напрузі на конденсаторі С1, тобто на виході чопперної схеми. Коли напруга на прямому вході DA1 перевищить значення напруги на його інверсному вході, на виході компаратора DA1 з'являється напруга, рівне напрузі на виході чопперної схеми. Ця напруга через дільник на резисторах R2, R3 відкриває транзистор VT1. База транзистора VT2 через відкритий транзистор VT1 з'єдн ується з загальним проводом, тому ключ на складених транзисторах VT2, VT3 переходить у замкнений стан і L-C-VD-фільтр відключається від мережі постійного струму. Енергія, запасена в дроселі L1 і конденсаторі С1, надходить у навантаження через розрядний діод VD1. Коли напруга на прямому вході компаратора DA1 стає нижче напруги на його інверсному вході, на виході компаратора з'являється потенціал загального проводу, закривається транзистор VT1 і знову починається процес накачування енергії і цикл повторюється. На виході чопперної схеми встановлюється постійна напруга величиною 24В, що підтримується з точністю до 0,1В при струмах навантаження більш 10А. Робота блока 6. Постійна напруга від нетрадиційного джерела живлення, зокрема, від сонячних батарей, величиною 4090В, подається на вхід пристрою. Ця напруга стабілізується параметричним стабілізатором на VD1 і резисторі R1, потім згладжується конденсатором С1. RC-ланцюжок установки в нуль, виконаної на резисторі R9 і конденсаторі С2, установлює по R-входу вузла пам'яті RS-тригер у ви хідній (нульовій) стан. Пристрій захисту по струм у працює в такий спосіб. Датчик струму, виконаний на резисторі R2, контролює величину струму, що протікає через пристрій. Якщо споживаний струм перевищує значення 0,5А, то транзистор VT1 починає відкриватися і на резисторі R4 з'являється негативний фронт, що надходить на вхід логічного елемента «І» DD1-1. На виході логічного елемента «І» DD1-1 з'являється позитивний фронт, що надходить на інвертор DD12, негативний фронт із виходу якого встановлює RS-тригер вузла пам'яті в одиничний стан. На виході RS-тригера, з'єднаному з вихідним вузлом з'являється напруга логічного нуля, що відкриває транзистори VT3 і VT4 вихідного вузла. Відкритий транзистор VT4 замикає базу складеного регулюючого транзистора імпульсного стабілізатора VT2 (блок 5) на нульову шину живлення, тим самим відключаючи його від навантаження. Для відновлення нормальної роботи блоків 5 і 6, необхідно відключити їх від живильної напруги, усун ути причину збільшення струму і знову включити напругу живлення. Пристрій захисту по перевищенню вихідної напруги стабілізатора напруги працює в такий спосіб. Якщо напруга на ви ході попереднього імпульсного стабілізатора - блок 5 - перевищить величину 30В, то через дільник напруги на резисторах R6 і R7 відкривається транзистор VT2 і на резисторі R5 з'являється негативний фронт, що надходить на вхід на вхід логічного елемента «І» DD1-1. На виході логічного елемента «І» DD1-1 з'являється позитивний фронт, що надходить на інвертор DD12, негативний фронт із виходу якого встановлює RS-тригер вузла пам'яті в одиничний стан. На виході RS-тригера, з'єднаному з вихідним вузлом, з'являється напруга логічного нуля, що відкриває транзистори VT3 і VT4 вихідного вузла. Відкритий транзистор VT4 замикає базу складеного регулюючого транзистора VT2 попередні імпульсні стабілізатори (блок 5) на нульову шин у живлення, тим самим відключаючи його від навантаження. Для відновлення нормальної роботи блоків 5 і 6, необхідно відключити їх від живильної напруги, усун ути причину збільшення вихідної напруги імпульсного стабілізатора і знову включити напругу живлення. Тому очевидно, що реалізація пристрою, що заявляється, дозволить вирішити задачу, поставлену в даному винаході - розробку нової схемотехніки імпульсного стабілізатора - з досягненням технічного результату - підвищенням навантажувальної здатності пристрою і розширенням функціональних можливостей імпульсного стабілізатора.

ДивитисяДодаткова інформація

Назва патенту англійськоюPulse voltage regulator proposed by bekirov e.a.

Автори англійськоюBekirov Eskender Alimovych

Назва патенту російськоюИмпульсный стабилизатор напряжения бекирова

Автори російськоюБекиров Эскендер Алимович

МПК / Мітки

МПК: H02M 7/00, H02M 3/335, G05F 1/56

Мітки: стабілізатор, бекірова, імпульсний

Код посилання

<a href="https://ua.patents.su/11-66525-impulsnijj-stabilizator-bekirova.html" target="_blank" rel="follow" title="База патентів України">Імпульсний стабілізатор бекірова</a>

Попередній патент: Імуностимулюючий препарат “амброфіт”, спосіб його виготовлення та застосування

Наступний патент: Вузол квантування за часом – 2

Випадковий патент: Топічна композиція, що містить рибний желатин