Спосіб перетворення інформації та пристрій для його здійснення

Номер патенту: 84125

Опубліковано: 25.09.2008

Автори: Ересско Олег, Ходаков Віктор Єгорович, Рабчевська Ксенія Василівна, Шаганян Сергій Миколайович, Цивільський Федір Миколайович, Лунегов Максім, Бараненко Роман Васильович, Корчевська Лілія Олександрівна, Пилипенко Микола Вадимович

Формула / Реферат

1. Спосіб перетворення інформації, при якому на підготовчому етапі генерують ключ, який на вирішальному етапі накладають на вихідну інформацію за заданим законом, а зворотне перетворення для одержання вихідного тексту виконують повторним генеруванням ключа, який накладають на перетворену інформацію за тим же законом, який відрізняється тим, що на підготовчому етапі з бітових елементів вихідної інформації і ключа дискретно формують масиви у вигляді тривимірних геометричних об'єктів

та

та  відповідно кожен із яких, принаймні один, із заданою дискретною орієнтацією в тривимірному просторі, причому всі елементи з дійсними значеннями просторового розподілу в системах координат

відповідно кожен із яких, принаймні один, із заданою дискретною орієнтацією в тривимірному просторі, причому всі елементи з дійсними значеннями просторового розподілу в системах координат ![]() ;

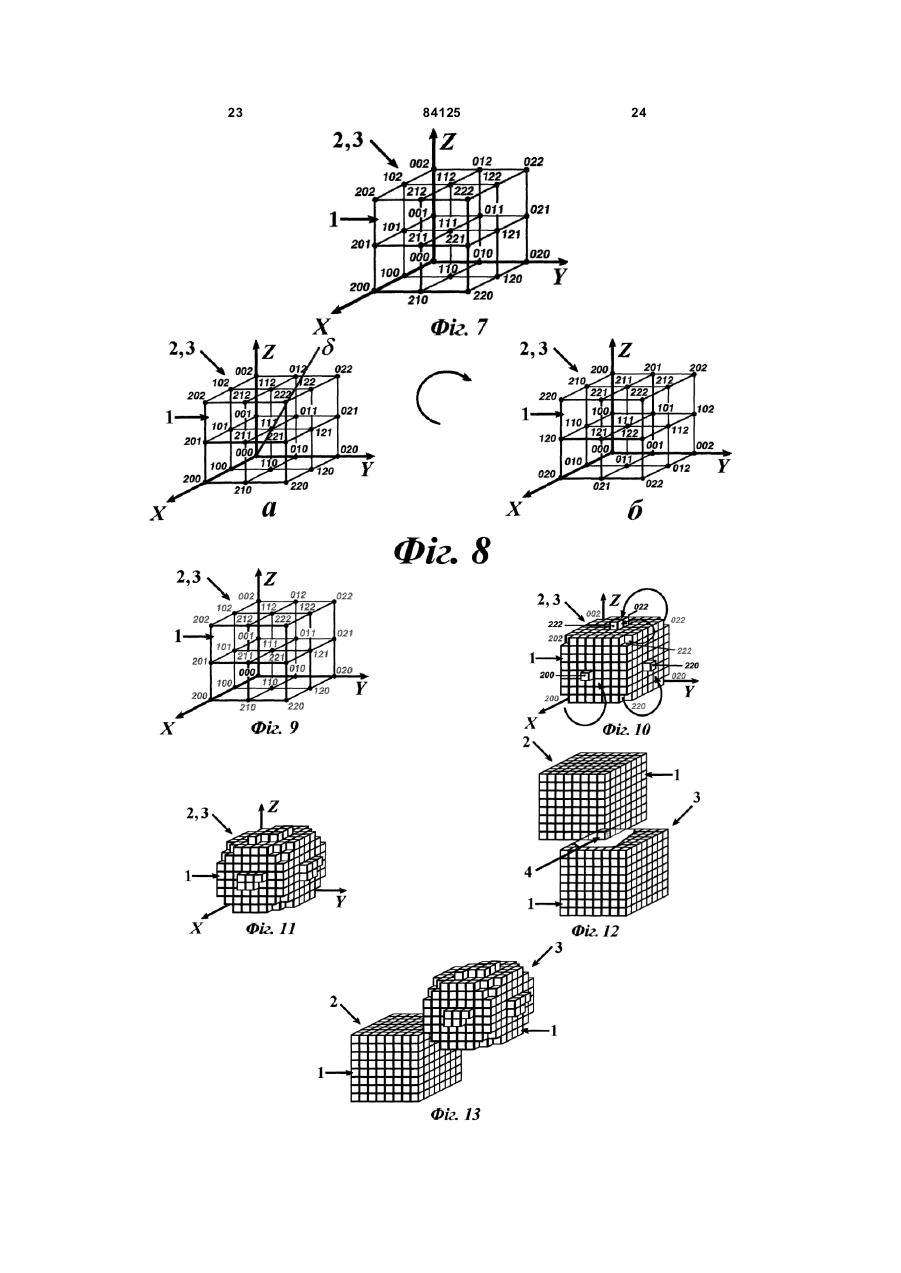

; ![]() , додатково містить проміжний етап, що передує вирішальному етапу - операції взаємодії між бітовими елементами зазначених тривимірних геометричних об'єктів, на зазначеному проміжному етапі виконують керовану дискретну зміну форми тривимірних геометричних об'єктів, їхніх напрямків орієнтації в тривимірній системі координат та/або їхнє обертання із можливістю керованого незалежного дискретного обертання кожного з зазначених тривимірних об'єктів навколо вершини осі координат одного з елементів зазначених об'єктів

, додатково містить проміжний етап, що передує вирішальному етапу - операції взаємодії між бітовими елементами зазначених тривимірних геометричних об'єктів, на зазначеному проміжному етапі виконують керовану дискретну зміну форми тривимірних геометричних об'єктів, їхніх напрямків орієнтації в тривимірній системі координат та/або їхнє обертання із можливістю керованого незалежного дискретного обертання кожного з зазначених тривимірних об'єктів навколо вершини осі координат одного з елементів зазначених об'єктів ![]() , де

, де ![]() - матриця значень місця розташування об'єкта відносно осі x,

- матриця значень місця розташування об'єкта відносно осі x, ![]() - матриця значень місця розташування об'єкта відносно осі у,

- матриця значень місця розташування об'єкта відносно осі у, ![]() - матриця значень місця розташування об'єкта відносно осі z із можливістю керованого незалежного дискретного обертання систем координат зазначених об'єктів та з можливістю керованої дискретної просторової зміни кроку переміщення і взаємодії їхніх елементів, причому керування дискретною зміною кроку виконують за додатковим параметром періодичності, наприклад,

- матриця значень місця розташування об'єкта відносно осі z із можливістю керованого незалежного дискретного обертання систем координат зазначених об'єктів та з можливістю керованої дискретної просторової зміни кроку переміщення і взаємодії їхніх елементів, причому керування дискретною зміною кроку виконують за додатковим параметром періодичності, наприклад, ![]() , де l – крок, t - параметр періодичності, причому

, де l – крок, t - параметр періодичності, причому ![]() та

та ![]() керування незалежним дискретним обертанням кожного з зазначених тривимірних об'єктів навколо осі координат виконують за додатковим параметром періодичності, наприклад,

керування незалежним дискретним обертанням кожного з зазначених тривимірних об'єктів навколо осі координат виконують за додатковим параметром періодичності, наприклад,  , де y - кут обертання об'єкта, s - керований показник величини кута обертання при його дійсних значеннях, тобто,

, де y - кут обертання об'єкта, s - керований показник величини кута обертання при його дійсних значеннях, тобто, ![]() , t - параметр періодичності, при цьому з можливістю керованого незалежного дискретного обертання деяких елементів тривимірних об'єктів навколо вершини осі координат одного з елементів зазначених об'єктів за параметром періодичності

, t - параметр періодичності, при цьому з можливістю керованого незалежного дискретного обертання деяких елементів тривимірних об'єктів навколо вершини осі координат одного з елементів зазначених об'єктів за параметром періодичності ![]() , де

, де ![]() та

та ![]() .

.

2. Спосіб за п. 1, який відрізняється тим, що дискретність значення кута обертання дорівнює принаймні 90°, тобто, ![]() .

.

3. Спосіб за п. 1, який відрізняється тим, що зміну форми зазначених об'єктів виконують методом перестановок.

4. Спосіб за п. 1, який відрізняється тим, що керовану дискретну зміну форми зазначених об'єктів виконують за формулою ангармонійного коливання.

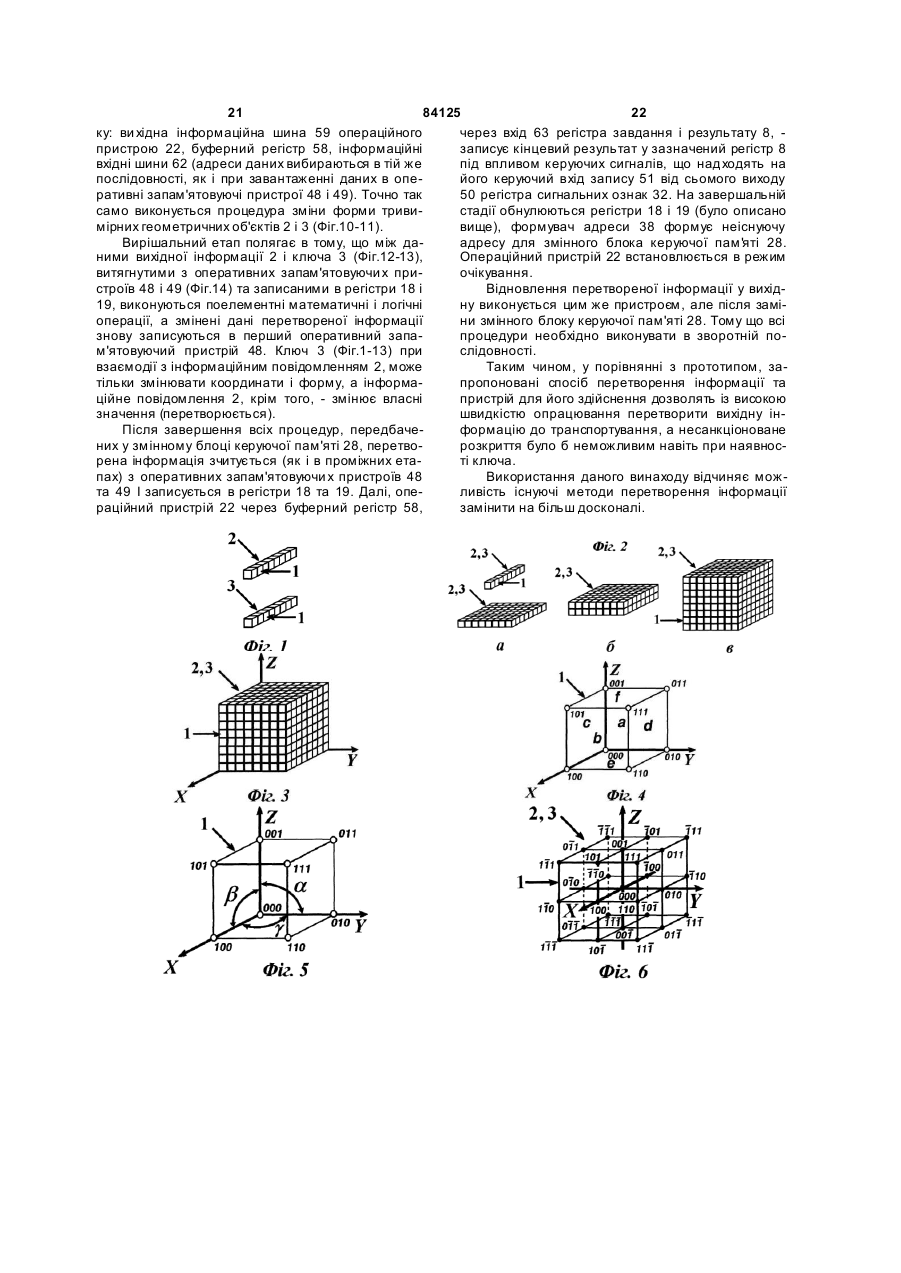

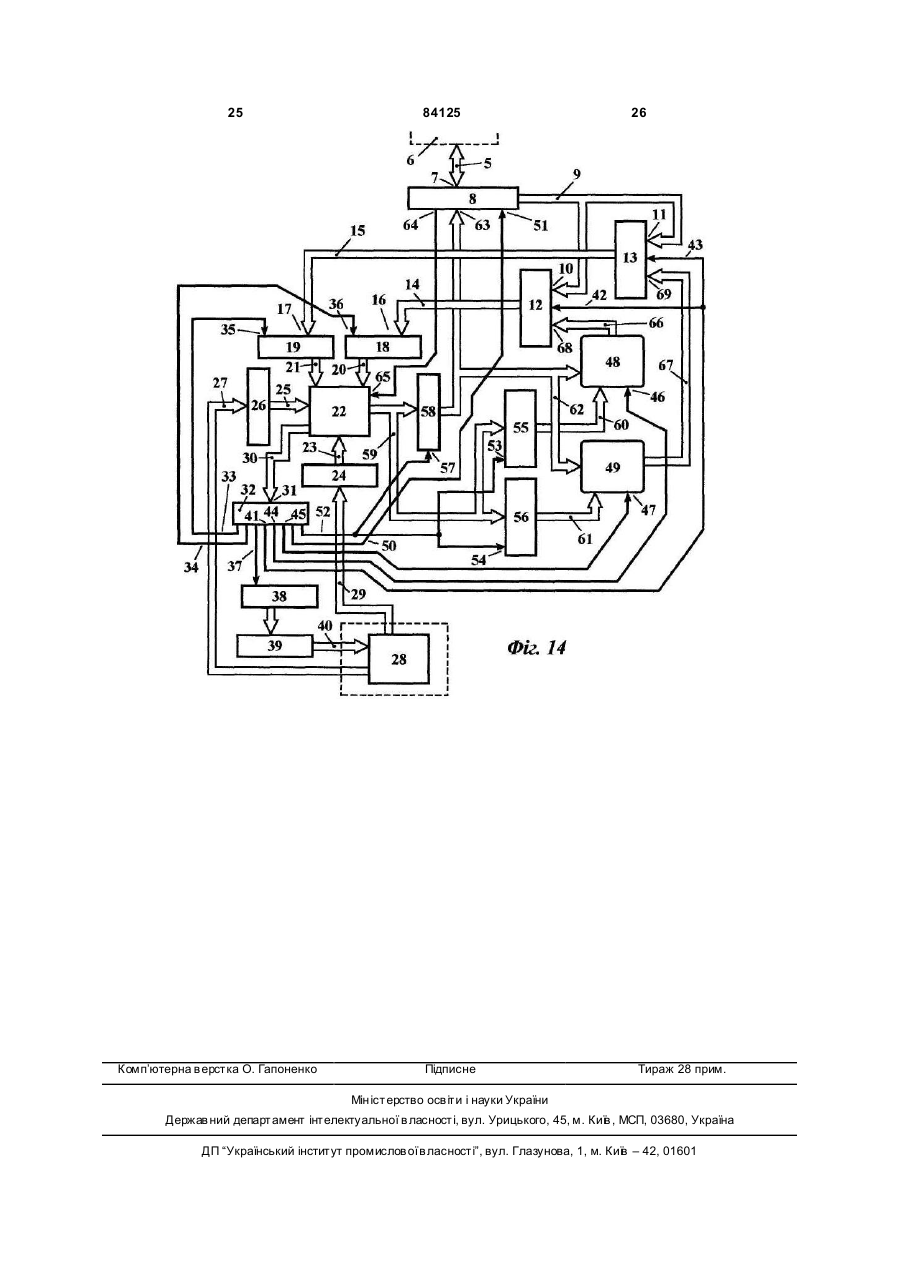

5. Пристрій перетворення інформації, який містить операційний пристрій, дві інформаційні вхідні шини якого зв'язані з виходами першого та другого інформаційних регістрів, вхідна шина керування зв'язана із виходом регістра керування, вхідна шина мікрокоманд через регістр мікрокоманд зв'язана із вихідною шиною блока керуючої пам'яті, виходом операційного пристрою є шина сигнальних ознак і вихідна інформаційна шина, виходом пристрою є основна шина процесора, який відрізняється тим, що додатково містить регістр сигнальних ознак, формувач адреси, регістр адреси, буферний регістр, перший і другий регістри фіксованих адрес, перший і другий мультиплексори, перший і другий оперативні запам'ятовуючі пристрої, регістр завдання і результату, зазначені дві інформаційні вхідні шини операційного пристрою виконані у вигляді інформаційного регістра та регістра ключа, відповідно, зазначена основна шина процесора виконана у вигляді двонаправленої шини обчислювальної системи, зазначений блок керуючої пам'яті виконаний у вигляді змінного блока керуючої пам'яті, вихідна шина якого виконана у вигляді першої вихідної шини, зазначена шина сигнальних ознак зв'язана з входом регістра сигнальних ознак, перший вихід якого зв'язаний із керуючим входом регістра ключа, другий вихід - із керуючим входом інформаційного регістра, третій вихід - із керуючим входом формувача адреси, четвертий вихід - із керуючими входами першого і другого мультиплексорів, п'ятий і шостий виходи - із керуючими входами запис/зчитування першого і другого оперативних запам'ятовуючих пристроїв, відповідно, сьомий вихід - із керуючим входом запису регістра завдання і результату, восьмий вихід - із керуючими входами першого і другого регістрів фіксованих адрес і буферного регістра, вхід зазначеного регістра керування зв'язаний із другою вихідною шиною змінного блока керуючої пам'яті, вхідна шина якого зв'язана через регістр адреси з виходом формувача адреси, зазначена вихідна інформаційна шина операційного пристрою зв'язана із входами буферного регістра і першого та другого регістрів фіксованих адрес, вихідні шини яких зв'язані з адресними вхідними шинами першого та другого оперативних запам'ятовуючих пристроїв, відповідно, інформаційні вхідні шини яких зв'язані з виходом буферного регістра та із входом регістра завдання і результату, сигнальний вихід готовності даних якого зв'язаний з аналогічним входом операційного пристрою, інформаційні вихідні шини першого і другого запам'ятовуючих оперативних пристроїв зв'язані з першими входами першого і другого мультиплексорів, відповідно, другі входи яких зв'язані з вихідною шиною регістра завдання і результату, вихідні шини першого і другого мультиплексорів зв'язані з входами інформаційного регістра та регістра ключа, відповідно, а шинний двонаправлений вхід/вихід регістра завдання і результату зв'язаний із двонаправленою шиною обчислювальної системи, входом і виходом пристрою є двонаправлена шина обчислювальної системи.

6. Пристрій за п. 5, який відрізняється тим, що, операційний пристрій виконаний у вигляді мікропроцесорного пристрою.

7. Пристрій за п. 5, який відрізняється тим, що двонаправлена шина обчислювальної системи виконана у вигляді СОМ порту за стандартом RS-232C.

8. Пристрій за п. 5, який відрізняється тим, що двонаправлена шина обчислювальної системи виконана у вигляді універсального послідовного USB порту.

9. Пристрій за п. 5, який відрізняється тим, що двонаправлена шина обчислювальної системи виконана у вигляді інтерфейсу АТА.

10. Пристрій за п. 5, який відрізняється тим, що двонаправлена шина обчислювальної системи виконана у вигляді інтерфейсу Centronics - IEEE-1284 із специфікацією режимів LPT порту.

11. Пристрій за п. 5, який відрізняється тим, що, двонаправлена шина обчислювальної системи виконана у вигляді інтерфейсу IrDA.

12. Пристрій за п. 5, який відрізняється тим, що, змінний блок керуючої пам'яті виконаний у вигляді постійного запам'ятовуючого пристрою, або перепрограмуючого запам'ятовуючого пристрою.

Текст

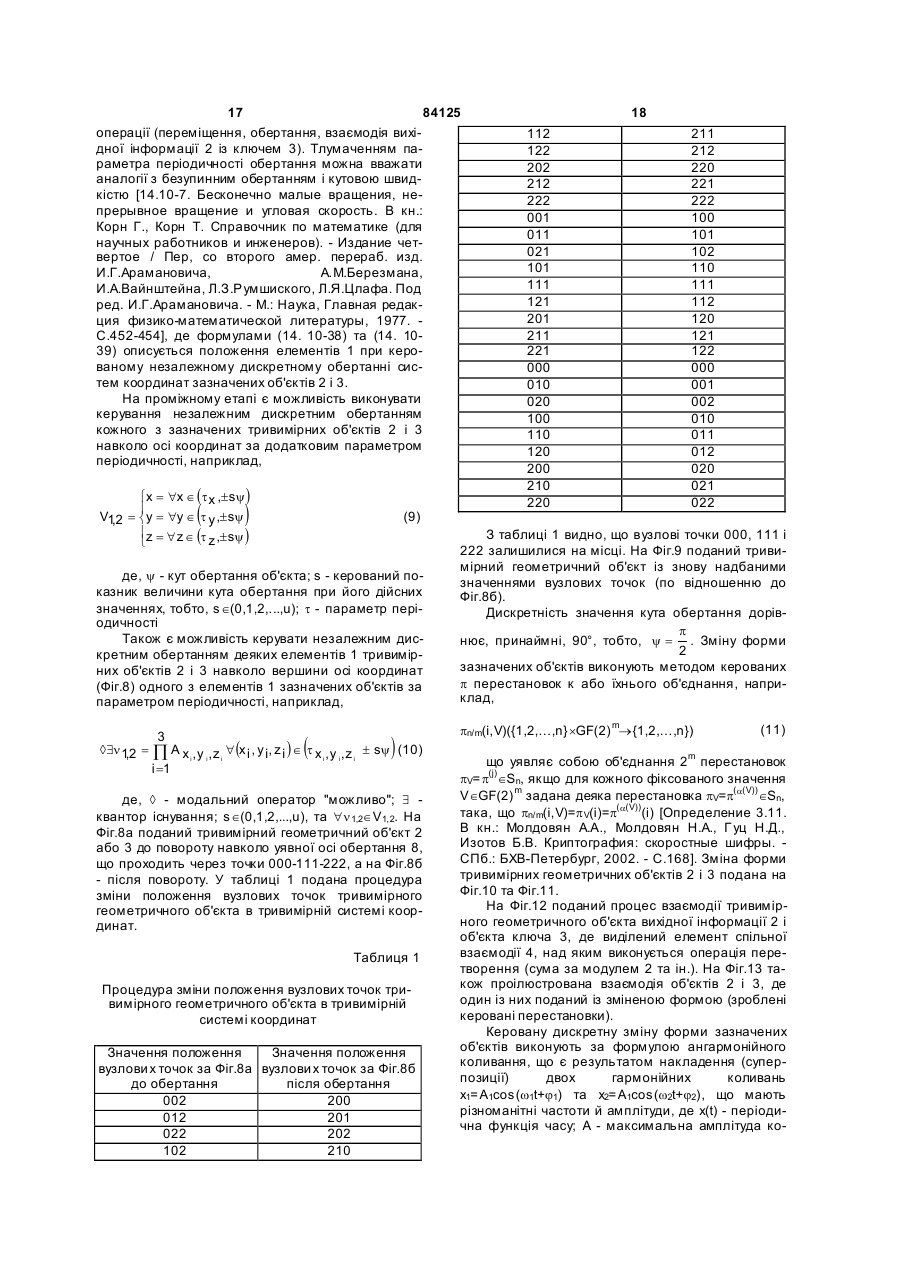

1. Спосіб перетворення інформації, при якому на підготовчому етапі генерують ключ, який на вирішальному етапі накладають на вихідну інформацію за заданим законом, а зворотне перетворення для одержання вихідного тексту виконують повторним генеруванням ключа, який накладають на перетворену інформацію за тим же законом, який відрізняється тим, що на підготовчому етапі з бітових елементів вихідної інформації і ключа дискретно формують масиви у вигляді тривимірних геометричних об'єктів ìx = x1, x 2 ,..., x g ï ï V1 = íy = (y1, y 2,..., yh ) ïz = (z , z ,..., z ) ï 1 2 k î та ì x' = (x 1, x 2 ,..., x m ) ï V2 = í y' = y1, y 2 ,..., y q ï îz' = (z1, z2 ,..., z r ) відповідно кожен із яких, принаймні один, із заданою дискретною орієнтацією в тривимірному просторі, причому всі елементи з дійсними значеннями просторового розподілу в системах координат "i Î { ,12,..., w} ; w ® max{g, h, k, m, q, r } , додатково 0 , містить проміжний етап, що передує вирішальному 2 3 84125 4 фіксованих адрес і буферного регістра, вхід зазна3 ченого регістра керування зв'язаний із другою виà$n1,2 = Õ A x i , y i , z i "(x i, yi , z i ) Î t x i , y i , z i ± sy , хідною шиною змінного блока керуючої пам'яті, i=1 вхідна шина якого зв'язана через регістр адреси з де s Î (0,12,..., u) та " n1 2 Î V1 2 . , , , виходом формувача адреси, зазначена вихідна 2. Спосіб за п. 1, який відрізняється тим, що дисінформаційна шина операційного пристрою зв'язакретність значення кута обертання дорівнює прина із входами буферного регістра і першого та p другого регістрів фіксованих адрес, вихідні шини наймні 90°, тобто, y = . яких зв'язані з адресними вхідними шинами пер2 шого та другого оперативних запам'ятовуючих 3. Спосіб за п. 1, який відрізняється тим, що зміну пристроїв, відповідно, інформаційні вхідні шини форми зазначених об'єктів виконують методом яких зв'язані з виходом буферного регістра та із перестановок. входом регістра завдання і результату, сигнальний 4. Спосіб за п. 1, який відрізняється тим, що кевихід готовності даних якого зв'язаний з аналогічровану дискретну зміну форми зазначених об'єктів ним входом операційного пристрою, інформаційні виконують за формулою ангармонійного коливанвихідні шини першого і другого запам'ятовуючих ня. оперативних пристроїв зв'язані з першими входа5. Пристрій перетворення інформації, який містить ми першого і другого мультиплексорів, відповідно, операційний пристрій, дві інформаційні вхідні шини другі входи яких зв'язані з вихідною шиною регістякого зв'язані з виходами першого та другого інра завдання і результату, ви хідні шини першого і формаційних регістрів, вхідна шина керування другого мультиплексорів зв'язані з входами інфозв'язана із виходом регістра керування, вхідна рмаційного регістра та регістра ключа, відповідно, шина мікрокоманд через регістр мікрокоманд зв'яа шинний двонаправлений вхід/ви хід регістра зазана із вихідною шиною блока керуючої пам'яті, вдання і результату зв'язаний із двонаправленою виходом операційного пристрою є шина сигнальшиною обчислювальної системи, входом і вихоних ознак і вихідна інформаційна шина, виходом дом пристрою є двонаправлена шина обчислювапристрою є основна шина процесора, який відрізльної системи. няється тим, що додатково містить регістр сигна6. Пристрій за п. 5, який відрізняється тим, що, льних ознак, формувач адреси, регістр адреси, операційний пристрій виконаний у вигляді мікробуферний регістр, перший і другий регістри фіксопроцесорного пристрою. ваних адрес, перший і другий мультиплексори, 7. Пристрій за п. 5, який відрізняється тим, що перший і другий оперативні запам'ятовуючі придвонаправлена шина обчислювальної системи строї, регістр завдання і результату, зазначені дві виконана у вигляді СОМ порту за стандартом RSінформаційні вхідні шини операційного пристрою 232C. виконані у вигляді інформаційного регістра та регі8. Пристрій за п. 5, який відрізняється тим, що стра ключа, відповідно, зазначена основна шина двонаправлена шина обчислювальної системи процесора виконана у вигляді двонаправленої виконана у вигляді універсального послідовного шини обчислювальної системи, зазначений блок USB порту. керуючої пам'яті виконаний у вигляді змінного бло9. Пристрій за п. 5, який відрізняється тим, що ка керуючої пам'яті, вихідна шина якого виконана у двонаправлена шина обчислювальної системи вигляді першої вихідної шини, зазначена шина виконана у вигляді інтерфейсу АТА. сигнальних ознак зв'язана з входом регістра сиг10. Пристрій за п. 5, який відрізняється тим, що нальних ознак, перший вихід якого зв'язаний із двонаправлена шина обчислювальної системи керуючим входом регістра ключа, другий ви хід - із виконана у вигляді інтерфейсу Centronics - IEEEкеруючим входом інформаційного регістра, третій 1284 із специфікацією режимів LPT порту. вихід - із керуючим входом формувача адреси, 11. Пристрій за п. 5, який відрізняється тим, що, четвертий вихід - із керуючими входами першого і двонаправлена шина обчислювальної системи другого мультиплексорів, п'ятий і шостий виходи виконана у вигляді інтерфейсу IrD A. із керуючими входами запис/зчитування першого і 12. Пристрій за п. 5, який відрізняється тим, що, другого оперативних запам'ятовуючих пристроїв, змінний блок керуючої пам'яті виконаний у вигляді відповідно, сьомий вихід - із керуючим входом запостійного запам'ятовуючого пристрою, або перепису регістра завдання і результату, восьмий вихід програмуючого запам'ятовуючого пристрою. - із керуючими входами першого і другого регістрів ( ) Винахід відноситься до методів перетворення коду, у якому інформація подана заданою послідовністю цифр або чисел, у код, де та ж інформація подана цифрами або числами, відмінними від заданої шляхом кодування за допомогою кодового слова, вираженого цифрами або числами; і може бути використаний при побудові систем опрацювання інформації. Відомий спосіб перетворення вихідної інформації в ши фрований текст методом Вернама [Защита программного обеспечения: Пер. с англ. / Д.Гроувер, Р.Сатер, Дж.Фипс и др. / Под редакцией Д.Гроувера. - M.: Мир, 1992. - C.100-103], [Соколов А.В., Степанюк О.М. Методы информационной защиты объектов и компьютерных сетей. - M.: ООО "Фирма "Издательство ACT"; СПб.: ООО "Издательство "Полигон", 2000. - ("Шпионские 5 84125 6 штучки"). - С.209-210.], у якому перетворення вихіпам'яті, виходом операційного пристрою є шина дної інформації, поданої заданою двійковою посигнальних ознак, а вихідна інформаційна шина слідовністю, виконують побітним додаванням за зв'язана з основною шиною процесора. модулем 2 із набором двійкових ключів, а дешифНедоліком даного пристрою є неможливість рування у ви хідну інформацію виконують побітним одночасного високошвидкісного опрацювання зі додаванням за модулем 2 шифрованого тексту з складними комбінаційними операціями великих набором тих же двійкових ключів. масивів інформації для її перетворення. Недоліком зазначеного способу є необхідність Задачею винаходу є одержання способу перерівності довжини вихідної двійкової послідовності з творення інформації та пристрою для його здійсдовжиною набору двійкових ключів. нення, за допомогою яких можна було б із високою Цього недоліку позбавлений спосіб шифр ушвидкістю опрацювання перетворити вихідну інвання Віжинера [Раздел 2.12. Система шифроваформацію до транспортування, а несанкціоноване ния Вижинера. В кн.: Гундарь К.Ю., Г ундарь А.Ю., розкриття було б неможливим навіть при наявносЯнишевский Д.А. Защи та информации в компьюті ключа. терных системах. - K.: "Корнейчук", 2000. - С.30Поставлена задача вирішується тим, що спо32.], при якому, на підготовчому етапі, ключ кінцесіб перетворення інформації та пристрій для його вої довжини k=(k0, k1, ..., kn- 1) продовжують до нездійснення, при яких, на підготовчому етапі, генескінченої послідовності, повторюючи ланцюжок, у рують ключ, який, на вирішальному етапі, накларезультаті чого одержують робочий ключ K=(k0, k1, дають на вихідну інформацію за заданим законом, а зворотне перетворення для одержання вихідно..., k n-1, k n, k n+1, k n+2, ...), при Kj=k(j mod n), a 0£J

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod for transformation of information and device for embodiment of it

Автори англійськоюPylypenko Mykola Vadymovych, Khodakov Viktor Yehorovych, Eressko Oleg, NL); Lunegov Maksim, DE); Baranenko Roman Vasyliovych, Shahanian Serhii Mykolaiovych, Tsyvilskyi Fedir Mykolaiovych, Rabchevska Ksenia Vasylivna, Korchevska Liliya Oleksandrivna

Назва патенту російськоюМетод преобразования информации и устройство для его осуществления

Автори російськоюПилипенко Николай Вадимович, Ходаков Виктор Егорович, Ересско Олег, Лунегов Максим, Бараненко Роман Васильевич, Шаганян Сергей Николаевич, Цивильский Федор Николаевич, Рабчевская Ксения Васильевна, Корчевска Лилия Александровна

МПК / Мітки

МПК: H03M 7/46

Мітки: інформації, пристрій, здійснення, перетворення, спосіб

Код посилання

<a href="https://ua.patents.su/13-84125-sposib-peretvorennya-informaci-ta-pristrijj-dlya-jjogo-zdijjsnennya.html" target="_blank" rel="follow" title="База патентів України">Спосіб перетворення інформації та пристрій для його здійснення</a>

Попередній патент: Захищений від підробки папір, спосіб його виготовлення та цінний документ (варіанти), пристрій для виготовлення захищеного від підробки паперу та сітка папероробної машини

Наступний патент: Дріт конденсаторного сорту з більш високими міцністю на розрив і твердістю

Випадковий патент: Металотермічний реактор