Електронний запам’ятовуючий пристрій

Формула / Реферат

1. Електронний запам'ятовуючий пристрій, що містить електрично програмовані запам'ятовуючі комірки, адресну шину для адресування запам'ятовуючих комірок, а також керовану схему формування напруги програмування запам'ятовуючих комірок, який відрізняється тим, що він містить керований сигналом режиму контролю перемикальний пристрій (23), виконаний з можливістю такого з'єднання адресної шини (30) у режимі контролю зі схемою (22) формування напруги програмування, що поданими адресними бітами встановлена попередньо задана контрольна напруга програмування.

2. Електронний запам'ятовуючий пристрій за п.1, який відрізняється тим, що як контрольна напруга програмування є попередньо задана напруга, при якій бездефектні запам'ятовуючі комірки ще не можуть бути перепрограмовані.

3. Електронний запам'ятовуючий пристрій за п.1 або 2, який відрізняється тим, що запам'ятовуючі комірки є комірками ЕСППЗП (21).

4. Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що попередньо задана контрольна напруга програмування в режимі контролю встановлювана командою програмування.

5. Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що перемикальний пристрій є мультиплексором (23).

6. Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що схема (22) формування напруги програмування виконана з можливістю керування нею, а також тим, що в режимі контролю номінальне значення контрольної напруги програмування задане адресними бітами.

7. Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що використовувані у режимі контролю адресні біти мають вигляд складової однієї або кількох контрольних команд програмування, записаних у запам'ятовуючому пристрої і використовуваних в разі потреби.

Текст

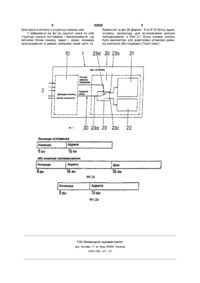

1 Елеісгронний запам'ятовуючий пристрій, що містить елеісгрично програмовані запам'ятовуючі комірки, адресну шину для адресування запам'ятовуючих комірок, а також керовану схему формування напруги програмування запам'ятовуючих комірок, який відрізняється тим, що він містить керований сигналом режиму контролю перемикальний пристрій (23), виконаний з можливістю такого з'єднання адресної шини (ЗО) у режимі контролю зі схемою (22) формування напруги програмування, що поданими адресними бітами встановлена попередньо задана контрольна напруга програмування 2 Електронний запам'ятовуючий пристрій за п 1 , який відрізняється тим, що як контрольна напруга програмування є попередньо задана напруга, при якій бездефектні запам'ятовуючі комірки ще не можуть бути перепрограмовані Винахід стосується електронного запам'ятовуючого пристрою, що містить електрично програмовані запам'ятовуючі комірки, адресну шину для адресування запам'ятовуючих комірок, а також керовану схему формування напруги програмування запам'ятовуючих комірок Електронні запам'ятовуючі пристрої такого виду реалізуються у загальному випадку у вигляді напівпровідникового чіпа, що містить, наприклад, модуль з програмованим постійним запам'ятовуючим пристроєм з електричним стиранням (ECnn3n=EEPROM) і схему формування напруги програмування, а також модуль зі схемами декодування і логіки, з яким з'єднані входи і виходи чіпа При цьому область пам'яті представляє собою власне запам'ятовуючий пристрій, що містить 3 Електронний запам'ятовуючий пристрій за п 1 або 2, який відрізняється тим, що запам'ятовуючі комірки є комірками ЕСППЗП (21) 4 Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що попередньо задана контрольна напруга програмування в режимі контролю встановлювана командою програмування 5 Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що перемикальний пристрій є мультиплексором (23) 6 Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що схема (22) формування напруги програмування виконана з можливістю керування нею, а також тим, що в режимі контролю номінальне значення контрольної напруги програмування задане адресними бітами 7 Електронний запам'ятовуючий пристрій за одним із попередніх пунктів, який відрізняється тим, що використовувані у режимі контролю адресні біти мають вигляд складової однієї або кількох контрольних команд програмування, записаних у запам'ятовуючому пристрої і використовуваних в разі потреби О 00 00 ю велику КІЛЬКІСТЬ запамятовуючих комірок Для програмування окремих ЕСППЗП-комірок на них необхідно подавати напругу програмування, що становить, наприклад, 20 В і є значно більшою, ніж напруга живлення, наприклад, 5 В Оптимальну напругу програмування отримують на ЧІПІ із напруги живлення за допомогою регульованої схеми формування напруги Із європейського патенту ЕР-А-0594294 відомий електронний запам'ятовуючий пристрій, що містить електрично програмовані комірки пам'яті, адресну шину для адресування комірок пам'яті і керовану схему для формування напруги програмування комірок пам'яті Після виготовлення такого напівпровідникового чіпа серед іншого має бути перевірений на ро 52828 ботоздатність ЕСППЗП Для цього передбачені спеціальні команди програмування, за допомогою яких програмується область пам'яті В ході цього тестування напругу програмування знижують до певного значення з метою перевірки здатності запам'ятовуючих комірок бути перепрограмованими при цій напрузі програмування Цю напругу програмування підводять ІЗЗОВНІ через додатковий контрольний контактний стовпчик на ЧІПІ Одначе цей контрольний контактний стовпчик для нормальної роботи чіпа не потрібен, а займає на ньому місце, яке не може бути використане для збільшення ємності пам'яті або збільшує розміри чіпа понад функціонально необхідні Тому в основі винаходу лежить задача розробки електронного запам'ятовуючого пристрою вказаного вище виду, в якому для контролю функціонування вказаний вище контрольний контактний стовпчик не є необхідним Згідно з п 1 формули винаходу ця задача вирішена тим, що у вказаному вище електронному запам'ятовуючому пристрої передбачено керований сигналом режиму контролю перемикальний пристрій, за допомогою якого в режимі контролю адресна шина може бути під'єднана до схеми формування напруги програмування таким чином, що підведеними адресними бітами може бути встановлена поперередньо задана напруга програмування Перевага цього рішення полягає в тому, що завдяки використанню адресних бітів у структурі команд чіпа для передачі заданого значення до схеми формування напруги програмування не потрібні додаткові витрати у декодері команд чи у схемі керуючої логіки Крім того, цінним є те, що в разі, коли у запам'ятовуючому пристрої записані критичні щодо безпеки дані, завдяки відсутності контрольного контактного стовпчика можливий зловмисник позбавлений точки втручання Команди контролю можуть бути постійно заблоковані у ЧІПІ, доки він не покине завод-виробник, завдяки чому маніпуляції більше неможливі Врешті, запам'ятовуючий пристрій згідно з винаходом потребує менше площі на ЧІПІ, завдяки чому порівняно з рівнем техніки при однаковій площі може бути збільшена ємність запам'ятовуючого пристрою або чіп такої ж ємності може мати менші розміри Додаткові пункти формули винаходу містять ВИГІДНІ удосконалення винаходу Контрольну напругу програмування вибирають такою, при якій запам'ятовуючі комірки ще не можуть бути перепрограмовані Запам'ятовуючі комірки утворюють переважно область пам'яті ЕСППЗП Одначе можливі також ІНШІ типи запам'ятовуючих пристроїв, у яких напруга програмування необхідна для зміни вмісту області пам'яті і має змінюватися з метою контролю Крім того, попередньо задана контрольна напруга програмування в режимі контролю може бути встановлена за допомогою команди програмування Перемикальним пристроєм може бути, зокрема, мультиплексор В загальному випадку керування схемою формування напруги програмування здійснюють таким чином, що в режимі контролю адресними бітами може бути передане задане значення контрольної напруги програмування , Інші подробиці, ознаки і переваги винаходу розкриті у наведеному нижче описі переважної форми виконання винаходу з використанням ілюстрації На них схематично зображено Фіг 1 Принципова схема такої форми виконання, Фіг 2а і 2Ь структура різних команд для подачі на схему згідно з фіг 1 Електронний запам'ятовуючий пристрій 1 із входами і виходами 2 містить згідно з фіг 1 перший модуль 10, другий модуль 20, а також адресну шину ЗО що з'єднує ці два модулі Перший модуль містить декодер команд і схеми керуючої логіки Крім того, з цим модулем з'єднані входи і виходи 2 запам'ятовуючого пристрою 1 Другий модуль 20 містить область 21 пам'яті з великою КІЛЬКІСТЮ окремих запам'ятовуючих комірок, регульовану схему 22 формування напруги програмування 22, а також мультиплексор 23, до входів 23а якого підведена адресна шина ЗО Мультиплексор 23 має два виходи 23Ь, 23с, один з яких з'єднаний з областю 21 пам'яті, а другий зі схемою 22 формування напруги програмування Мультиплексор 23 виконує функцію перемикача підведеної до його входу 23а адресної шини ЗО між областю 21 пам'яті і схемою 22 формування напруги програмування Перемикання здійснюється шляхом подачі на його керуючий вхід 23d сигналу режиму контролю Після виготовлення такого електронного запам'ятовуючого пристрою 1 необхідний контроль його роботоздатності Запам'ятовуючі комірки роботоздатного пристрою 1 можуть бути перепрограмовані лише при досягненні попередньо заданої напруги програмування і не можуть бути перепрограмовані при зниженні напруги програмування відносно вказаного значення В іншому разі існує небезпека ненавмисної зміни вмісту області пам'яті, наприклад, при підвищенні напруги живлення внаслідок непередбачуваних обставин В ході контролю напругу програмування знижують до певного значення, щоб перевірити, чи не перепрограмовуються ще запам'ятовуючі комірки при цій напрузі Оскільки В ХОДІ ЦЬОГО контролю перевіряються всі запам'ятовуючі комірки разом, їх адресування не потрібне Тому для проведення контролю на керуючий вхід 23d мультиплексора 23 подають сигнал режиму контролю, внаслідок чого адресна шина ЗО з'єднується з другим, зв'язаним зі схемою 22 формування напруги програмування виходом 23с мультиплексора 23 Після ЦЬОГО напругу програмування через адресну шину ЗО знижують до попередньо заданого значення, причому адресні біти безпосередньо діють на вузол керування схеми 22 формування напруги програмування, встановлюючи нове задане значення для зниженої напруги програмування Насамкінець мультиплексор 23 знову перемикають у робочий режим, в якому запам'ятовуючі комірки можуть бути перевірені стосовно їх здатності змінювати свій вміст Встановлення напруги програмування може бути просто втілене в структуру команд чіпа У зображеній на фіг 2а, ВІДОМІЙ самій по собі структурі команд зчитування і програмування, що включає блоки команд, адрес і даних, команда програмування в режимі контролю може мати зо 52828 6 бражений на фіг 2Ь формат Біти 8-15 блоку адрес служать, наприклад, для встановлення напруги програмування, а біти 0-7 блоку команд можуть бути використані для додаткових установок режиму контролю або ігноровані ("don't care") 2 ФІГ1 2 2 TOB "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)236-47-24

ДивитисяДодаткова інформація

Назва патенту англійськоюElectronic memory device

Назва патенту російськоюЭлектронное запоминающее устройство

МПК / Мітки

МПК: G11C 29/04

Мітки: пристрій, електронний, запам'ятовуючий

Код посилання

<a href="https://ua.patents.su/3-52828-elektronnijj-zapamyatovuyuchijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Електронний запам’ятовуючий пристрій</a>

Попередній патент: Засіб для з’єднання бурових штанг

Наступний патент: Гідроакустичний профілограф

Випадковий патент: Пристрій для регулювання струмів збудження тягових електродвигунів