Багаторозрядний пристрій множення чисел з плаваючою комою

Номер патенту: 19536

Опубліковано: 25.12.1997

Автори: Радкевич Олександр Іванович, Нагорний Леонід Якович, Сидорчук Олександр Дем'янович

Формула / Реферат

Многоразрядное устройство умножения чисел с плавающей запятой, содержащее регистр множимого, сумматор, регистр сдвига результата, регистры результата основного и вспомогательного, схему ИЛИ, блок управления, 64-х битовую шину мантиссы, отличающееся тем, что в него введены мультиплексор множителя, регистр множителя, блок анализа, блок сдвига, причем 64-х битовая шина мантиссы является входом регистра множимого, первым входом сумматора, первым входом мультиплексора множителя, выход которого соединен со входом регистра множителя, выход которого является первым входом блока сдвига и входом блока анализа, выход которого соединен со вторым входом блока управления и вторым входом блока сдвига, выход которого соединен со вторым входом мультиплексора множителя и первым входом блока управления, первый выход которого является третьим входом мультиплексора множителя, а второй выход соединен со вторым входом регистра сдвига результата, первый вход которого является выходом сумматора, второй вход которого соединен с выходом регистра множимого, выход регистра сдвига результата соединен со входом регистра результата основного и вспомогательного, выходы G, R и S которого являются входами схемы ИЛИ, выход которой является входом S регистра результата основного, выход регистра результата вспомогательного соединен 64-х битовой шиной мантиссы.

Текст

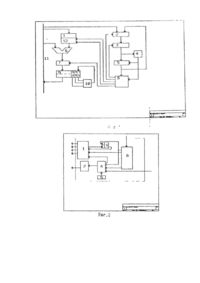

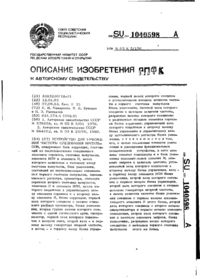

Изобретение относится к цифровой вычислительной технике и может быть использовано для выполнения операции умножения в арифметических сопроцессорах и специализированных процессорах. Известен процессор для обработки числовых данных [Патент США, №4.484.259]. позволяющий выполнять арифметические операции и трансцендентные функции над многоразрядными числовыми данными, содержащий сдвиговый регистр, регистр мультиплексор, блок управления мультиплексором, сумматор, сдвигатель результата, блок управления, регистры результата основного и вспомогательного, схему ИЛИ, шестидесятичетырех битовую шину мантиссы. В устройстве реализован метод анализа двух бит множителя, загружаемого в сдвиговый регистр за цикл частоты синхронизации. Недостаток прототипа заключается в низком быстродействии из-за того, что в каждом такте синхронизации множитель сдвигается только на два разряда и затем анализируется. Задачей изобретения является усовершенствование устройства, путем использования алгоритма анализа всего множителя за такт частоты синхронизации, чем достигается увеличение быстродействия. Выполнение поставленной задачи достигается тем, что в известное устройство умножения чисел с плавающей запятой, содержащее сумматор, правый вход которого является выходом регистра, вход которого подключен к 64-х битовой шине мантиссы и первому входу сумматора, выход которого соединен с первым входом регистра сдвига результата, выход которого соединен со входом регистра сдвига результата основного и вспомогательного, выход которого соединен с первым входом сумматора 64-х битовой шиной мантиссы введет мультиплексор множителя, регистр множителя, блок анализа и блок сдвигов, первый вход которого соединен с выходом регистра множителя и входом блока анализа, выход которого соединен со вторым входом блока управления и вторым входом блока сдвига, выход которого соединен со вторым входом мультиплексора множителя и первым входом блока управления, первый выход которого соединен с третьим входом мультиплексора множителя, а второй выход соединен со вторым входом регистра сдвига результата, первый вход мультиплексора множителя соединен с 64-х битовой шиной мантиссы. Предлагаемое устройство умножения чисел с плавающей запятой обладает существенным отличием по сравнению с известными техническими решениями, поскольку именно совокупность отличительных признаков: наличие блока анализа всего множителя и блока сдвигов на n разрядов их взаимосвязь между собой и известными признаками, присущими прототипу позволяют повысить быстродействие. Коме того, только совокупность отмеченных выше признаков с дополнительными признаками дает возможность повысить быстродействие, что невозможно осуществить с помощью прототипа и других выявленных аналогов. В научно-технической литературе не выявлено заявления совокупности новых признаков, что является доказательством соответствия технического решения критерию "существенные отличия". На фиг.1 приведена структурная схема предлагаемого устройства; на фиг,2 - функциональная схема блока микропрограммного управления. В таблице отражена работа блока управления при перемножении чисел как функция количества подряд идущих нулей или единиц и значения балансного триггера внутри схемы управления 8. Устройство содержит регистр множимого 1, мультиплексор множителя 2, регистр множителя 3, бок анализа 4, блок сдвига 5, сумматор 6, регистр сдвига результата 7, блок управления 8, регистры результата основного и вспомогательного 9, схему ИЛИ 10, шестидесятичетырехбитовую шину 11 мантиссы, мультиплексора множимого 12, причем 64-х битовая шина мантиссы 11 является входом регистра множимого 1, левым входом сумматора 6, первым входом мультиплексора множителя 2, выход которого соединен со входом регистра множителя 3, выход которого является первым входом блока сдвига 5 и входом блока анализа 4, выход которого соединен со вторым входом блока управления 8 и вторым входом блока сдвига 5, выход которого соединен со вторым входом мультиплексора множителя 2 и первым входом блока управления 8, первый выход которого является вторым входом регистра множителя 3, второй выход соединен с третьим входом мультиплексора множителя 2, третий и четвертый выходы являются вторым и третьим входами мультиплексора множимого 12 соответственно, пятый выход является вторым входом регистра сдвига результата 7, первый вход которого является выходом сумматора 6, правый вход которого соединен с выходом мультиплексора множимого12, а выход регистра сдвига результата 7 соединен со входом регистра результата основного и вспомогательного 9, выходы G, R и S которого являются входами схемы ИЛИ 10, выход которой является входом S регистра результата основного и вспомогательного 9, выход которого соединен с 64-х битовой шиной мантиссы 11. Устройство работает следующим образом. Множитель перед выполнением операции умножения нормализован и поступает на первый вход мультиплексора множителя 2 из 64-х битовой шины мантиссы 11. Далее с выхода мультиплексора 2 множитель поступает на вход регистра множителя 3 выход которого соединен со входом блока анализа 4 и блока сдвига 5. Блок анализа 4 вырабатывает код количества сдвигов множителя на необходимое количество разрядов согласно таблице. Если в первом разряде множителя нуль, то производится анализ количества подряд идущих нулей, если единица, то производится анализ количества подряд идущих единиц. Блоком сдвига 5 множитель сдвигается вправо на необходимое количество разрядов, согласно полученному коду из блока анализа 4 и поступает на второй вход мультиплексора множителя 2. Множимое поступает на вход регистра множимого 1 из шины мантиссы 11, с выхода которого поступает на правый вход сумматора 6. Рассмотрим процедуру умножения на примере 64-х разрядного множителя 111111111111110000000000000000011 111111000000000 1111111110000000. В первом цикле операции умножения n=7, что соответствует семи нулям с права в множителе, затем подряд идут 9 единиц и во втором цикле n=9 (девять) и т.д. Таким образом операции умножения произвольного множителя выполнится за 6 циклов, а не за 34 как в прототипе. Удвоенное множимое получается путем сдвига множимого на один разряд вправо. Суммирование либо вычитание множимого выполняется сумматором. В основу функционирования устройства заложен алгоритм умножения основанный: на анализе всего множителя. Суть алгоритма заключается в следующем: подсчитывается количество подряд идущих нулей либо единиц начиная с младшего разряда. В начале выполнения операции начальное состояние равно нулю. Затем в зависимости от количества подряд идущих нулей либо единиц и начального состояния согласно таблице. Например, для множителя 111111111111110000000000000000011 1111110000000001111111110000000 младший разряд равен нулю, количество подряд идущих нулей справа равно n=7 1. Начальное состояние равно 0. Мы попадаем под условие строки 5 таблицы. Устройство управления передает управляющую информацию (см. строку 5 последний столбец) на сдвиг множителя и результата на семь разрядов вправо устанавливая при этом новое состояние в нуль. Множитель после сдвига равен 000000011111111111111000000000000000 0011111111000000000111111111 затем младший разряд равен 1 и количество подряд идущих единиц n=9 1. Предыдущее состояние 0. Согласно строки 7 таблицы 1 выдается управление на сдвиг множителя на 9 разрядов вправо, вычитание из результата множимого, сдвиг результата на 9 разрядов вправо и установка в единицу нового состояния и т.д. Предложенный алгоритм существенно отличается от алгоритма умножения основанном на пропуске такта суммирования при нулевом множителе. При многоразрядных избыточных вычислениях, особенно целочисленных, последовательности более двух разрядов подряд идущих нулей или подряд единиц, встречающихся в представлениях мантисс, приводят к сокращению количества циклов при выполнении операции умножения. Количество циклов выполнения операции умножения зависит от длины указанных выше последовательностей нулей или единиц. При представлении реальных целых чисел в форме с плавающей запятой в 64-х разрядной сетке мантиссы появляются длинные более сорока бит последовательности нулей, что более чем на 20 циклов сокращает количество циклов выполнения операции умножения по сравнению с прототипом. Вероятность появления в 64-х разрядной двоичной сетке таких последовательностей высокая, т.к. плотное распределение чередующихся нулей и единиц на 64 разрядную сетку возможно лишь гипотически. Блок управления 8 управляет последовательностью поступления операндов от блока к блоку посредством ПЗУ микрокоманд. Блок управления имеет следующие функциональные характеристики: - код операции на 6 разрядов; - адрес памяти микропрограмм на 8 разрядов; - выходы с тремя состояниями. Блок микропрограммного управления управляет обнулением регистров множимого, множителя, сумматора и регистра результата. Выборкой операндов множимого, множителя и занесением их в соответствующие регистры. Информация о состоянии триггера, содержимом разряда (0 или 1), количество разрядов (1) является входной для блока микрокода 1, на выходе которого а также счетчика сдвигов формируются сигналы на сдвиг множимого, множителя, операции сложения либо вычитания, занесения в регистр. Наличие всех нулей на входе дешифратора 6 кодируется в признак окончания операции умножения, при этом триггер и счетчик устанавливаются в исходное состояние. Блок управления содержит счетчик количества сдвигов, ПЗУ микрокоманд, регистр, генератор тактовых импульсов, дешифратор признака окончания операции умножения, балансный триггер. Счетчик сдвигов выполнен на двух микросхемах КР 1531 ИЕ 7, регистр - КР 580 ИР 82, ПЗУ - КР 556 РТ 5. Блок анализа представляет собой шифратор 64-х разрядного операнда множителя в 7-битовый, содержащий код количества сдвигов множителя в каждом такте частоты синхронизации. Блок анализе выполнен из восьми микросхем серии КР556РТ5, выходы которых включены параллельно.

ДивитисяДодаткова інформація

Автори англійськоюRadkevych Oleksandr Ivanovych

Автори російськоюРадкевич Александр Иванович

МПК / Мітки

МПК: G06F 7/40, G06F 7/483

Мітки: багаторозрядний, чисел, пристрій, комою, множення, плаваючою

Код посилання

<a href="https://ua.patents.su/4-19536-bagatorozryadnijj-pristrijj-mnozhennya-chisel-z-plavayuchoyu-komoyu.html" target="_blank" rel="follow" title="База патентів України">Багаторозрядний пристрій множення чисел з плаваючою комою</a>

Попередній патент: Вулик для двохматкового утримання бджіл

Наступний патент: Композиційний присадний матеріал для обробки металургійних розплавів

Випадковий патент: Електромагнітостатичний генератор