Мережний програмований контролер

Номер патенту: 37651

Опубліковано: 15.09.2003

Автори: Малиновський Михаїл Леонідович, Загарій Генадій Іванович, Фурман Ілля Олександрович

Формула / Реферат

Мережний програмований контролер, який містить блоки пам'яті станів та команд, схему порівняння та лічильник адреси, перший вхід якого є першим входом пристрою, вихід лічильника адреси є першим виходом пристрою та з'єднаний з адресними входами блоків пам'яті станів та команд, інформаційний вихід блока пам'яті станів підключений до першого входу схеми порівняння, другий вхід якої є другим входом пристрою, другим виходом якого є перший (інформаційний) вихід блока пам'яті команд, який відрізняється тим, що до нього введені блок пам'яті переходів, вузол логічного керування та логічний елемент "І", причому адресний вхід блока пам'яті переходів є третім входом пристрою, перший (інформаційний) вихід блока пам'яті переходів з'єднаний з першим входом лічильника адреси, другий та третій входи якого підключені відповідно до першого та другого виходів вузла логічного керування, перший вхід якого з'єднаний з другим виходом блока пам'яті переходів, другий та третій входи вузла логічного керування підключені відповідно до другого виходу блока пам'яті команд та до виходу логічного елемента "І", перший вхід якого є третім входом пристрою, другий вхід логічного елемента "І" з'єднаний з виходом схеми порівняння.

Текст

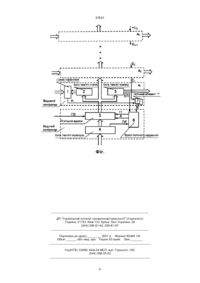

Мережний програмований контролер, який містить блоки пам'яті станів та команд, схему порівняння та лічильник адреси, перший вхід якого є першим входом пристрою, вихід лічильника адреси є першим виходом пристрою та з'єднаний з адресними входами блоків пам'яті станів та команд, інформаційний вихід блока пам'яті станів підключений до першого входу схеми порівняння, другий вхід якої є другим входом пристрою, другим вихо 37651 мереж на основі прототипу деякі блоки стають незадіяними (надмірними), крім того, у прототипі застосовується метод аналізу умов переходів, реалізація якого зв'язана з підвищеними апаратними витратами. В основу винаходу поставлено задачу вдосконалення мережного програмованого контролера шляхом введення до нього нових блоків та зв'язків, які забезпечують економічну схему компоновки контролерної мережі, а також реалізацію методу аналізу комбінацій умов переходів, яка потребує зменшених апаратних витрат. Реалізація поставленої задачі досягається тим, що у мережний програмований контролер, що містить блоки пам'яті станів та команд, схему порівняння та лічильник адреси, перший вхід якого є першим входом пристрою, вихід лічильника адреси є першим виходом пристрою та з'єднаний з адресними входами блоків пам'яті станів та команд, інформаційний вихід блока пам'яті станів підключений до першого входу схеми порівняння, другий вхід якої є другим входом пристрою, другим виходом якого є перший (інформаційний) вихід блока пам'яті команд, введені блок пам'яті переходів, вузол логічного керування та логічний елемент "І", причому адресний вхід блока пам'яті переходів є третім входом пристрою, перший (інформаційний) вихід блока пам'яті переходів з'єднаний з першим входом лічильника адреси, другий та третій входи якого підключені відповідно до першого та другого виходів вузла логічного керування, перший вхід якого з'єднаний з другим виходом блока пам'яті переходів, другий та третій входи вузла логічного керування підключені відповідно до другого ви ходу блока пам'яті команд та до виходу логічного елемента "І", перший вхід якого є третім входом пристрою, другий вхід логічного елемента "І" з'єднаний з виходом схеми порівняння. Введення вказаних відмінних ознак винаходу дозволяє усунути апаратну надмірність пристрою за рахунок застосування економічної схеми компоновки контролерних мереж, при якій контролерка мережа являє собою набір ведених контролерів, керованих одним ведучим контролером, а також ефективного методу аналізу комбінацій умов переходів, який потребує зменшених апаратних витрат. На фігурі наведена блок-схема запропонованого пристрою. Пристрій містить схему порівняння 1, блок 2 пам'яті станів, лічильник адреси 3, блок 4 пам'яті переходів, блок 5 пам'яті команд, вузол логічного керування 6 та логічний елемент "І" 7, причому перший вхід лічильника адреси 3 є першим входом пристрою, вихід лічильника адреси 3 є першим виходом пристрою та з'єднаний з адресними входами блоків 2 та 5 пам'яті станів та команд, інформаційний вихід блока 2 пам'яті станів підключений до першого входу схеми порівняння 1, другий вхід якої є др угим входом пристрою, другим виходом якого є перший (інформаційний) вихід блока 5 пам'яті команд, адресний вхід блока 4 пам'яті переходів є третім входом пристрою, перший (інформаційний) вихід блока 4 пам'яті переходів з'єднаний з першим входом лічильника адреси 3, другий та третій входи якого підключені відповідно до першого та другого виходів вузла логічного ке рування 6, перший вхід якого з'єднаний з другим виходом блока 4 пам'яті переходів, другий та третій входи вузла логічного керування 8 підключені відповідно до другого виходу блока 5 пам'яті команд та до виходу логічного елемента "І" 7, перший вхід якого є третім входом пристрою, другий вхід логічного елемента "І" 7 з'єднаний з виходом схеми порівняння 1. Блок 2 пам'яті станів та блок 5 пам'яті команд призначені для зберігання програми (яка у загальному випадку складається із k підпрограм) керування циклом роботи обслуговуваного об'єкта. Програма керування циклом у запропонованому контролері являє собою послідовність рядків, кожний з яких складається з двох частин: 1) комбінації команд на вмикання та вимикання m механізмів, 2) комбінації станів, в які повинні прийти n датчиків у результаті спрацьовування m механізмів, при цьому до блока 5 пам'яті команд записується послідовність комбінацій команд на вмикання та вимикання механізмів, а до блока 2 пам'яті станів послідовність комбінацій станів, до яких повинні прийти датчики, які фіксують положення механізмів, в результаті виконання відповідних команд, причому в кожному рядку блока 5 пам'я ті команд один розряд виділений для програмування ознаки кінця програми (підпрограми) - КП. Адресація блоків 2, 5 здійснюється паралельно за допомогою лічильника адреси 3. Блок 4 пам'яті переходів призначений для зберігання та відпрацьовування програми вибору початкових адрес підпрограм, які записані у блоках 2 та 5 пам'яті станів та команд. Схема порівняння 1 призначена для паралельного (одночасного) порівняння комбінацій фактичних станів датчиків циклу з їх очікуваними значеннями, які записані в і-му рядку блока 2 пам'яті станів. Вузол логічного керування 6 залежно від комбінації сигналів на його входа х здійснює логічне керування роботою лічильника адреси 3. Логічний елемент "І" 7 призначений для формування сигналу еквівалентності Е на вході вузла логічного керування 6 при будуванні контролерних мереж. Як блоки, з яких складається пропонований пристрій, можуть використовуватися стандартні елементи (мікросхеми): лічильники, схеми порівняння; блоки пам'яті можуть бути реалізовані, наприклад, на постійних програмованих запам'ятовуючих пристроях (ППЗП), а вузол логічного керування - на програмованій логічній матриці (ПЛМ). Мережний програмований контролер паралельної дії працює таким чином. Умовно він може бути розділений на два вузла: ведений контролер (а1-аn), який включає до себе схему порівняння 1, блоки пам'яті станів та команд 2 та 5 та логічний елемент "І" 7, а також ведучий контролер, який включає до себе лічильник адреси 3, блок пам'яті переходів 4 та вузол логічного керування 6. Ведучий контролер використовується для аналізу комбінацій станів датчиків умов переходів, адресації ведених контролерів у процесі відробки підпрограм а також для організації функцій переривання. Ведений контролер здійснює безпосередньо відробку підпрограм, формує керуючі команди та сигнали кінця підпрограми (КП) та еквівалентності (Е). 2 37651 Будування контролерних мереж на основі запропонованого пристрою відбувається шляхом каскадування ведених контролерів, керованих одним ведучим контролером, за рахунок чого досягається економія апаратних витрат. Встановлення пристрою у початковий стан здійснюється за допомогою зовнішнього імпульсного сигналу початкового встановлення ПВ, який обнуляє лічильник адреси. Процес відпрацьовування керуючої програми складається з двох етапів: 1) аналізу комбінацій станів датчиків умов переходів (станів зовнішнього середовища) та формування початкової адреси підпрограми; 2) власне відпрацьовування вибраної підпрограми, причому аналіз станів зовнішнього середовища здійснюється паралельно та незалежно від відпрацьовування підпрограми. В останньому рядку кожної підпрограми а також у нульовому рядку програми записується тільки ознака кінця підпрограми КП, яка використовується як дозвіл переходу пристрою до відпрацьовування будь-якої із записаних у блоках 2 та 5 підпрограм. Вибір початкової адреси підпрограми здійснюється за допомогою блока 4 пам'яті переходів, який у разі виникнення на його вході однієї із запрограмованих комбінацій встановлює лічильник адреси до відповідного даній комбінації стану. У разі виникнення на його вході незапрограмованої комбінації лічильник адреси буде встановлений у нульовий стан або залишиться у ньому. До вузла логічного керування 6 записуються такі логічні рівняння: Якщо вирішується логічне рівняння: Е· КП · ПР =+1, то на першому виході вузла логічного керування 6 з'являється сигнал "+1", за яким лічильник адреси 3 адресує блоки 2 та 5 пам'яті станів та команд до наступного (і+1) рядка. Якщо на якому-небудь кроці підпрограми станеться вихід з ладу механізму або датчика (який не приводить до аварійної ситуації), перехід до наступного рядка підпрограми не відбувається, тому що не спрацьовує схема порівняння 1, яка блокує логічний елемент "І" 7. У разі виходу з ладу механізмів або датчиків можливе виникнення заборонених комбінацій станів механізмів, при яких у керованих об'єктах можуть з'являтися аварійні ситуації, які потребують негайного втручання до процесу керування. Для реакції пристрою на аварійні ситуації один з виходів блока 4 пам'яті переходів виділений для фіксації та видачі на третій вхід вузла логічного керування 6 сигналу ознаки переривання ПР, при цьому вирішується логічне рівняння: ПР=А, у результаті чого лічильник адреси без очікування кінця відпрацьовування робочої підпрограми переадресує блоки 2 та 5 пам'яті станів та команд до початкової адреси перериваючої підпрограми. При проектуванні контролерних мереж на основі запропонованого пристрою з виходу схем порівняння кожного з ведених контролерів (а1-аn) на другі входи логічних елементів "І" 7 поступає сигнал еквівалентності еі. На перші входи логічних елементів "І" 7 всіх ведених контролерів, крім останнього, поступає сигнал Еі, який являє собою добуток сигналів еквівалентності е і+1·еі+2·...·е n. Перший вхід логічного елемента останнього веденого контролера аn підключений до Un. Таким чином, сигнал еквівалентності Е являє собою добуток сигналів еквівалентності кожного з ведених контролерів: Е=е 1·е2·...·е n. Іншими словами, формування сигналу еквівалентності на третьому вході вузла логічного керування 6 можливо тільки при наявності даного сигналу на виходах схем порівняння 1 всіх ведених контролерів. КП+ПР=А, Е· КП · ПР =+1, де ПР - ознака переривання, Е - сигнал еквівалентності з виходу елемента "І" 7. Якщо вирішується логічне рівняння: КП =А, то на другому виході вузла логічного керування 6 з'являється сигнал "Адреса" ("A"), за яким лічильник адреси 3 здійснює переадресацію блоків 2 та 5 пам'яті станів та команд на першу адресу вибраної підпрограми або на нульовий рядок. 3 37651 Фіг. __________________________________________________________ ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2001 р. Формат 60х84 1/8. Обсяг ______ обл.-вид. арк. Тираж 50 прим. Зам._______ ____________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 ___________________________________________________________ 4

ДивитисяДодаткова інформація

Назва патенту англійськоюNetwork programmable controller

Автори англійськоюZaharii Hennadii Ivanovych, Furman Illia Oleksandrovych

Назва патенту російськоюСетевой программируемый контроллер

Автори російськоюЗагарий Геннадий Иванович, Фурман Илья Александрович

МПК / Мітки

МПК: G05B 19/18

Мітки: мережний, контролер, програмований

Код посилання

<a href="https://ua.patents.su/4-37651-merezhnijj-programovanijj-kontroler.html" target="_blank" rel="follow" title="База патентів України">Мережний програмований контролер</a>

Попередній патент: Синтаксичний аналізатор контекстовільних граматик

Наступний патент: Керуюча насадка вентиля калорифера

Випадковий патент: Поліуретанові піни