Програмований багатоканальний таймер

Формула / Реферат

Програмований багатоканальний таймер, що містить першу дискретну лінію затримки, N+3 логічних елементів І, запам'ятовуючий пристрій, лічильник керування, N тригерів, логічний елемент АБО, перший вхід якого підключений до вхідної шини імпульсу запуску, другий вхід до виходу (N+3)-го логічного елемента І, а вихід - до входу початкового установлення першої дискретної лінії затримки та лічильного входу лічильника керування, вхід установлення у початковий стан якого підключений до виходу (N+2)-гo логічного елемента І, а виходи лічильника керування підключені до першої групи адресних входів запам'ятовуючого пристрою, друга група адресних входів якого підключена до вхідної шини керування, перша група виходів підключена до інформаційних входів першої дискретної лінії затримки, а друга група виходів підключена до перших входів логічних елементів І, другі входи (N+l)-гo та (N+2)-гo логічних елементів І підключені до виходу першої дискретної лінії затримки, виходи логічних елементів І підключені до відповідних І-виходів тригерів, вихід (N-H)-гo логічного елемента І підключений до К-входів тригерів, виходи яких підключені до відповідних вихідних шин, а входи синхронізації тригерів підключені до входу тактових імпульсів першої дискретної лінії затримки і вхідної шини тактових імпульсів, який відрізняється тим, що в нього введено другу дискретну лінію затримки і комутатор кодів, інформаційні входи якого підключені до вхідної шини кодів інтервалів, входи керування підключені до третьої, групи виходів запам'ятовуючого пристрою, а виходи комутатора кодів підключені до інформаційних входів другої дискретної лінії затримки, вхід тактових імпульсів якої .підключений до вхідної шини тактових імпульсів, вхід запуску підключений до виходу першої дискретної лінії затримки, вхід початкового установлення підключений до виходу логічного елемента АБО, а вихід підключений до других входів усіх логічних елементів І.

Текст

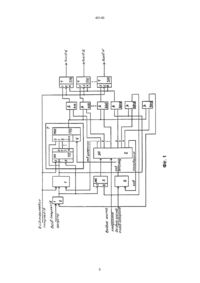

Програмований багатоканальний таймер, що містить першу дискретну лінію затримки, N+3 логічних елементів І, запам'ятовуючий пристрій, лічильник керування, N тригерів, логічний елемент АБО, перший вхід якого підключений до вхідної шини імпульсу запуску, другий вхід до виходу (N+3)-го логічного елемента І, а вихід - до входу початкового установлення першої дискретної лінії затримки та лічильного входу лічильника керування, вхід установлення у початковий стан якого підключений до виходу (N+2)-гo логічного елемента І, а виходи лічильника керування підключені до першої гр упи адресних входів запам'ятовуючого пристрою, друга група адресних входів якого підключена до вхідної шини керування, перша група виходів підключена до інформаційних входів першої дискретної лінії затримки, а друга група виходів A (54) ПРОГРАМОВАНИЙ БАГАТОКАНАЛЬНИЙ ТАЙМЕР 40140 мою затримок спрацьовування лічильника керування і запам'ятовуючого пристрою. Якщо імпульс на виході дискретної лінії затримки з'явиться раніше, ніж установляться сигнали на виходах запам'ятовуючого пристрою, відбудеться порушення функціонування таймера. Таким чином, мінімальний часовий інтервал повинен бути більшим за час відновлення. Виключенням є випадок, коли вихідні імпульси збігаються. При цьому формування вихідних імпульсів відбувається від одного і того ж тактового імпульсу. В основу винаходу поставлено задачу створення пристрою з підвищеною точністю формування малих часових інтервалів між вихідними імпульсами шляхом зменшення часу відновлення. Поставлена задача вирішується тим, що у пристрій, який містить першу дискретну лінію затримки N+3 логічних елементів І, запам'ятовуючий пристрій, лічильник керування, N тригерів, логічний елемент АБО, перший вхід якого підключений до вхідної шини імпульсу запуску, другий вхід до виходу (N+3)-гo логічного елемента І, а вихід - до входу початкового установлення першої дискретної лінії затримки та лічильного входу лічильника керування, вхід установлення у початковий стан якого підключений до виходу (N+2)-гo логічного елемента І, а виходи лічильника керування підключені до першої групи адресних входів запам'я товуючого пристрою, друга група адресних входів якого підключена до вхідної шини керування, перша група виходів підключена до інформаційних входів першої дискретної лінії затримки, а друга група виходів підключена до перших входів логічних елементів І, другі входи (N+1)-гo та (N+2)-гo логічних елементів І підключені до виходу першої дискретної лінії затримки, виходи логічних елементів І підключені до відповідних І-виходів тригерів, вихід (N+1)-гo логічного елемента І підключений до К-входів тригерів, ви ходи яких підключені до відповідних вихідних шин, а входи синхронізації тригерів підключені до входу тактови х імпульсів першої дискретної лінії затримки і вхідної шини тактових імпульсів, введено другу дискретну лінію затримки і комутатор кодів, інформаційні входи якого підключені до вхідної шини кодів інтервалів, входи керування підключені до третьої групи виходів запам'ятовуючого пристрою, а виходи комутатора кодів підключені до інформаційних входів другої дискретної лінії затримки, вхід тактових імпульсів якої підключений до вхідної шини тактових імпульсів, вхід запуску підключений до виходу першої дискретної лінії затримки, вхід початкового установлення підключений до виходу логічного елемента АБО, а ви хід підключений до други х входів усіх логічних елементів І. Причинно-наслідковий зв'язок між сукупністю ознак винаходу і технічним результатом полягає в такому. Введення вищевказаних конструктивних елементів з відповідними зв'язками дає можливість підвищити точність формування малих часових інтервалів між вихідними імпульсами шляхом зменшення часу відновлення. На фіг. 1 наведено схему даного пристрою, на фіг. 2 - часові діаграми роботи пристрою для випадку N=2 (N - кількість виходів таймера). ТІ - тактові імпульси, ЛК - лічильник керування; ІЗ - імпульс запуску; ДЛЗ - дискретна лінія затримки; ЗП запам’ятовуючий пристрій; tв - час відновлення таймера; tс - затримка керуючого лічильника; tзп затримка запам'ятовуючого пристрою. Програмований багатоканальний таймер містить першу дискретну лінію затримки 1, запам'ятовуючий пристрій 2, лічильник 3 керування, логічні елементи І 4.1¸4.(N+3), тригери 5.1¸5.N, логічний елемент АБО 6, др угу дискретну лінію затримки 7, комутатор кодів 8. Перший вхід логічного елемента АБО 6 підключений до вхідної шини імпульсу запуску, другий вхід - до виходу (N+3)-гo логічного елемента І 4.(N+3), а вихід - до входу початкового установлення дискретної лінії затримки 1 і лічильного входу лічильника керування 3, вхід установлення в початковий стан якого підключений до виходу (N+2)-гo логічного елемента І 4.(N+2), а виходи лічильника керування 3 підключені до першої групи адресних входів запам'ятовуючого пристрою 2, друга гр упа адресних входів якого підключена до вхідної шини керування, перша група виходів підключена до інформаційних входів першої дискретної лінії затримки 3, а друга група виходів підключена до перших входів логічних елементів І 4.1¸4.(N+3), другі входи (N+1)-гo та (N+2)-гo логічних елементів І 4.(N+1)¸4.(N+2) підключені до виходу першої дискретної лінії затримки 1, виходи логічних елементів І 4.1¸4.N підключені до відповідних І-входів тригерів 5.1¸5.N, вихід (N+1)-гo логічного елемента І 4.(N+1) підключений до К-входів тригерів, виходи яких підключені до відповідних вихідних шин, а входи синхронізації тригерів підключені до входу тактових імпульсів першої дискретної лінії затримки 4 і до вхідної шини тактових імпульсів. Інформаційні входи комутатора кодів 8 підключені до вхідної шини кодів інтервалів, входи керування - до третьої групи виходів запам'ятовуючого пристрою 3, а виходи - до інформаційних входів др угої дискретної лінії затримки 7. Вхід тактових імпульсів другої дискретної лінії затримки 7 підключений до вхідної шини тактових імпульсів, вхід запуску - до виходу першої дискретної лінії затримки 1, вхід початкового установлення - до виходу логічного елемента 6, а вихід - до других входів логічних елементів І 4.1¸4.(N+3). Дискретна друга лінія затримки 7 може складатися, наприклад, із регістра зсуву "одиниці" 7.1 і мультиплексора 7.2. Вхід послідовного прийому інформації регістра 7.1 і перший інформаційний вхід мультиплексора 7.2 підключені до входу імпульсу запуску другої дискретної лінії затримки 7. Решта інформаційних входів м ультиплексора 7.2 підключені до відповідних ви ходів регістра 7.1. У початковому стані на вхід синхронізації регістра зсуву 7.1 надходять тактові імпульси. На вході послідовного прийому інформації і усіх виходах регістра 7.1 сигнал відповідає логічному "нулю". На керуючі входи мультиплексора 7.2 надходить код, який забезпечує підключення до виходу др угої дискретної лінії затримки 7 одного з його інформаційних входів. За тримка вихідного імпульсу тим більша, чим старший розряд регістра 7.1 підключений до виходу другої дискретної лінії затримки 7. Робочий цикл другої дискретної лінії затримки 7 починається, коли на вхід послідовного прийому 2 40140 інформації регістра 7.1 надходить імпульс запуску. Тактовий імпульс записує логічну "одиницю" у перший розряд регістра 7.1. Логічна "одиниця" зсувається у старші розряди регістра 7.1 тактовими імпульсами доти, поки на виході дискретної лінії затримки 7 не з'явиться імпульс, який потім через: зовнішні кола надходить на R-вхід регістра 7.1 і обнулює його. Обн уління відбувається за спадом імпульсу на R-вході. Схема повертається у початковий стан. Даний пристрій, працює таким чином. У вихідному стані лічильник 3 керування перебуває у стані 0. Вихідні сигнали запам'ятовуючого пристрою 2 визначаються кодом адреси, який надходить з лічильника 3 керування і з вхідної шини керування. На інформаційні входи першої дискретної лінії затримки 1 з виходу запам'ятовуючого пристрою 2 надходить код затримки. На входи керування комутатора кодів 8 з виходу запам'ятовуючого пристрою 2 надходять керуючі сигнали, які забезпечують підключення із вхідної шини коду інтервалів до інформаційних входів др угої дискретної лінії затримки 7 коду нульової затримки. На входи логічних елементів І 4 від запам'ятовуючого пристрою 2 надходить сигнал логічного нуля. На вхід тактових: імпульсів пристрою надходять тактові імпульси. Робочий цикл починається після приходу імпульсу запуску. Імпульс запуску, який надходить із входу пристрою, проходить через логічний елемент АБО 6, здійснює початкове установлення дискретних ліній затримки 1 і 7 відповідно до кодів на їх інформаційних входах і збільшує вміст лічильника 3 керування на одиницю. Після початкового установлення починається робочий цикл першої дискретної лінії затримки 1, змінюється код адреси на вході запам'ятовуючого пристрою 2, а на виходах запам'ятовуючого пристрою 2 змінюються код затримки і керуючі сигнали, які надходять на логічні елементи І 4 і комутатор кодів 8. Керуючі сигнали забезпечують підключення до виходу др угої дискретної лінії затримки 7 І - входу тригера 5.1 через логічний елемент І 4.1 та логічного елемента АБО 6 через логічний елемент І 4.(N+3). Крім того, керуючі сигнали з виходу запам'ятовуючого пристрою 2 забезпечують підключення до інформаційних входів другої дискретної лінії затримки 7 коду інтервалу, який дорівнює нулю. По закінченні робочого циклу перша дискретна лінія затримки 1 видає на вхід затриманий імпульс, який проходить без затримки (ні на один такт) через мультиплексор 7.2 на вихід другої дискретної лінії затримки 7. Імпульс з виходу другої дискретної лінії затримки 7 надходить через логічний елемент І 4.1 на І-вхід тригера 5.1, дозволяючи установлення у стан 1. Тактовий імпульс, який надходить на вхід синхронізації тригера 5.1, установлює його у стан 1. Крім того, імпульс із входу др угої дискретної лінії затримки 7 через логічний елемент І 4.(N+3) і логічний елемент АБО здійснює початкове установлення першої дискретної лінії затримки згідно з кодом на її інформаційних входах і збільшує вміст лічильника 3 керування на одиницю. Після початкового установлення починається новий цикл роботи першої дискретної лінії затрим ки 1, змінюється код адреси на вході запам'ятовуючого пристрою 2, а на виходах запам'ятовуючого пристрою 2 змінюються код затримки і керуючі сигнали, які надходять на логічні елементи І та комутатор кодів 8. Керуючі сигнали забезпечують підключення до виходу першої дискретної лінії затримки 1 К-входів тригерів, а до виходу др угої дискретної лінії затримки 7 І-входу тригера 5.2 та логічного елемента АБО, а також коду інтервалу до інформаційних входів другої дискретної лінії затримки 7. По закінченні робочого циклу першої дискретної лінії затримки 1 імпульс з її виходу запускає другу дискретну лінію затримки 7 і надходить через логічний елемент І 4.(N+1) на К-вхід тригерів, дозволяючи їх установлення у стан 0. За спадом тактового імпульсу тригер 5.1 установлюється у стан 0, а решта тригерів 5.2¸5.N не змінюють свого стану, залишаються у стані 0. Імпульс на виході другої дискретної лінії затримки 7 з'являється із затримкою відносно запускаючого імпульсу на вході цієї лінії. Затримка залежить від коду на інформаційних входах др угої дискретної лінії затримки 7. На фіг. 2 величина затримки дорівнює одному такту. Імпульс з виходу др угої дискретної лінії затримки 7 надходить через логічний елемент І 4.2 на Івхід тригера 5.2, дозволяючи установлення у стан 1. За спадом тактового імпульсу тригер 5.2 установлюється у стан 1. Крім того, імпульс з виходу др угої дискретної лінії затримки 7 через логічний елемент І 4.(N+3) та логічний елемент АБО 6 здійснює початкове установлення першої дискретної лінії затримки 1, збільшує вміст лічильника 3 керування на одиницю і здійснює початкове установлення другої дискретної лінії затримки 7. Початкове установлення другої дискретної лінії затримки 7 відбувається за спадом імпульсу. Таким чином, на виході І закінчується формування імпульсу за тривалістю (формується спад), а на виході ІІ формується фронт імпульсу і починається формування тривалості імпульсу. Інтервал між спадом імпульсу на виході та фронтом імпульсу на виході II дорівнює кількості тактів затримки, які формуються другою дискретною лінією затримки 7 (на фіг. 2 - один такт). Мінімальна кількість тактів, затримки може дорівнювати нулю. Максимальна кількість тактів повинна перекривати час відновлення таймера (на фіг. 2 - tв). Після початкового установлення починається новий робочий цикл першої дискретної лінії затримки 1. Згідно з кодом лічильника 3 керування на виходах запам'ятовуючого пристрою 2 установлюються сигнали керування, які блокують логічні елементи 4.1¸4.N, 4.(N+3), знімають блокування логічних елементів І 4.(N+1), 4.(N+2) і підключають до інформаційних входів другої дискретної лінії затримки 7 код інтервалу, який дорівнює нулю. В результаті цього імпульс з виходу першої дискретної лінії затримки 1 забезпечує початкове установлення лічильника 2 керування і, після проходження через дискретну лінію затримки 7, забезпечує початкове установлення в 0 тригерів 5. Пристрій повертається у початковий стан. 3 40140 Новий робочий цикл починається в момент, коли на вхід логічного елемента АБО 6 надійде імпульс запуску. Величина часових інтервалів і порядок проходження вихідних імпульсів програмованого багато канального таймера в новому циклі буде залежати від сигналів, які установляться на вхідній шині керування і вхідній шині кодів інтервалів. 4 Фіг. 1 40140 5 Фіг. 2 40140 6 40140 __________________________________________________________ ДП “Український інститут промислової власності (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2001 р. Формат 60х84 1/8. Обсяг ______ обл.-вид.арк. Тираж 50 прим. Зам._______ ____________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 ___________________________________________________________ 7

ДивитисяДодаткова інформація

Назва патенту англійськоюProgrammable multichannel timer

Автори англійськоюPyko Heorhii Anatoliiovych

Назва патенту російськоюПрограммируемый многоканальный таймер

Автори російськоюПико Георгий Анатольевич

МПК / Мітки

МПК: H03K 5/13

Мітки: багатоканальний, таймер, програмований

Код посилання

<a href="https://ua.patents.su/7-40140-programovanijj-bagatokanalnijj-tajjmer.html" target="_blank" rel="follow" title="База патентів України">Програмований багатоканальний таймер</a>

Попередній патент: Вибухова водовмісна гелеподібна суспензія

Наступний патент: Пристрій для дугового зварювання

Випадковий патент: Спосіб зниження концентрації метану у шахтних виробках