Двотактний симетричний підсилювач струму

Номер патенту: 42958

Опубліковано: 27.07.2009

Автори: Гарнага Володимир Анатолійович, Азаров Олексій Дмитрович, Решетнік Олександр Олександрович, Теплицький Михайло Юхимович

Формула / Реферат

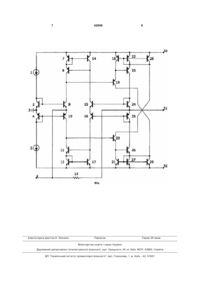

Двотактний симетричний підсилювач струму, який містить перше та друге джерела струму, резистор зворотного зв'язку, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, а також з першим виводом резистора зворотного зв'язку, емітери першого і другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектори третього і четвертого транзисторів з'єднано з базами п'ятого і шостого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами та колекторами першого і другого транзисторів відповідно, а також з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, вихідну шину з'єднано з другим виводом резистора зворотного зв'язку, який відрізняється тим, що у нього введено вісімнадцять транзисторів, причому колектори третього і четвертого транзисторів з'єднано з колекторами дев'ятого та десятого транзисторів відповідно, емітери дев'ятого та десятого транзисторів з'єднано з базами та колекторами сьомого та восьмого транзисторів відповідно, а також з базами одинадцятого та дванадцятого транзисторів відповідно, бази дев'ятого і десятого транзисторів з'єднано з колекторами одинадцятого та дванадцятого транзисторів відповідно, а також з колекторами тринадцятого та чотирнадцятого транзисторів відповідно, емітери тринадцятого та чотирнадцятого транзисторів об'єднано між собою, бази тринадцятого і чотирнадцятого транзисторів з'єднано з базами і колекторами двадцять першого та двадцять другого транзисторів відповідно, а також з колекторами дев'ятнадцятого та двадцятого транзисторів, емітери двадцять першого та двадцять другого транзисторів об'єднано та з'єднано з вихідною шиною, а також з другим виводом резистора зворотного зв'язку, емітери п'ятого та шостого транзисторів з'єднано з колекторами п'ятнадцятого ти шістнадцятого транзисторів відповідно, а також з колекторами дев'ятнадцятого та двадцятого транзисторів відповідно, базу і колектор сімнадцятого транзистора об'єднано та з'єднано з базою і колектором двадцять третього транзистора і базою п'ятнадцятого транзистора, а також з колектором шостого транзистора, базу і колектор вісімнадцятого транзистора об'єднано та з'єднано з базою і колектором двадцять четвертого транзистора і базою шістнадцятого транзистора, а також з колектором п'ятого транзистора, емітери сьомого, одинадцятого, п'ятнадцятого, сімнадцятого та двадцять третього транзисторів підключено до шини додатного живлення, емітери восьмого, дванадцятого, шістнадцятого, вісімнадцятого та двадцять четвертого транзисторів підключено до шини від'ємного живлення.

Текст

Двотактний симетричний підсилювач струму, який містить перше та друге джерела струму, резистор зворотного зв'язку, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, а також з першим виводом резистора зворотного зв'язку, емітери першого і другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектори третього і четвертого транзисторів з'єднано з базами п'ятого і шостого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами та колекторами першого і другого транзисторів відповідно, а також з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, вихідну шину з'єднано з другим виводом резистора зворотного зв'язку, який відрізняється тим, що у нього введено вісімнадцять транзисторів, причому колектори третього і четвертого транзисторів з'єднано з колекторами дев'ятого та десятого транзисторів відповідно, емітери дев'ятого та десятого транзисторів з'єднано з базами та колекторами сьомого та восьмого транзисторів U 2 UA 1 3 постійного струму. Третій і четвертий транзистори мають структуру відповідно другого і першого транзисторів, їх колектори є виходами підсилювача постійного струму, а бази третього і четвертого транзисторів з'єднано з колекторами першого і другого транзисторів відповідно. Бази першого і другого транзисторів з'єднано з шиною нульового потенціалу через перший і другий транзистори відповідно у діодному включені та перше і друге джерела струмів, які включено між шинами додатного та від'ємного живлення та базами першого і другого транзисторів відповідно. Перший та другий транзистори з діодному включенні мають структуру відповідно до першого і другого транзисторів відповідно. Перший та другий струмозадаючі елементи виконано відповідно на першому і другому відбивачах струму та п'ятому і шостому транзисторах, які мають структуру відповідно до третього і четвертого транзисторів. Бази п'ятого і шостого транзисторів є виходами відповідно першого і другого струмозадаючого елементів, їх колектори з'єднано з шиною нульового потенціалу, а емітери - з виходами відповідно першого і другого відбивачів струму. Входи відбивачів струму з'єднано через двополюсний струмозадаючий елемент. Колектори третього і четвертого транзисторів з'єднано через коло зміщення. Коло зміщення виконано на третьому і четвертому транзисторах в діодному включенні. Виводи кола зміщення підключено до баз сьомого і восьмого транзисторів, які ввімкнено по схемі із загальним колектором. Емітери сьомого і восьмого транзисторів з'єднано, вони є виходом підсилювача. Недоліком пристрою є низький коефіцієнт підсилення та висока нелінійність. Як найближчий аналог обрано двотактний симетричний підсилювач струму (Push-pull amplifier with current mirrors for determining the quiescent operating point, United States Patent 3,852,678, Dec.3, 1974), який містить перше і друге джерела струму, резистор зворотного зв'язку, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього четвертого транзисторів відповідно, а також з першим виводам резистора зворотного зв'язку, колектори третього і четвертого транзисторів з'єднано з базами п'ятого і шостого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами та колекторами першого і другого транзисторів відповідно, а також з першими виводами першого і другого джерел струму, емітери першого і другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, другі виводи першого і другого джерел струму та емітери п'ятого і шостого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, колектори п'ятого і шостого транзисторів з'єднано з вихідною шиною та другим виводом резистора зворотного зв'язку. Недоліком найближчого аналога є низький коефіцієнт підсилення, що обмежує галузь використання пристрою. 42958 4 В основу корисної моделі поставлено задачу створення двотактного симетричного підсилювача струму, в якому за рахунок введення нових елементів та зв'язків між ними збільшується коефіцієнт підсилення, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача досягається тим, що у двотактний симетричний підсилювач струму, який містить перше та друге джерела струму, резистор зворотного зв'язку, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, а також з першим виводом резистора зворотного зв'язку, емітери першого і другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектори третього і четвертого транзисторів з'єднано з базами п'ятого і шостого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами та колекторами першого і другого транзисторів відповідно, а також з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, вихідну шину з'єднано з другим виводом резистора зворотного зв'язку, введено вісімнадцять транзисторів, причому колектори третього і четвертого транзисторів з'єднано з колекторами дев'ятого та десятого транзисторів відповідно, емітери дев'ятого та десятого транзисторів з'єднано з базами та колекторами сьомого та восьмого транзисторів відповідно, а також з базами одинадцятого та дванадцятого транзисторів відповідно, бази дев'ятого і десятого транзисторів з'єднано з колекторами одинадцятого та дванадцятого транзисторів відповідно, а також з колекторами тринадцятого та чотирнадцятого транзисторів відповідно, емітери тринадцятого та чотирнадцятого транзисторів об'єднано між собою, бази тринадцятого і чотирнадцятого транзисторів з'єднано з базами і колекторами двадцять першого та двадцять другого транзисторів відповідно, а також з колекторами дев'ятнадцятого та двадцятого транзисторів, емітери двадцять першого та двадцять другого транзисторів об'єднано та з'єднано з вихідною шиною, а також з другим виводом резистора зворотного зв'язку, емітери п'ятого та шостого транзисторів з'єднано з колекторами п'ятнадцятого ти шістнадцятого транзисторів відповідно, а також з колекторами дев'ятнадцятого та двадцятого транзисторів відповідно, базу і колектор сімнадцятого транзистора об'єднано та з'єднано з базою і колектором двадцять третього транзистора і базою п'ятнадцятого транзистора, а також з колектором шостого транзистора, базу і колектор вісімнадцятого транзистора об'єднано та з'єднано з базою і колектором двадцять четвертого транзистора і базою шістнадцятого транзистора, а також з колектором п'ятого транзистора, емітери сьомого, одинадцятого, п'ятнадцятого, сімнадцятого та двадцять третього транзисторів підключено до шини додатного 5 живлення, емітери восьмого, дванадцятого, шістнадцятого, вісімнадцятого та двадцять четвертого транзисторів підключено до шини від'ємного живлення. На кресленні представлено принципову схему двотактного симетричного підсилювача струму. Пристрій містить вхідну шину 6, яку з'єднано з емітерами третього 9 і четвертого 10 транзисторів, а також з першим виводом резистора зворотного зв'язку 13, емітери першого 2 і другого 4 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 3, колектори третього 9 і четвертого 10 транзисторів з'єднано з базами п'ятого 19 і шостого 20 транзисторів відповідно, бази третього 9 і четвертого 10 транзисторів з'єднано з базами та колекторами першого 2 і другого 4 транзисторів відповідно, а також з першими виводами першого 1 і другого 5 джерел струму, другі виводи першого 1 і другого 5 джерел струму з'єднано з шинами додатного 30 і від'ємного 32 живлення відповідно, вихідну шину 31 з'єднано з другим виводом резистора зворотного зв'язку 13, колектори третього 9 і четвертого 10 транзисторів з'єднано з колекторами дев'ятого 8 та десятого 11 транзисторів відповідно, емітери дев'ятого 8 та десятого 11 транзисторів з'єднано з базами та колекторами сьомого 7 та восьмого 12 транзисторів відповідно, а також з базами одинадцятого 14 та дванадцятого 17 транзисторів відповідно, бази дев'ятого 8 і десятого 11 транзисторів з'єднано з колекторами одинадцятого 14 та дванадцятого 17 транзисторів відповідно, а також з колекторами тринадцятого 15 та чотирнадцятого 16 транзисторів відповідно, емітери тринадцятого 15 та чотирнадцятого 16 транзисторів об'єднано між собою, бази тринадцятого 15 і чотирнадцятого 16 транзисторів з'єднано з базами і колекторами двадцять першого 24 та двадцять другого 25 транзисторів відповідно, а також з колекторами дев'ятнадцятого 23 та двадцятого 26 транзисторів, емітери двадцять першого 24 та двадцять другого 25 транзисторів об'єднано та з'єднано з вихідною шиною, а також з другим виводом резистора зворотного зв'язку 13, емітери п'ятого 19 та шостого 20 транзисторів з'єднано з колекторами п'ятнадцятого 18 та шістнадцятого 21 транзисторів відповідно, а також з колекторами дев'ятнадцятого 23 та двадцятого 26 транзисторів відповідно, базу і колектор сімнадцятого 22 транзистора об'єднано та з'єднано з базою і колектором двадцять третього 28 транзистора і базою п'ятнадцятого 18 транзистора, а також з колектором шостого 20 транзистора, базу і колектор вісімнадцятого 27 транзистора об'єднано та з'єднано з базою і колектором двадцять четвертого 29 транзистора і базою шістнадцятого 21 транзистора, а також з колектором п'ятого 19 транзистора, емітери сьомого 7, одинадцятого 14, п'ятнадцятого 18, сімнадцятого 22 та двадця 42958 6 ть третього 28 транзисторів підключено до шини додатного живлення 30, емітери восьмого 12, дванадцятого 17, шістнадцятого 21, вісімнадцятого 27 та двадцять четвертого 28 транзисторів підключено до шини від'ємного живлення 32. Пристрій працює таким чином. Вхідний сигнал у вигляді струму поступає на вхідну шину 6. Якщо вхідний струм втікає у схему, то четвертий 10 транзистор привідкривається, а третій 9 транзистор призакривається, відповідно шостий 20 транзистор привідкривається, а п'ятий 19 транзистор призакривається. При цьому потенціал точки об'єднання емітерів тринадцятого 15 і чотирнадцятого 16 транзисторів зменшується і прямує до -Еж. При цьому точка об'єднання емітерів двадцять першого 24 і двадцять другого 25 транзисторів, а також вихідна шина 31 відслідковує потенціал точки об'єднання емітерів тринадцятого 15 і чотирнадцятого 16 транзисторів і також зменшується та наближається до - Еж. Якщо вхідний струм витікає зі схеми, то четвертий 10 транзистор призакривається, а третій 9 транзистор привідкривається, відповідно шостий 20 транзистор призакривається, а п'ятий 19 транзистор привідкривається. При цьому потенціал точки об'єднання емітерів тринадцятого 15 і чотирнадцятого 16 транзисторів збільшується і прямує до Еж. При цьому точка об'єднання емітерів двадцять першого 24 і двадцять другого 25 транзисторів, а також вихідна шина 31 відслідковує потенціал точки об'єднання емітерів тринадцятого 15 і чотирнадцятого 16 транзисторів і також збільшується та наближається до Еж. Перше 1 і друге 5 джерела струму та перший 2, другий 4, третій 9, четвертий 10 транзистори утворюють схему завдання режиму по постійному струму. Сьомий 7, дев'ятий 8, одинадцятий 14, а також десятий 11, восьмий 12 та дванадцятий 17 транзистори являють собою відбивачі струму, що завдають базовий струм для підсилювальних каскадів на п'ятому 19 і шостому 20 транзисторах відповідно. Тринадцятий 15, чотирнадцятий 16, двадцять перший 24, двадцять другий 25 транзистори утворюють двонаправлений відбивач струму, який через відбивачі струму, що побудовані на п'ятнадцятому 18, сімнадцятому 22, двадцять третьому 28, а також шістнадцятому 21, вісімнадцятому 27 і двадцять четвертому 29 транзисторах відповідно, завдає базовий струм підсилювальних каскадів на дев'ятнадцятому 23 і двадцятому 26 транзисторах відповідно. Резистор зворотного зв'язку 13 задає коефіцієнт підсилення. Шини додатного 30 і від'ємного 32 живлення, а також шина нульового потенціалу 3 забезпечують потрібний рівень напруги для живлення схеми. 7 Комп’ютерна верстка Н. Лиcенко 42958 8 Підписне Тираж 28 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюPush-pull balanced current amplifier

Автори англійськоюAzarov Oleksii Dmytrovych, Teplytskyi Mykhailo Yukhymovych, Reshetnik Oleksandr Oleksandrovych, Harnaha Volodymyr Anatoliiovych

Назва патенту російськоюДвухтактный симметричный усилитель тока

Автори російськоюАзаров Алексей Дмитриевич, Теплицкий Михаил Ефимович, Решетник Александр Александрович, Гарнага Владимир Анатольевич

МПК / Мітки

Мітки: двотактний, підсилювач, симетричний, струму

Код посилання

<a href="https://ua.patents.su/4-42958-dvotaktnijj-simetrichnijj-pidsilyuvach-strumu.html" target="_blank" rel="follow" title="База патентів України">Двотактний симетричний підсилювач струму</a>

Попередній патент: Спосіб шифрування даних

Наступний патент: Спосіб вимірювання бронхіального опору

Випадковий патент: Спосіб лікування інфекційно-запальних захворювань органів сечової системи у жінок в постменопаузальному періоді