Відбивач струму

Номер патенту: 88148

Опубліковано: 11.03.2014

Автори: Яцик Володимир Євгенійович, Азаров Олексій Дмитрович, Теплицький Михайло Юхимович, Богомолов Сергій Віталійович

Формула / Реферат

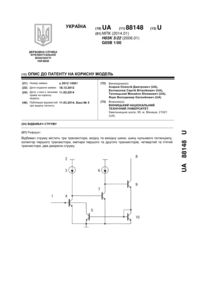

Відбивач струму, що містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною, який відрізняється тим, що у нього введено четвертий та п'ятий транзистори та два джерела струму, причому вхідну шину з'єднано з базою четвертого транзистора, колектор четвертого транзистора з'єднано з другим виводом першого джерела струму, а також з базою п'ятого транзистора, емітер четвертого та п'ятого транзисторів з'єднано з шиною нульового потенціалу, колектор п'ятого транзистора з'єднано з другим виводом другого джерела струму, а також з базою третього транзистора, перший вивід першого та перший вивід другого джерел струму з'єднано з шиною нульового потенціалу.

Текст

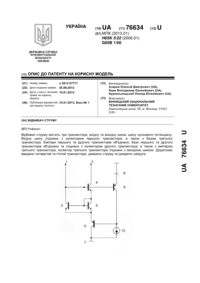

Реферат: Відбивач струму містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, колектор першого транзистора, емітери першого та другого транзисторів, четвертий та п'ятий транзистори, два джерела струму. UA 88148 U (54) ВІДБИВАЧ СТРУМУ UA 88148 U UA 88148 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до аналогової техніки і може бути використана в двотактних підсилювальних схемах. Відомо відбивач струму (Гребен А.Б. Токоотвод с диодным смещением // Гребен А.Б. Проектирование аналоговых интегральных схем. - М.: Энергия, 1976. - с. 74-76), який містить шину нульового потенціалу, вхідну та вихідну шини, два транзистори, причому вхідну шину з'єднано з колектором та базою першого транзистора, а також з базою другого транзистора, емітери першого та другого транзистора з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною. Таким чином схема забезпечує засіб отримання опорного струму, що не залежить від параметрів приборів, проте недоліком є обмежена функціональна можливість. Як найближчий аналог обраний відбивач струму Уілсона (Титце У. Токовое зеркало Вильсона // Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том 1: Пер. с нем. М.: ДМК Пресс, 2008. - с. 342-344), який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною. Недоліком аналога є низька точність роботи пристрою. В основу корисної моделі поставлено задачу створення такого відбивача струму, в якому за рахунок введення нових елементів та зв'язків між ними, підвищується точність роботи, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у відбивач струму, який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною, згідно з корисною моделлю введено четвертий та п'ятий транзистори та два джерела струму, причому вхідну шину з'єднано з базою четвертого транзистора, колектор четвертого транзистора з'єднано з другим виводом першого джерела струму, а також з базою п'ятого транзистора, емітер четвертого та п'ятого транзисторів з'єднано з шиною нульового потенціалу, колектор п'ятого транзистора з'єднано з другим виводом другого джерела струму, а також з базою третього транзистора, перший вивід першого та перший вивід другого джерел струму з'єднано з шиною нульового потенціалу. На кресленні представлено схему відбивача струму. Пристрій мітить вхідну шину 1, яку з'єднано з колектором першого 5 транзистора, емітери першого 5 та другого 10 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 2, бази першого 5 та другого 10 транзисторів об'єднано та з'єднано з колектором другого 10 транзистора, а також з емітером третього 9 транзистора, колектор третього 9 транзистора з'єднано з вихідною шиною 8, вхідну шину 1 з'єднано з базою четвертого 4 транзистора, колектор четвертого 4 транзистора з'єднано з другим виводом першого 3 джерела струму, а також з базою п'ятого 7 транзистора, емітер четвертого 4 та п'ятого 7 транзисторів з'єднано з шиною нульового потенціалу 2, колектор п'ятого 7 транзистора з'єднано з другим виводом другого 6 джерела струму, а також з базою третього 9 транзистора, перший вивід першого 3 та перший вивід другого 6 джерел струму з'єднано з шиною нульового потенціалу 2. Пристрій працює таким чином. Вхідний сигнал у вигляді струму поступає на вхідну шину 1. Якщо вхідний струм збільшується, то четвертий 4 транзистор привідкривається, при цьому збільшується колекторний струм четвертого 4 транзистора, при цьому напруга на колекторі четвертого 4 транзистора падає, при цьому п'ятий 7 транзистор призакривається, при цьому зменшується колекторний струм п'ятого 7 транзистора, при цьому напруга на колекторі п'ятого 7 транзистора збільшується, при цьому третій 9 транзистор привідкривається, при цьому збільшується колекторний та емітерний струм третього 9 транзистора. Збільшення емітерного струму третього 9 транзистора передається через відбивач струму, побудований на першому 5 та другому 10 транзисторах на вхід схеми, тобто збільшується колекторний струм першого 5 транзистора, що компенсує збільшення вхідного струму. Якщо вхідний струм зменшується, то четвертий 4 транзистор призакривається, при цьому зменшується колекторний струм четвертого 4 транзистора, при цьому напруга на колекторі четвертого 4 транзистора зростає, при цьому п'ятий 7 транзистор привідкривається, при цьому 1 UA 88148 U 5 10 15 збільшується колекторний струм п'ятого 7 транзистора, при цьому напруга на колекторі п'ятого 7 транзистора зменшується, при цьому третій 9 транзистор призакривається, при цьому зменшується колекторний та емітерний струм третього 9 транзистора. Зменшення емітерного струму третього 9 транзистора передається через відбивач струму, побудований на першому 5 та другому 10 транзисторах на вхід схеми, тобто зменшується колекторний струм першого 5 транзистора, що компенсує зменшення вхідного струму. Коефіцієнт передачі по струму буде дорівнювати K1 Iв их 1 , і залежить від коефіцієнту Iв х передачі по струму відбивача струму, побудованого на першому 5 та другому 10 транзисторах. Вихідний опір схеми rвих rк Т3 1 T3 , де Т3 - опір колекторного переходу третього 9 к транзистора у схемі із загальним емітером (ЗЕ), T3 - коефіцієнт передачі струму третього 9 транзистора у схемі ЗЕ. Колекторний струм третього 9 транзистора поступає на вихідну шину 8. Перше 3 та друге 6 джерела струму задають робочий струм для роботи четвертого 4, та п'ятого 7 транзисторів відповідно. Шина нульового потенціалу 2 встановлює необхідний рівень напруги для живлення схеми. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 20 25 30 Відбивач струму, що містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною, який відрізняється тим, що у нього введено четвертий та п'ятий транзистори та два джерела струму, причому вхідну шину з'єднано з базою четвертого транзистора, колектор четвертого транзистора з'єднано з другим виводом першого джерела струму, а також з базою п'ятого транзистора, емітер четвертого та п'ятого транзисторів з'єднано з шиною нульового потенціалу, колектор п'ятого транзистора з'єднано з другим виводом другого джерела струму, а також з базою третього транзистора, перший вивід першого та перший вивід другого джерел струму з'єднано з шиною нульового потенціалу. Комп’ютерна верстка О. Рябко Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 2

ДивитисяДодаткова інформація

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych, Teplytskyi Mykhailo Yukhymovych, Yatsyk Volodymyr Yevhenovych

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич, Теплицкий Михаил Ефимович, Яцик Владимир Евгеньевич

МПК / Мітки

Код посилання

<a href="https://ua.patents.su/4-88148-vidbivach-strumu.html" target="_blank" rel="follow" title="База патентів України">Відбивач струму</a>

Попередній патент: Кожух безмастильної муфти

Наступний патент: Відбивач струму

Випадковий патент: Спосіб хірургічного лікування рецидивів уротеліальної карциноми верхніх сечовивідних шляхів