Система розподілу ресурсів при формуванні команд проекту

Номер патенту: 120383

Опубліковано: 25.10.2017

Автори: Доценко Наталія Володимирівна, Павлик Ганна Володимирівна

Формула / Реферат

Система розподілу ресурсів при формуванні команд проекту, яка містить два двійкові лічильники, два блоки пам'яті, виходи результату, групу інформаційних входів, два виходи пристрою, два керуючі входи, два елементи НІ, два елементи І, тригер, k блоків множення векторів, k порогових елементів, причому виходи першого блока пам'яті з'єднані з виходами результату та з першими групами входів блоків множення векторів, вихід тригера з'єднаний з другим виходом та через другий елемент HI з першим входом першого елемента І, перший керуючий вхід з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з підсумовуючим входом першого двійкового лічильника, вихід переносу якого з'єднаний з першим виходом та через перший елемент HI з третім входом першого елемента І, і-та група інформаційних входів з'єднана з другою групою входів і-го блока множення векторів, виходи блоків множення векторів з'єднані з першими групами входів відповідного порогового елемента, виходи яких з'єднані з відповідними входами другого елемента І, вихід якого з'єднаний з входом тригера, другий керуючий вхід з'єднаний з підсумовуючим входом другого двійкового лічильника, виходи якого з'єднані з адресними входами другого блока пам'яті, і-та група виходів другого блока пам'яті з'єднана з другою групою входів і-го порогового елемента, (і = 1,…,k), яка відрізняється тим, що містить суматор, аналізатор вхідних даних, причому виходи першого двійкового лічильника з'єднані з першою групою входів суматора, виходи аналізатора вхідних даних з'єднані з другою групою входів суматора, виходи якого з'єднані з входами першого блока пам'яті.

Текст

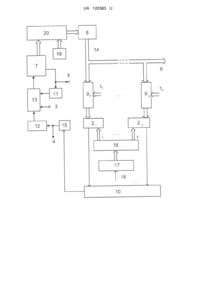

Реферат: Система розподілу ресурсів при формуванні команд проекту містить два двійкові лічильники, два блоки пам'яті, виходи результату, групу інформаційних входів, два виходи пристрою, два керуючі входи, два елементи НІ, два елементи І, тригер, k блоків множення векторів, k порогових елементів. Виходи першого блока пам'яті з'єднані з виходами результату та з першими групами входів блоків множення векторів. Вихід тригера з'єднаний з другим виходом та через другий елемент HI з першим входом першого елемента І, перший керуючий вхід з'єднаний з другим входом першого елемента І. Вихід першого елемента І з'єднаний з підсумовуючим входом першого двійкового лічильника, вихід переносу якого з'єднаний з першим виходом та через перший елемент HI з третім входом першого елемента І, і-та група інформаційних входів з'єднана з другою групою входів і-го блока множення векторів. Виходи блоків множення векторів з'єднані з першими групами входів відповідного порогового елемента, виходи яких з'єднані з відповідними входами другого елемента І, вихід якого з'єднаний з входом тригера, другий керуючий вхід з'єднаний з підсумовуючим входом другого двійкового лічильника, виходи якого з'єднані з адресними входами другого блока пам'яті, і-та група виходів другого блока пам'яті з'єднана з другою групою входів і-го порогового елемента, (і=1,…, k). Додатково введено суматор, аналізатор вхідних даних. При цьому виходи першого двійкового лічильника з'єднані з першою групою входів суматора, виходи аналізатора вхідних даних з'єднані з другою групою входів суматора, виходи якого з'єднані з входами першого блока пам'яті. UA 120383 U (54) СИСТЕМА РОЗПОДІЛУ РЕСУРСІВ ПРИ ФОРМУВАННІ КОМАНД ПРОЕКТУ UA 120383 U UA 120383 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і призначена для розподілу ресурсів при формуванні команд проекту. Відомий діагностичний процесор [Патент України № 49639 A, G06F 11/25. Заявл. 14.01.2002; опубл. 16.09.2002, бюл. № 9], що містить двійковий лічильник, блок пам'яті, виходи результату, групу інформаційних входів, два виходи пристрою, керуючий вхід, два елементи HI, елемент І, тригер. Недоліком відомого пристрою є низька швидкодія. Відома система формування команди проекту [Патент України № 20818, G06F17/00. Заявл. 08.08.2006; опубл. 15.02.2007, бюл. № 2], що містить двійковий лічильник, блок пам'яті, виходи результату, групу інформаційних входів, два виходи пристрою, керуючий вхід, два елементи НІ, два елементи І, тригер, k блоків множення векторів, k порогових елементів. Недоліком відомої системи є низька швидкодія. Найбільш близькою по технічній суті і результату, що досягається, є система формування команди проекту [Патент України № 112224, G06F 17/00. Заявл. 23.05.2016; опубл. 12.12.2016, бюл. № 23], яка має два двійкові лічильники, два блоки пам'яті, виходи результату, групу інформаційних входів, два виходи пристрою, два керуючі входи, два елемента НІ, два елемента І, тригер, k блоків множення векторів, k порогових елементів, причому виходи першого блока пам'яті з'єднані з виходами результату та з першими групами входів блоків множення векторів, вихід тригера з'єднаний з другим виходом та через другий елемент HI з першим входом першого елемента І, перший керуючий вхід з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з підсумовуючим входом першого двійкового лічильника, вихід переносу якого з'єднаний з першим виходом та через перший елемент НІ з третім входом першого елемента І, і-та група інформаційних входів з'єднана з другою групою входів і-го блока множення векторів, виходи блоків множення векторів з'єднані з першими групами входів відповідного порогового елемента, виходи яких з'єднані з відповідними входами другого елемента І, вихід якого з'єднаний з входом тригера, другий керуючий вхід з'єднаний з підсумовуючим входом другого двійкового лічильника, виходи якого з'єднані з адресними входами другого блока пам'яті, і-та група виходів другого блока пам'яті з'єднана з другою групою входів і-го порогового елемента, (і = 1,….,k). Недоліком відомого пристрою є низька швидкодія. В основу корисної моделі поставлено задачу вдосконалити систему шляхом введення нового складу елементів та нової організації взаємозв'язків між ними забезпечити більшу швидкодію. Поставлена задача вирішується тим, що система розподілу ресурсів при формуванні команд проекту, яка містить два двійкові лічильники, два блоки пам'яті, виходи результату, групу інформаційних входів, два виходи пристрою, два керуючі входи, два елементи НІ, два елементи І, тригер, k блоків множення векторів, k порогових елементів, причому виходи першого блока пам'яті з'єднані з виходами результату та з першими групами входів блоків множення векторів, вихід тригера з'єднаний з другим виходом та через другий елемент HI з першим входом першого елемента І, перший керуючий вхід з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з підсумовуючим входом першого двійкового лічильника, вихід переносу якого з'єднаний з першим виходом та через перший елемент НІ з третім входом першого елемента І, і-та група інформаційних входів з'єднана з другою групою входів і-го блока множення векторів, виходи блоків множення векторів з'єднані з першими групами входів відповідного порогового елемента, виходи яких з'єднані з відповідними входами другого елемента І, вихід якого з'єднаний з входом тригера, другий керуючий вхід з'єднаний з підсумовуючим входом другого двійкового лічильника, виходи якого з'єднані з адресними входами другого блока пам'яті, і-та група виходів другого блока пам'яті з'єднана з другою групою входів і-го порогового елемента, (і = 1,…,k), згідно з корисною моделлю, містить суматор, аналізатор вхідних даних, причому виходи першого двійкового лічильника з'єднані з першою групою входів суматора, виходи аналізатора вхідних даних з'єднані з другою групою входів суматора, виходи якого з'єднані з входами першого блока пам'яті. Заявлена система має новий склад елементів та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості. Технічний результат, як наслідок цих властивостей - підвищення швидкодії. На кресленні представлена функціональна схема системи розподілу ресурсів при формуванні команд. Система розподілу ресурсів при формуванні команд проекту містить групу інформаційних входів 1, k порогових елементів 2, два керуючі входи 3, 18, два виходи пристрою 4, 5, виходи результату 6, два двійкові лічильники 7, 17, два блоки пам'яті 8, 16, k блоків множення векторів 1 UA 120383 U 5 10 15 20 25 30 35 40 45 50 55 9, два елементи І 10, 13, два елементи HI 11, 12, тригер 15, аналізатор вхідних даних 19, суматор 20, причому виходи першого блока пам'яті 8 з'єднані з виходами результату 6 та з першими групами входів блоків множення векторів 9, вихід тригера 15 з'єднаний з другим виходом 4 та через другий елемент НІ 12 з першим входом першого елемента І 13, перший керуючий вхід 3 з'єднаний з другим входом першого елемента I 13, вихід першого елемента I 13 з'єднаний з підсумовуючим входом першого двійкового лічильника 7, вихід переносу якого з'єднаний з першим виходом 5 та через перший елемент НІ 11 з третім входом першого елемента І 13, і-та група інформаційних входів 1i з'єднана з другою групою входів і-го блока множення векторів 9i, виходи блоків множення векторів 9 з'єднані з першими групами входів відповідного порогового елемента 2, виходи яких з'єднані з відповідними входами другого елемента І 10, вихід якого з'єднаний з входом тригера 15, другий керуючий вхід 18 з'єднаний з підсумовуючим входом другого двійкового лічильника 17, виходи якого з'єднані з адресними входами другого блока пам'яті 16, і-та група виходів другого блока пам'яті 16 з'єднана з другою групою входів і-го порогового елемента 2і, (і = 1,…,k), виходи першого двійкового лічильника 7 з'єднані з першою групою входів суматора 20, виходи аналізатора вхідних даних 19 з'єднані з другою групою входів суматора 20, виходи якого з'єднані з входами першого блока пам'яті 8. Розглянемо роботу системи. При описі роботи введені такі позначення: η - кількість претендентів, k - кількість робіт; i i i Α ={a 1,…, а n} - двійкове число, що подається на і-ту групу інформаційних входів 1i, причому i i a j=1, якщо j-тий претендент може виконувати і-ту роботу, та a j=0 у іншому випадку; С={с1,…, сn} - двійкове число, на виходах 14 блока пам'яті 8, яке відображує можливий склад команди проекту, причому Ci=1, якщо і-тий претендент входить у склад команди, та Ci=0 у протилежному випадку. Аналізатор вхідних даних 19 визначає мінімальну можливу кількість членів команди для заданих даних і формує на своїх виходах відповідну початкову адресу. У блоці пам'яті 8 записані лексикографічно впорядковані значення двійкових чисел С. На інформаційні входи 1 подаються відповідні значення двійкових чисел А. Спочатку всі елементи пам'яті схеми пристрою знаходяться в стані "0". На другий керуючий вхід 18 подається імпульс і стан другого двійкового лічильника 17 стає "0…01" і на виходах другого блока пам'яті 16 формуються значення для першої групи обмежень. На керуючий вхід 3 подається імпульсна послідовність, при цьому змінюється стан двійкового лічильника 7. Двійкове число на виходах двійкового лічильника 7 додається у суматорі 20 до значень, сформованих аналізатором вхідних даних 19. Двійкове число на виходах суматора 20 є адресою, згідно з якою на виходах 14 блока пам'яті 8 формується відповідне значення числа С. На виходах 16i блока множення векторів 9i формуються двійкові унітарні η-розрядні коди, що і і і відповідають двійковому числу а 1*c1, а 2*c2,…, а n*cn. Порогові елементи 2 формують на своєму виході сигнал "1", якщо двійковий код, що надходить на їх перші входи, не менше двійкового коду, що надходить на їх другі входи. Якщо на виходах усіх порогових елементів сигнал "1", що відповідає наявності рішення, на виході другого елемента І формується сигнал "1", при цьому тригер 15 переходить у стан "1" і на виході 4 формується сигнал "1", що свідчить про наявність рішення. Якщо розглянутий варіант не є рішенням, то наступний імпульс на керуючому вході 3 переведе двійковий лічильник 7 у наступний стан, і на виходах блока пам'яті 8 формується наступний варіант побудови команди проекту. Коефіцієнт рахунку першого двійкового лічильника 7 дорівнює кількості варіантів побудови команди проекту. Якщо перебрані всі варіанти, але рішення немає, то на виході 5 формується сигнал "1", який про це свідчить. Після отримання рішення на другий керуючий вхід 18 подається наступний імпульс. Стан другого двійкового лічильника 17 стає "0…010" і аналогічно розглядається склад команди проекту для другої групи обмежень. Таким чином, система послідовно генерує та аналізує варіанти побудови команди проекту із заданим резервом для різних варіантів обмежень. Пристрій має більшу швидкодію, тому що розглядаються тільки перспективні варіанти рішення задачі. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 60 Система розподілу ресурсів при формуванні команд проекту, яка містить два двійкові лічильники, два блоки пам'яті, виходи результату, групу інформаційних входів, два виходи 2 UA 120383 U 5 10 15 пристрою, два керуючі входи, два елементи НІ, два елементи І, тригер, k блоків множення векторів, k порогових елементів, причому виходи першого блока пам'яті з'єднані з виходами результату та з першими групами входів блоків множення векторів, вихід тригера з'єднаний з другим виходом та через другий елемент HI з першим входом першого елемента І, перший керуючий вхід з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з підсумовуючим входом першого двійкового лічильника, вихід переносу якого з'єднаний з першим виходом та через перший елемент HI з третім входом першого елемента І, і-та група інформаційних входів з'єднана з другою групою входів і-го блока множення векторів, виходи блоків множення векторів з'єднані з першими групами входів відповідного порогового елемента, виходи яких з'єднані з відповідними входами другого елемента І, вихід якого з'єднаний з входом тригера, другий керуючий вхід з'єднаний з підсумовуючим входом другого двійкового лічильника, виходи якого з'єднані з адресними входами другого блока пам'яті, і-та група виходів другого блока пам'яті з'єднана з другою групою входів і-го порогового елемента, (і=1,…, k), яка відрізняється тим, що містить суматор, аналізатор вхідних даних, причому виходи першого двійкового лічильника з'єднані з першою групою входів суматора, виходи аналізатора вхідних даних з'єднані з другою групою входів суматора, виходи якого з'єднані з входами першого блока пам'яті. 3 UA 120383 U Комп’ютерна верстка Г. Паяльніков Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 17/00

Мітки: система, ресурсів, проекту, розподілу, команд, формуванні

Код посилання

<a href="https://ua.patents.su/6-120383-sistema-rozpodilu-resursiv-pri-formuvanni-komand-proektu.html" target="_blank" rel="follow" title="База патентів України">Система розподілу ресурсів при формуванні команд проекту</a>

Попередній патент: Спосіб діагностики розвитку атеросклерозу

Наступний патент: Спосіб виконання горизонтального протифільтраційного екрана

Випадковий патент: Спосіб діагностики розвитку атеросклерозу