Пристрій обчислення швидкого перетворення фур’є

Номер патенту: 41581

Опубліковано: 17.09.2001

Автори: Каплієнко Володимир Сергійович, КУКОЛЬНИЦЬКИЙ АНАТОЛІЙ ПИЛИПОВИЧ

Формула / Реферат

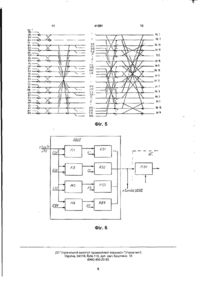

Пристрій для обчислення, швидкого перетворення Фур'є, що містить перший і другий помножувачі, перший і другий оперативні запам'ятовуючі блоки, два постійні запам'ятовуючі блоки і блок керування, причому перший вхід першого помножувача з'єднаний з виходом першого постійного запам'ятовуючого блока, перший вхід другого помножувача з'єднаний з виходом другого постійного запам'ятовуючого блока, керуючі входи першого і третього постійних запам'ятовуючих блоків і першого та другого оперативних запам'ятовуючих блоків з'єднані з виходами блока керування, який відрізняється тим, що він містить два постійні запам'ятовуючі блоки і два мікропроцесорні суматори-накопичувачі, причому вхідна шина пристрою з'єднана з другим входом першого помножувача, вихід якого з'єднаний з інформаційними входами першого і другого оперативних запам'ятовуючих блоків, виходи яких з'єднані з інформаційним входом першого мікропроцесорного суматора-накопичувача, керуючий вхід якого з'єднаний з виходом другого постійного запам'ятовуючого блока, а вихід - з другим входом другого помножувача, вихід якого з'єднаний з інформаційним входом другого мікропроцесорного суматора-накопичувача, керуючий вхід якого з'єднаний з виходом четвертого постійного запам'ятовуючого блока, а вихід є виходом пристрою, керуючі виходи третього і четвертого постійних запам'ятовуючих блоків з'єднані з виходами блока керування.

Текст

Пристрій для обчислення, швидкого перетворення Фур'є, що містить перший і другий помножувачі, перший і другий оперативні запам'ятовуючі блоки, два постійні запам'ятовуючі блоки і блок керування, причому перший вхід першого помножувача з'єднаний з виходом першого постійного запам'ятовуючого блока, перший вхід другого помножувача з'єднаний з виходом другого постійного запам'ятовуючого блока, керуючі входи першого і третього постійних запам'ятовуючих блоків І першого та другого оперативних запам'ятовуючих Пристрій, що пропонується, належить до галузі радіотехніки і може бути використаним у системах обробки сигналів, аналізаторах спектра і т. д. Відомі пристрої для обчислення швидкого перетворення Фур'є (ШПФ) одно- і двопроцесорний цифровий обчислювач ["Л 1 Цифровые фильтры и устройство обработки сигналов на интегральных микросхемах" под редакцией Б Ф Высоцкого. М., Радио и связь, 1984 г., стр114 рис 4 11, стр.120 рис 4.16, стр.126 рис 4 23], недоліком яких є наявність зворотного зв'язку через зберігання результатів проміжних обчислень в основних запам'ятовуючих пристроях, що спричиняє необхідність додаткових комутаторів швидкодіючої оперативної пам'яті і збільшення розрядності основного запам'ятовуючого пристрою, а також велика обмеженість кількості точок, що обробляються ШПФ структурою арифметичних пристроїв і т.д. Суттєвими ознаками аналога і пристрою, що збігаються, є наявність оперативної1 пам'яті, арифметичних пристроїв, помножувачів І постійних запам'ятовуючих пристроїв з коректуючими коефіцієнтами та поворотними множниками. Із відомих рішень найбільш близьким до при блоків з'єднані з виходами блока керування, який відрізняється тим, що він містить два постійні запам'ятовуючі блоки і два мікропроцесорні суматори-накопичувачі, причому вхідна шина пристрою з'єднана з другим входом першого помножувача, вихід якого з'єднаний з інформаційними входами першого і другого оперативних запам'ятовуючих блоків, виходи яких з'єднані з інформаційним входом першого мікропроцесорного суматора-накопичувача, керуючий вхід якого з'єднаний з виходом другого постійного запам'ятовуючого блока, а вихід - з другим входом другого помножувача, вихід якого з'єднаний з інформаційним входом другого мікропроцесорного суматора-нашпичувача, керуючий вхід якого з'єднаний з виходом четвертого постійного запам'ятовуючого блока, а вихід є виходом пристрою, керуючі виходи третього і четвертого постійних запам'ятовуючих блоків з'єднані з виходами блока керування. строю, що заявляється, за технічною сутністю є рішення, наведене в {Л 1 на рис 4 3, ст.103), яке складається з двох надоперативних запам'ятовуючих пристроїв, чотирьох оперативних запам'ятовуючих пристроїв, чотирьох помножувачів, двох постійних запам'ятовуючих пристроїв, пристрою керування і арифметичного пристрою, який складається з надоперативного запам'ятовуючого пристрою, п-'і кількості арифметичних функціональних вузлів та пристрою керування. Недоліками цього рішення є : 1 Зберігання проміжних результатів обчислень в основних оперативних запам'ятовуючих пристроях-ОЗП1 ... ОЗП4. 2 Наявність двох надоперативних запам'ятовуючих пристроїв з комутаторами НОЗП1 та НОЗП2. 3. Необхідність проводити нормування проміжних результатів обчислень арифметичного пристрою (АП) або збільшення розрядності НОЗП1, НОЗП2, ОЗП1 .. ОЗП4 для попередження переповнення. 4. Суттєва обмеженість кількості точок ШПФ, що обробляються структурою АП і алгоритмом об 00 ю 41581 робки, тому що N = r\ де N- кількість точок, що обчислюється ШПФ; г- основа базової операції алгоритму ШПФ (для даної схеми - const); п - ціле позитивне число. 5. Необхідність наявності у складі АП вузла введення-виведення, регістрової пам'яті і комутаторів (Л.1 ст.66, рис 3.2) В основу винаходу поставлено задачу створення пристрою обчислення швидкого перетворення Фур'є (ШПФ) в реальному масштабі часу з програмною зміною кількості фільтрів, що обчислюються, при скороченні об'єму апаратури шляхом' 1. Виключення зберігання проміжних результатів обчислень в ОЗП1...ОЗП4, що виключає необхідність наявності НОЗП1, пристрою введення-виведення, регістрової пам'яті та комутаторів в АП і необхідність нормування проміжних результатів обчислень, а в цілому підвищує точність обчислень І швидкодію усієї системи в цілому без додаткових витрат. 2. Побудови спеціального арифметичного пристрою таким чином, щоб можна було програмно перерозподіляти кількість підсумовувань між частинами АП, тобто програмно змінювати величину г, що дозволяє обчислювати ШПФ з різною кількістю точок із змінним кроком і робить систему більш гнучкою при роботі в реальному масштабі часу: U0JQ _ /V • де N - кількість точок ШПФ, що обчислюються; ( 7 Ж 2 ( * — ) -> РОН2 4; Шостий етап: Аналогічно розраховуються складові сигналів решти непарних фільтрів при восьмиточковому ШПФ. Процес обчислення усіх шістнадцяти складових при восьмиточковому ШПФ проходить за 60 тактів, двадцяти чотирьох складових при дванадцятиточковому ШПФ - за 88 тактів, а тридцяти двох складових при шістнадцятиточковому ШПФ за 128 тактів. 8 Програми роботи мікропроцесорних суматорівнакопичуаачів МП1 і МП2(б,10) і значення поворотних множників для другого помножувача ПМ2(8), необхідні при обчисленні складових парних і непарних фільтрів при різних N, записані у ПЗП2, ПЗПЗ та ПЗП4 (7, 9, 11). Вибір програми обчислення здійснюється поданням команди через пристрій керування і синхронізації на ПЗП2...ПЗП4 (7, 9, 11) Дана структура дозволяє легко реалізувати обробку ШПФ при N= 24, 32, 48 І Т.Д. Якщо tl)IICk/}, 8такт..МП, де Ттакт.МП - період тактової частоти мікропроцесорних суматорі в-н а копичувачіа, то для обчислення усіх складових при N = 8, 12, 16 і т.д. достатньо одного арифметичного пристрою при постійному об'ємі ОЗП. Таким чином, пристрій, що заявляється, має таку структуру, яка дозволяє будувати і розробляти програми для обчислення ШПФ послідовностей, довжина яких No добутком взаємно простих множників, вибраних Із множини {2, 3, 4, 5, 7, 8, 9, 16}. jn 8 40 1— 3 ПІУЗ Фіг. 1 ІС=А+В А-В З С - А • 0,5 0.5. Позначення А, В та С умовні Фіг. 2 и ЛІ 10 41581 Jr, Jr. 1 1 a as \ / г / \ it $t ґ Фіг. З к X X O; £> • /i I, £г lr r ~y/ о —^r X x \\ If ж \/ \. x: C-'.' & li It \T Л \... X л ZT \\W7 W7 У7 \V / // \\ / \ У / \ / П ч\» і. t- / / / X Фіг. 4 \ 7~T 7 11 12 41581 Г7 -17/ T Gt X X. 'a if «^ .tv,—A fe-^v

ДивитисяДодаткова інформація

Автори англійськоюKUKOLNITSKYI ANATOLII PYLYPOVYCH

Автори російськоюКУКОЛЬНИЦКИЙ АНАТОЛИЙ ФИЛИППОВИЧ

МПК / Мітки

МПК: G06F 17/14, G06F 15/00

Мітки: пристрій, фур'є, перетворення, обчислення, швидкого

Код посилання

<a href="https://ua.patents.su/6-41581-pristrijj-obchislennya-shvidkogo-peretvorennya-fureh.html" target="_blank" rel="follow" title="База патентів України">Пристрій обчислення швидкого перетворення фур’є</a>

Попередній патент: Спосіб вимірювання швидкості потоку і пристрій для його реалізації

Наступний патент: Спосіб гри у шахи та пристрій для його реалізації

Випадковий патент: Пристрій захисту приймача