Спосіб двійкового додавання/віднімання

Номер патенту: 83133

Опубліковано: 27.08.2013

Автори: Білик Віктор Кирилович, Клімовська Алла Іванівна, Боюн Віталій Петрович, Палагін Олександр Васильович

Формула / Реферат

Спосіб двійкового додавання/віднімання, що включає формування сигналів напруги одиничної та нульової амплітуд, при якому амплітуди напруги сигналів розрядів двох доданків додають і віднімають, який відрізняється тим, що додатково формують сигнал напруги одиничної амплітуди протилежної полярності, при цьому порівнюють абсолютну величину амплітуди напруги сигналу результату додавання амплітуд з величиною одиничної амплітуди напруги, і, при перевищенні величини амплітуди напруги сигналу результату додавання над одиничною, амплітуду напруги сигналу результату додавання зменшують удвічі до одиничної і приймають це за результат визначення двійкового розряду переносу, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають двійковий розряд переносу нульовим; паралельно з цим порівнюють абсолютну величину амплітуди напруги сигналу результату віднімання з нульовою і, при негативному результаті порівняння, за результат визначення двійкового розряду суми двох доданків приймають щойно одержане одиничне значення амплітуди напруги сигналу результату додавання, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають двійковий розряд суми нульовим.

Текст

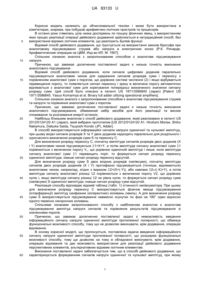

Реферат: Спосіб двійкового додавання/віднімання включає формування сигналів напруги одиничної та нульової амплітуд, при якому амплітуди напруги сигналів розрядів двох доданків додають і віднімають. Додатково формують сигнал напруги одиничної амплітуди протилежної полярності, при цьому порівнюють абсолютну величину амплітуди напруги сигналу результату додавання амплітуд з величиною одиничної амплітуди напруги. При перевищенні величини амплітуди напруги сигналу результату додавання над одиничною, амплітуду напруги сигналу результату додавання зменшують удвічі до одиничної і приймають це за результат визначення двійкового розряду переносу. За результат визначення двійкового розряду суми двох доданків приймають щойно одержане одиничне значення амплітуди напруги сигналу результату додавання, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають двійковий розряд суми нульовим. UA 83133 U (12) UA 83133 U UA 83133 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і може бути використана в комп'ютерах, зокрема, при побудові арифметико-логічних пристроїв та процесорів. В останні роки з’явилась ціла низка досліджень по пошуку фізичних явищ, з використанням яких процес реалізації операції двійкового додавання здійснюється в нетрадиційний спосіб, без використання відомих логічних елементів, що реалізують Булеві функції. Відомий спосіб двійкового додавання, що ґрунтується на використанні законів Кірхгофа при аналоговому підсумовуванні струмів або напруги в електричних колах [Р.К. Ричарде. Арифметические операции на ЦВМ. Изд-во ИЛ. М. 1957]. Спільною ознакою аналога з запропонованим способом є аналогове підсумовування напруги. Причиною, що заважає досягненню поставленої задачі є низька точність виконання аналогового підсумування. Відомий спосіб двійкового додавання, коли сигнали цифрових доданків паралельно підсумовуються аналоговим чином для одержання сигналів розрядів суми і переносу з порівнянням аналогової суми з порогом, що дорівнює системі числення (2) і якщо відбувається перевищення порогу, то появляється сигнал переносу і зразу ж величина порогу автоматично віднімається з аналогової суми для корегування попередньо визначеного значення сигналу розряду суми. Цей спосіб було описано в патенті US 1971/3586845 (Japan) [Patent US 1971/3586845. Yasuo Komamiya et al. Binary full adder utilizing operational amplifiers]. Спільною ознакою аналога з запропонованим способом є аналогове підсумовування струмів та напруги та порівняння аналогової суми з порогом. Причиною, що заважає досягненню поставленої задачі є низька точність виконання аналогового підсумовування, обмежений набір засобів для його реалізації та високе споживання та розсіювання енергії останніх. Найбільш близьким аналогом є спосіб двійкового додавання, який реалізовано в патенті US 2012/0124120 A1 (Japan), який вибрано прототипом [US 2012/0124120 A1. Hirofumi Morise, Shiho Nakamura, Dalsuke Saida, Tsuyoshi Kondo (JP), Adder]. В способі використовуються інформаційні сигнали напруги одиничної та нульової амплітуд, при цьому вхідні сигнали розрядів X та Y двох доданків надходять паралельно для роздільного і одночасного визначення розрядів суми S та переносу С. Для визначення розряду переносу С, спочатку амплітуди сигналів розрядів двох доданків (X і Y) аналоговим чином підсумовуються 1=X+Y, a потім амплітуда сигналу аналогової суми 1 порівнюється з величиною порогу V1, що дорівнює одиночній амплітуді і лише, коли амплітуда сигналу аналогової суми 1 перевищить поріг, то формується сигнал розряду переносу одиничної амплітуди, інакше сигнал розряду переносу відсутній. Для визначення розряду суми S двох вхідних розрядів (напівсуми), спочатку амплітуди сигналів двох розрядів доданків (X і Y) протифазно підсумовуються (точніше, віднімаються) аналоговим чином, наприклад, згідно з виразом 2=(Х+(-Y)), або навпаки 2=((-Х)+Y), а потім амплітуда сигналу аналогової різниці 2 порівнюється з величиною порогу V2, що дорівнює нулю і, якщо амплітуда сигналу різниці 2 не рівна нулю, то формується сигнал розряду суми (напівсуми) S одиничної амплітуди, інакше сигнал розряду суми відсутній. Реалізація способу відповідає відомій таблиці (табл. 1) істинності напівсуматора. При цьому для визначення розряду переносу С використовується фізичне явище підсумовування (інтерференції) амплітуд синфазних (когерентних) коливань (хвиль). А для визначення розряду суми S використовується підсумовування навмисно зсунутих по фазі на 180° один відносно одного первісно синхронних коливань. Спільними ознаками запропонованого способу з найближчим аналогом є аналогове підсумовування амплітуд напруги сигналів та порівняння результатів підсумовування зі значеннями порогів. Причиною, що заважає досягненню поставленої задачі є неможливість введення інформаційного сигналу напруги одиничної амплітуди протилежної полярності, що обмежує функціональні можливості способу, тому що не дозволяє виконувати, крім додавання, операцію віднімання. В основу корисної моделі, що пропонується, поставлена задача введення інформаційного сигналу напруги одиничної амплітуди протилежної полярності, що розширює функціональні можливості способу, тому що дозволяє на тому ж обладнанні виконувати, крім додавання, операцію віднімання та дає можливість використання для реалізації двійкового додавання перспективних елементів, альтернативних відомим логічним елементам. Виконання поставленої задачі забезпечується тим, що в способі двійкового додавання, що характеризується формуванням сигналів напруги одиничної та нульової амплітуд, при якому 1 UA 83133 U 5 10 15 20 25 30 35 40 45 амплітуди напруги сигналів розрядів двох доданків додають і віднімають, додатково формують сигнал напруги одиничної амплітуди протилежної полярності, при цьому порівнюють абсолютну величину амплітуди напруги сигналу результату додавання амплітуд з величиною одиничної амплітуди напруги, і, при перевищенні величини амплітуди напруги сигналу результату додавання над одиничною, амплітуду напруги сигналу результату додавання зменшують удвічі до одиничної і приймають це за результат визначення розряду переносу, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають розряд переносу нульовим; паралельно з цим, порівнюють абсолютну величину амплітуди напруги сигналу результату віднімання з нульовою і, при негативному результаті порівняння, за результат визначення розряду суми двох доданків приймають щойно одержане одиничне значення амплітуди напруги сигналу результату додавання, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають розряд суми нульовим. Відмітними ознаками запропонованого способу є те, що додатково формують сигнал напруги одиничної амплітуди протилежної полярності, при цьому порівнюють абсолютну величину амплітуди напруги сигналу результату додавання амплітуд з величиною одиничної амплітуди напруги, і, при перевищенні величини амплітуди напруги сигналу результату додавання над одиничною, амплітуду напруги сигналу результату додавання зменшують удвічі до одиничної і приймають це за результат визначення розряду переносу, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають розряд переносу нульовим; паралельно з цим, порівнюють абсолютну величину амплітуди напруги сигналу результату віднімання з нульовою і, при негативному результаті порівняння, за результат визначення розряду суми двох доданків приймають щойно одержане одиничне значення амплітуди напруги сигналу результату додавання, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають розряд суми нульовим. Введення додатково нових ознак розширює функціональні можливості способу, тому що дозволяє на тому ж обладнанні виконувати, крім додавання, операцію віднімання та відкриває можливості використання для реалізації двійкового додавання перспективних елементів, альтернативних відомим логічним елементам, наприклад, енергоощадних елементів з електромеханічним переносом електронів та інших. Спосіб двійкового додавання/віднімання, що характеризується формуванням сигналів напруги одиничної амплітуди позитивної і негативної полярності та сигналів нульової амплітуди, передбачає виконання наступних дій: амплітуди напруги сигналів розрядів двох доданків паралельно додають і віднімають, а потім порівнюють абсолютну величину амплітуди напруги сигналу результату додавання з величиною одиничної амплітуди напруги, і, лише при перевищенні величини амплітуди напруги сигналу результату додавання над одиничною, амплітуду напруги сигналу результату додавання зменшують удвічі до одиничної і приймають це за результат визначення розряду переносу, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають розряд переносу нульовим; паралельно (разом) з цим, порівнюють абсолютну величину амплітуди напруги сигналу результату віднімання з нульовою і, лише при негативному результаті порівняння, за результат визначення розряду суми двох доданків приймають щойно одержане одиничне значення амплітуди напруги сигналу результату додавання, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають розряд суми нульовим. Результати виконання дій згідно з запропонованим способом двійкового додавання зведено в табл. 2. Сигнали напруги одиничної амплітуди позитивної або негативної полярності та сигнали нульової амплітуди, що відповідають значенню "+1" або "-1" та "0", відповідно, двійкових 1 Xi Yi віднімання розрядів X i , і Y i , двох доданків, синхронно подають для додавання 50 2 Xi Y i їх амплітуд. Потім порівнюють абсолютну величину амплітуди напруги сигналу результату додавання Xi Y i з величиною одиничної амплітуди напруги. 2 UA 83133 U Xi Y i 1 Лише у разі (див. варіанти 4, 9 в табл. 2), коли значення амплітуди напруги сигналу результату аналогового підсумовування помітно перевищить рівень значення напруги, що відповідає значенню логічної одиниці, амплітуду напруги сигналу результату додавання 1 Xi Yi 5 зменшують удвічі до одиничної і приймають це за результат визначення двійкового розряду переносу C 1 Xi Yi / 1 2 , відповідно з полярністю сигналу Xi Yi 0 результату додавання ("+1" для варіанта 4 і "-1" для варіанта 9). При цьому різниця . В усіх інших випадках приймають розряд двійкового переносу нульовим, С=0. Разом з тим порівнюють абсолютну величину амплітуди напруги сигналу результату Xi Y i 10 віднімання з величиною нульової амплітуди напруги. І лише, коли значення амплітуди напруги сигналу результату аналогового віднімання 2 Xi Yi 0 , тобто, лише при негативному результаті порівняння, за результат визначення двійкового розряду суми S двох доданків приймають щойно одержане одиничне значення 15 S 1 Xi Yi / 1 амплітуди напруги сигналу результату додавання , відповідно з полярністю сигналу результату додавання (див. варіанти 2, 3 і 5, 6 в табл. 2). В усіх інших випадках приймають розряд двійкової суми нульовим, S=0, тому що: |2|=0 у варіантах 1, 4, 9, а в варіантах 7, 8 сума 1=0. Наведене вище виконання послідовності дій підтверджує вірність здійснення операції двійкового додавання/віднімання для всіх варіантів комбінацій значень амплітуд напруги сигналів, що відповідають значенням вхідних двійкових доданків. 20 Таблиця 1 Варіант 1 2 3 4 X 0 1 0 1 Y 0 0 1 1 S 0 1 1 0 С 0 0 0 1 Таблиця 2 Вхідне Вхідне Додавання Віднімання Порівняння Порівняння Вихідне Вихідне значення значення ампулітуд ампулітуд ампулітуд ампулiтуд значення значення Варіант сигналів ампулітуди ампулітуди ампулітуди ампулітуди сигналів сигналів сигналів сигналу Х сигналу Y X+Y=1 сигналу S сигналу С X-Y=2 |1|>1 |2|≠0 1 0 0 0 0 0 0 0 0 2 1 0 1 1 0 1 1 0 3 0 1 1 -1 0 1 1 0 4 1 1 2 0 1 0 0 1 5 -1 0 -1 -1 0 1 -1 0 6 0 -1 -1 1 0 1 -1 0 7 1 -1 0 2 0 1 0 0 8 -1 1 0 -2 0 1 0 0 9 -1 -1 -2 0 1 0 0 -1 3 UA 83133 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 Спосіб двійкового додавання/віднімання, що включає формування сигналів напруги одиничної та нульової амплітуд, при якому амплітуди напруги сигналів розрядів двох доданків додають і віднімають, який відрізняється тим, що додатково формують сигнал напруги одиничної амплітуди протилежної полярності, при цьому порівнюють абсолютну величину амплітуди напруги сигналу результату додавання амплітуд з величиною одиничної амплітуди напруги, і, при перевищенні величини амплітуди напруги сигналу результату додавання над одиничною, амплітуду напруги сигналу результату додавання зменшують удвічі до одиничної і приймають це за результат визначення двійкового розряду переносу, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають двійковий розряд переносу нульовим; паралельно з цим порівнюють абсолютну величину амплітуди напруги сигналу результату віднімання з нульовою і, при негативному результаті порівняння, за результат визначення двійкового розряду суми двох доданків приймають щойно одержане одиничне значення амплітуди напруги сигналу результату додавання, відповідно з полярністю сигналу результату додавання, а в усіх інших випадках приймають двійковий розряд суми нульовим. Комп’ютерна верстка Л. Бурлак Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod of binary addition/subtraction

Автори англійськоюPalahin Oleksandr Vasyliiovych, Boiun Vitalii Petrovych, Klimovska Alla Ivanivna, Bilyk Viktor Kyrylovych

Назва патенту російськоюСпособ двоичного сложения/вычитания

Автори російськоюПалагин Александр Васильевич, Боюн Виталий Петрович, Климовская Алла Ивановна, Билык Виктор Кириллович

МПК / Мітки

МПК: G06J 1/00, G06F 7/502, H03H 9/00

Мітки: двійкового, спосіб

Код посилання

<a href="https://ua.patents.su/6-83133-sposib-dvijjkovogo-dodavannya-vidnimannya.html" target="_blank" rel="follow" title="База патентів України">Спосіб двійкового додавання/віднімання</a>

Попередній патент: Пристрій для огляду стінок свердловини

Наступний патент: Двійковий суматор

Випадковий патент: Об'ємна заготівка для відновлення зношеної п'яти ковша екскаватора