Числоімпульсний множильний пристрій

Номер патенту: 107811

Опубліковано: 24.06.2016

Автори: Николайчук Ярослав Миколайович, Давлетова Аліна Ярославівна, Возна Наталія Ярославівна, Круліковський Борис Борисович

Формула / Реферат

Числоімпульсний множильний пристрій, що містить першу і другу вхідні шини, лічильник і помножувач, який відрізняється тим, що додатково введені перша і друга групи K модульних лічильників у базисі Хаара-Крестенсона, група K модульних матричних перемножувачів, перша вхідна шина з'єднана з входами першої групи модульних лічильників, друга вхідна шипа з'єднана з входами другої групи модульних лічильників, виходи яких підключені до відповідних входів додатково введених матричних перемножувачів, другі входи яких підключені до виходів відповідних модульних лічильників першої групи, а виходи підключені до входів додатково введеного шифратора, виходи якого є виходами пристрою.

Текст

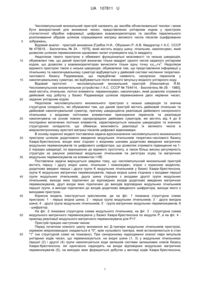

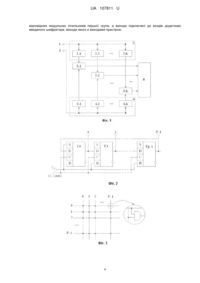

Реферат: Числоімпульсний множильний пристрій містить першу і другу вхідні шини, лічильник і помножувач. Додатково введені перша і друга групи K модульних лічильників у базисі ХаараКрестенсона, група K модульних матричних перемножувачів, перша вхідна шина з'єднана з входами першої групи модульних лічильників, друга вхідна шипа з'єднана з входами другої групи модульних лічильників, виходи яких підключені до відповідних входів додатково введених матричних перемножувачів, другі входи яких підключені до виходів відповідних модульних лічильників першої групи, а виходи підключені до входів додатково введеного шифратора, виходи якого є виходами пристрою. UA 107811 U (12) UA 107811 U UA 107811 U 5 10 15 20 25 30 35 40 45 50 55 Числоімпульсний множильний пристрій належить до засобів обчислювальної техніки і може бути використаний для множення чисел, представлених унітарним кодом у пристроях статистичної обробки інформації, цифрових взаємокореляторах та засобах паралельного розпізнавання образів шляхом опрацювання матриці великого числа пікселів оцифрованих зображень. Відомий аналог - пристрій множення [Грибок Н.И., Обуханич Р.-А.В. Квадратор // А.С. СССР № 475619. - Бюллетень № 24. - 1975], який містить вхідну шину, лічильник, накопичувач, який дозволяє шляхом перемноження однакових чисел отримувати код їх квадрату. Недоліком такого пристрою є обмежені функціональні можливості та низька швидкодія, обумовлені тим, що даний пристрій визначає тільки квадрат одного числа заданого унітарним 2 кодом, що дозволяє у взаємокореляторах вичислити тільки одну точку хiхi+0=х . Недоліком відомого пристрою також є низька швидкодія, обумовлена тим, що представлення інформації у лічильнику та накопичувальному суматорі відбувається у двійковій системі числення теоретикочислового базису Радемахера, що передбачає наявність наскрізних переносів у накопичувальному суматорі, які відбуваються після кожного імпульсу вхідного унітарного коду. Відомий прототип - числоімпульсний множильний пристрій [Николайчук Я.М. Числоимпульсное множительное устройство // А.С. СССР № 754414, - Бюллетень № 29. - 1980], який містить лічильник, логічні елементи, перемножувач, накопичувач, який дозволяє отримати двійковий код добутку у базисі Радемахера шляхом перемноження двох нерівних чисел, заданих унітарним кодом. Недоліком числоімпульсного множильного пристрою є низька швидкодія та значна структурна складність, які обумовлені тим, що даний пристрій містить двійковий лічильник та двійковий накопичувальний суматор, причому швидкодіюча реалізація двійкового синхронного лічильника з вхідними логічними елементами прискорення переносів та реалізація накопичувача на основі повних однорозрядних двійкових суматорів, які містять від 4 до 6 послідовно включених логічних елементів, характеризується низькою швидкодією та значною структурною складністю, що обмежує можливість реалізації їх великого числа в мікроелектронному кристалі матриці пікселів цифрової відеокамери. В основу корисної моделі поставлена задача вдосконалення числоімпульсного множильного пристрою шляхом додаткового введення модульних лічильників теоретико-числового базису Хаара-Крестенсона, входи яких з'єднані з вхідними шинами додатково введених матричних модульних перемножувачів та цифрового шифратора, що дозволяє отримати підвищення на 12 порядки швидкодії, по відношенню до відомого прототипу, а також більш високу регулярність структури за рахунок реалізації модульних лічильників па регістрах зсуву та матричних модульних перемножувачів на елементах І-НЕ. Поставлена задача вирішується завдяки тому, що числоімпульсний множильний пристрій містить першу і другу вхідні шини, лічильник і помножувач, згідно з корисною моделлю, додатково введені перша і друга групи K модульних лічильників у базисі Хаара-Крестенсона, група K модульних матричних перемножувачів, перша вхідна шина з'єднана з входами першої групи модульних лічильників, друга шина з'єднана з входами другої групи модульних лічильників, виходи яких підключені до відповідних входів додатково введених матричних перемножувачів, другі входи яких підключені до виходів відповідних модульних лічильників першої групи, а виходи підключені до входів додатково введеного шифратора, виходи якого є виходами пристрою. Корисна модель ілюструється кресленням, де на фіг. 1 показана структурна схема пристрою: 1 - перша вхідна шина; 2 - перша група модульних лічильників; 3 - друга вихідна шина; 4 - друга група модульних лічильників; 5 - група матричних модульних перемножувачів; 6 - шифратор. На фіг. 2 показана структурна схема модульного лічильника, на фіг. 3 - структурна схема модульного матричного перемножувача у базисі Хаара-Крестенсона по модулю Р, а на фіг. 4 приклад реалізації модульного матричного перемножувача для P=7. Пристрій працює наступним чином: Перед початком кожного циклу множення всі Д-тригери модульних лічильників пристрою, окремою мікрокомандою скидаються в "0", крім нульового тригера, який встановлюється в стан "1" (на структурній схемі не показано). При синхронному надходженні кожної пари імпульсів унітарних кодів чисел, що перемножуються, на вхідні шини (1, 3) у модульних лічильниках першої (2) і другої (4) групи накопичуються коди залишків системи залишкових класів базису Хаара-Крестенсона, які одночасно надходять на входи відповідних модульних матричних перемножувачів (5), на виходах яких формуються добутки у вигляді кодів Хаара-Крестенсона, 1 UA 107811 U згідно виразу ai bi mod Pi di ; i 1, k , де ai та bi поточні залишки чисел X та Y згідно виразів 5 10 15 20 ai res Xmod Pi ; bi res Ymod Pi . Після закінчення циклу перемноження на виході матричних модульних перемножувачів (5) формується код добутку d1, d2 ,...di ,...dk у системі числення залишкових класів базису Крестенсона, який шифратором (6) перетворюється у двійковий код базису Радемахера. Принцип роботи пристрою полягає у тому, що в числоімпульсному множильному пристрої унітарні коди паралельно записуються у модульні лічильники системи залишкових класів теоретико-числового базису Хаара-Крестенсона, паралельно перемножуються у матричних модульних перемножувачах, а результати дешифруються з системи залишкових класів в двійкову систему числення. При цьому, як показано на фіг. 2 модульний лічильник базису Хаара-Крестенсона реалізується на основі регістра зсуву на Д-тригерах зі зворотним зв'язком TP1 T0 . На початку циклу перемноження мікрокомандою у0 всі Д-тригери T1 TP1 по R-входах встановлені в стан "0", а тригер Т 0 по S-входу в стан "1". У процесі надходження імпульсів унітарного коду на вхідну шину, яка з'єднана з С-входами синхронізації всіх Д-тригерів на прямих виходах тригерів формуються модульні коди залишків aj,bj Хаара-Крестенсона з розрядністю Рі. Таким чином у процесі надходження вхідних імпульсів унітарного коду на модульні лічильники на їх виходах з часовою затримкою 2, де - тактова частота переключення логічних елементів кристала на якому реалізується пристрій. Структура модульного матричного перемножувача, на входи якого надходять коди ХаараКрестенсона з першої і другої груп модульних лічильників забезпечує виконання операції модульного множення також за інтервал часу 2 згідно таблиці та структури показаної на фіг. 4 для Р=7. P7 ai bi 0 1 2 3 4 5 6 0 1 2 3 4 5 6 0 0 0 0 0 0 0 0 1 2 3 4 5 6 0 2 4 6 1 3 5 0 3 6 2 5 1 4 0 4 1 5 2 6 3 0 5 3 1 6 4 2 0 6 5 4 3 2 1 25 30 35 40 Приклад реалізації модульного матричного перемножувача для Р=7, показаний на фіг. 4, швидкодія якого визначається двома послідовно включеними логічними інвенторами, що складає 2. Таким чином швидкодія числоімпульсного множильного пристрою згідно корисної моделі визначається затримкою сигналів внаслідок переключення елементів матричного модульного лічильника (л), модульного матричного перемножувача (п) та шифратора л п 2 2 2 6 . Швидкодія відомого пристрою-прототипу визначається сумарною швидкодією переключення Ж-тригерів двійкового лічильника, мультиплексора та накоплюючого суматора, який складається з двійкового багаторозрядного суматора на основі повних трьохвходових однорозрядних суматорів з часом переключення 4-6 [Круліковський Б.Б. Архітектура високопродуктисних матричних прискорювачів операції множення у базисах Радемахера та Хаара / Б.Б. Круліковський, А.Я. Давлетова, В.Л. Кімак, І.Б. Албанський / Праці міжнародної наукової школи-семінару "Питання оптимізації обчислень (ПОО-XLII)" Київ: Інститут кібернетики n імені В.М. Глушкова ПАН України, 2015. - С.47-49]. а такое 2n наскрізних переносів при 2 розрядних унітарних кодів перемножуваних чисел. Тобто л м р 2nc . 8 45 Наприклад при діапазоні кодування вхідних чисел унітарним кодом 2 швидкодія відомого пристрою буде визначатися наступним чином 4 2 2 2 8 4 72 , в той час як у пристрою згідно корисної моделі швидкодія складає 6 не залежно від розрядності вхідних унітарних кодів перемножуваних чисел. 2 UA 107811 U 5 Розрахунок системи взаємнопростих модулів P1,P2 ,..., Pi ,..., Pk . для числоімпульсного множильного пристрою при k 8 виконується виходячи з умови, що добуток модулів P1,P2 ,..., Pi ,..., Pk повинен перевищувати числове значення 216 . Цій умові відповідає наступний набір модулів системи залишкових класів базису Крестенсона 16 . Таким чином на виходах матричних модульних 7, 8, 9, 11, 13 72072 2 65536 перемножувачів, після завершення процесу множення, формується код Хаара-Крестенсона d1, d2 ,..., d5 , який дешифрується у 16-розрядний двійковий код базису Радемахера. Приклад: Нехай перемножуються числа X 100 , Y 200 ; X Y 20000. Числа Х та Y представляться у базисі Хаара-Крестенсона наступним кодом: 10 15 20 25 Сформовані таким чином коди надходять на входи i-тих матричних модульних перемножувачів, на виходах яких формується код Хаара-Крестенсона результатів перемноження d1, d2 ,..., dk згідно виразу: ai bi mod Pi di . що відповідає дешифрованому значенню 20 000 у двійковій системі числення базису Радемахера 100111000100000. Для спрощення структури шифратора (6) він реалізується по двокаскадный схемі, де в першому каскаді коди Хаара-Крестенсона по кожному модулю перетворюються в двійкові коди Радемахера, які в другому каскаді перетворюються в позиційний код двійкової системи числення, тобто 48-бітний код Хаара-Крестенсона дешифрується у 18-бітний код РадемахераКрестенсона та 16-бітний код Радемахера. При цьому в шифраторі (6) затримка сигналів складає 4 і загальна швидкодія пристрою буде складати 6+2=8. Технічний результат: пристрій згідно корисної моделі характеризується підвищеною на 1-2 порядки швидкодією відносно відомого прототипу, а також більш високою регулярністю структури за рахунок реалізації модульних лічильників на регістрах зсуву, та матричних модульних перемножувачів на елементах І-НЕ. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 30 35 Числоімпульсний множильний пристрій, що містить першу і другу вхідні шини, лічильник і помножувач, який відрізняється тим, що додатково введені перша і друга групи K модульних лічильників у базисі Хаара-Крестенсона, група K модульних матричних перемножувачів, перша вхідна шина з'єднана з входами першої групи модульних лічильників, друга вхідна шипа з'єднана з входами другої групи модульних лічильників, виходи яких підключені до відповідних входів додатково введених матричних перемножувачів, другі входи яких підключені до виходів 3 UA 107811 U відповідних модульних лічильників першої групи, а виходи підключені до входів додатково введеного шифратора, виходи якого є виходами пристрою. 4 UA 107811 U Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/38

Мітки: числоімпульсний, множильний, пристрій

Код посилання

<a href="https://ua.patents.su/7-107811-chisloimpulsnijj-mnozhilnijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Числоімпульсний множильний пристрій</a>

Попередній патент: Кузов вантажного транспортного засобу з шиберним бортом

Наступний патент: Прилад для вимірювання температури стінки сушильного циліндра

Випадковий патент: Спосіб визначення повзучості матеріалів при індентуванні