Пристрій для моделювання нейрона

Номер патенту: 27751

Опубліковано: 12.11.2007

Автори: Кожем'яко Андрій Вікторович, Кожем'яко Володимир Прокопович, Мартинюк Тетяна Борисівна, Мороз Ірина Віталіївна

Формула / Реферат

Пристрій для моделювання нейрона, який містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, і логічний блок, який відрізняється тим, що в нього введено комутатор, причому встановлювальний вхід і перший керуючий входи пристрою з'єднані з відповідними входами n блоків зміни синаптичних ваг, вхід скидання і адресний вхід пристрою з'єднані з відповідними входами суматора і логічного блока, перший вихід суматора з'єднаний з інформаційним входом комутатора, а його другий вихід з'єднаний з інформаційним входом логічного блока, вихід ознаки нуля суматора є виходом сигналу "Кінець" пристрою і з'єднаний з керуючим входом комутатора, вихід якого є інформаційним виходом результату пристрою, вхід порога і другий керуючий вхід пристрою з'єднані з відповідними входами логічного блока, вихід якого є виходом результуючого сигналу пристрою.

Текст

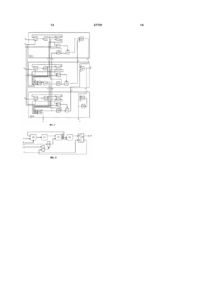

Пристрій для моделювання нейрона, який містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, і логічний блок, який відрізняється тим, що в 3 27751 Недоліком даного пристрою є його недостатня швидкодія через послідовний принцип оброблення n операндів в суматорі, який є його базовим блоком. В основу корисної моделі поставлена задача створення пристрою для моделювання нейрона, в якому введення нових вузлів та зв'язків дозволяє збільшити рівень паралелізму оброблення операндів у суматорі, що збільшить швидкодію пристрою. Поставлена задача досягається тим, що у пристрій для моделювання нейрона, який містить n блоків зміни синаптичних ваг, суматор, перші n вход із якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, логічний блок, введено комутатор, причому установний вхід і перший керуючий входи пристрою з'єднані з відповідними входами n блоків зміни синаптичних ваг, вхід скидання і адресний вхід пристрою з'єднані з відповідними входами суматора і логічного блока, перший вихід суматора з'єднаний з інформаційним входом комутатора, а його другий ви хід з'єднаний з інформаційним входом логічного блока, вихід ознаки нуля суматора є виходом сигналу „Кінець" пристрою і з'єднаний з керуючим входом комутатора, вихід якого є інформаційним виходом результату пристрою, вхід порогу і другий керуючий вхід пристрою з'єднані з відповідними входами логічного блока, вихід якого є ви ходом результуючого си гналу пристрою. На Фіг.1 приведена структурна схема пристрою; на Фіг.2 - структурна схема блока зміни синаптичних ваг; на Фіг.3 - структурна схема суматора; на Фіг.4 - структурна схема логічного блока. Пристрій для моделювання нейрона (Фіг.1) містить дві групи інформаційних входів 11,...,1n і 21,...,2n пристрою, n блоків 31,...,3n зміни синаптичних ваг, установний вхід 4 і керуючий вхід 5 пристрою, суматор 6, вхід 7 скидання та адресний вхід 8 пристрою, комутатор 9, логічний блок 10, вхід 11 порогу, керуючий вхід 12, вихід 13 сигналу „Кінець", інформаційний вихід 14 результату і вихід 15 результуючого сигналу пристрою. Групи інформаційних входів 11,...,1n і 21,...,2n пристрою підключені відповідно до першого і другого входів блоків 31,...,3n зміни синаптичних ваг, третій і четвертий входи яких з'єднані відповідно з установним входом 4 і керуючим входом 5 пристрою. Група виходів 161,...,16n блоків 31,...,3 n зміни синаптичних ваг підключена до п входів суматора 6, вихід 17 якого з'єднаний з інформаційним входом логічного блока 10, вихід 18 з'єднший з інформаційним входом комутатора 9, а вихід ознаки нуля суматора 6 є виходом 13 сигналу „Кінець" пристрою і з'єднаний з керуючим входом комутатора 9. Вхід 7 скидання і адресний вхід 8 пристрою з'єднані з відповідними входами суматора 6 і логічного блока 10, вихід якого є виходом 15 результуючого сигналу пристрою. Вхід 11 порогу і керуючий вхід 12 пристрою з'єднані з відповідними входами логічного блока 10, а вихід комутатора 9 є інформаційним виходом 14 результату пристрою. 4 , Кожний блок 3i, i = 1 n , зміни синаптичних ваг (Фіг.2) містить помножувальний елемент 19, перший вхід якого з'єднаний з інформаційним входом 1i пристрою, а його вихід є ви ходом 16i відповідного блока 3i зміни синаптичних ваг, мультиплексор 20, перший вхід якого з'єднаний з інформаційним входом 2i пристрою, а другий вхід з'єднаний з прямим виходом D-тригера 21. D-вхід D-тригера 21 з'єднаний з установним входом 4 пристрою, а відповідний керуючий вхід 5 пристрою з'єднаний з адресним входом мультиплексора 20, інформаційний вихід якого з'єднаний з другим входом помножувального елемента 19. Суматор 6 (Фіг.3) містить n комірок 22, причому і-та комірка містить мультиплексор 23, регістр 24, арифметично-логічний пристрій (АЛП) 25, суматор 26, D-тригер 27, мініматор 28, два регістри 29, 30, комутатор 31. Перший інформаційний вхід мультиплексора 23 з'єднаний з входом 16i і-ої комірки 22, керуючий вхід з'єднаний з адресним входом 8 пристрою, а його вихід підключено до входу 32 регістра 24, у якого вихід з'єднаний з прямим входом 33 АЛП 25 та інформаційним входом 34 мініматора 28. Вихід регістра 30 з'єднаний з інформаційним входом комутатора 31 та інверсним входом 35 АЛП 25, вихід 36 якого з'єднаний з другим інформаційним входом мультиплексора 23, а вихід 37 знака АЛП 25 з'єднаний зі знаковим входом 38 мініматора 28 і D-входом D-тригера 27, вхід скидання якого з'єднаний з входом 7 скидання пристрою, а його інверсний вихід з'єднаний з керуючим входом комутатора 31. Вихід комутатора 31 підключено до виходу 39 і-ої комірки 22, крім того, інформаційний вхід 40 мініматора 28 і-ої комірки 22 з'єднаний з виходом 41 (і-1)-ої комірки 22, вхід 42 суматора 26 і-ї комірки 22 з'єднаний з виходом 43 (і-1)-ої комірки 22, а вхід 44 підключено до виходу 39 (і+1)-ої комірки 22, вихід суматора 26 (n-1)-ої комірки є виходом 17 суматора і виходом 43 (n-1)ої комірки 22. В і-й комірці 22 вхід регістра 30 підключено до входу 45 і-ої комірки 22, вихід 46 мініматора 28 з'єднаний з входом регістра 29 цієї комірки, інформаційний вихід якого є виходом 41 іої комірки 22, а вихід знака якого є виходом 47 і-ої комірки 22, який з'єднаний зі знаковим входом 48 мініматора 28 (і+1)-ої комірки 22, вихід 46 мініматора 28 n-ої комірки 22 підключений до входів 45 всіх (n-1) молодших комірок 22. Перша комірка 22 не містить мініматор 28 та регістр 29, вихід її регістра 24 є виходом 41 першої комірки 22, вихід 37 знака АЛП 25 є її вк. кодом 47, а вхід 42 суматора 26 з'єднаний з виходом комутатора 31 цієї ж комірки 22. Остання n-на комірка 22 містить регістр 49, вхід якого з'єднаний з виходом суматора 26 n-ої комірки 22, а його вихід є виходом 18 суматора і з'єднаний також з входом 44 суматора 26 цієї ж комірки 22. Вихід 46 мініматора 28 n-ої комірки 22 з'єднаний з входом регістра 30 цієї комірки, а вихід ознаки нуля мініматора 28 n-ої комірки 22 з'єднаний з виходом ознаки нуля суматора 6 і є ви ходом 13 сигналу „Кінець" пристрою. 5 27751 Логічний блок 10 (Фіг.4) містить мультиплексор 50, регістр 51, комутатор 52, АЛП 53, елемент АБО 54, RS-тригер 55, елемент І 56. Адресний вхід мультиплексора 50 з'єднаний з адресним входом 8 пристрою, його перший інформаційний вхід з'єднаний з входом 11 порогу пристрою, а його вихід з'єднаний з входом регістра 51, вихід якого з'єднаний з прямим входом АЛП 53. Інверсний вхід АЛП 53 з'єднаний з виходом комутатора 52, інформаційний і керуючий входи якого з'єднані з входом 17 логічного блока 10 і з виходом елемента І 56 відповідно. Інформаційний вихід 57 АЛП 53 з'єднаний з другим інформаційним входом мультиплексора 50, вихід 58 знака з'єднаний з першим входом елемента АБО 54, а вихід 59 ознаки нуля з'єднаний з другим входом елемента АБО 54. Вихід елемента АБО 54 з'єднаний з Sвходом RS-тригера 55, R-вхід якого з'єднаний з входом 7 скидання пристрою, його прямий вихід є виходом 15 результуючого сигналу пристрою, а його інверсний вихід і керуючий вхід 12 пристрою з'єднані з входами елемента І 56. Пристрій для моделювання нейрона (Фіг.1) працює таким чином. Перед початком роботи суматор 6 і логічний блок 10 встановлюють у початковий стан одиничним сигналом на вході 7 скидання пристрою. Після цього здійснюють настроювання пристрою на необхідний режим функціонування. Для настроювання пристрою на функціонування у режимі формального нейрона необхідно через установний вхід 4 пристрою на відповідні входи n блоків 31,...,3 n зміни синаптичних ваг подати нульовий сигнал, на керуючі входи 5 і 12 пристрою подати нульовий і одиничний сигнали відповідно, а на вхід 11 порогу - початкове значення порогу Q. Іншими словами, на керуючі входи 4, 5 і 12 подається код операції 001 (табл. 1). Після цього пристрій готовий до прийому двійкових кодів вхідних сигналів х 1,...,хn і значення синаптичних ваг gl,...,g n, які поступають відповідно на групи інформаційних входів 11,...,1n і 21,...,2n пристрою. Режим (операція) Формальний нейрон Скалярний добуток векторів Цифровий інтегратор У n блоках 31,...,3n зміни синаптичних ваг виконується формування зважених вхідних сигналів вигляду (1) ai = xi × gi , i = 1 n, , які з групи виходів 161,...,16n подаються на відповідні входи суматора 6 паралельно. В суматорі 6 відбувається формування часткових сум Sj (вихід 17) та їх підсумовування (вихід 18) у вигляді k Sk = å S j . j =1 (2) 6 З виходу 17 суматора 6 часткові суми Sj подаються на інформаційний вхід логічного блока 10, де вони порівнюються з порогом Q і формується значення поточного порогу на j-му етапі оброблення вигляду D j = D j- 1 - S j , j = 1 N , , (3) де D0=Q; N - кількість етапів оброблення. При цьому, якщо Dj>0, то на виході 15 результуючого сигналу Y пристрою буде незмінним нульовий сигнал (Y=0). Якщо Dj£0, то на виході 15 результуючого сигналу Y пристрою сформується одиничний сигнал (Y=1) і порогове оброблення припиняється. Одночасно в суматорі 6 продовжується формування і підсумовування часткових сум Sj, доки не отримаємо одиничний сигнал на виході ознаки нуля суматора 6, що спричинить появу на виході 13 сигналу „Кінець" пристрою одиничного сигналу. У цьому випадку на керуючий вхід комутатора 9 подається одиничний сигнал дозволу з виходу ознаки нуля суматора 6 і результат S підсумовування вигляду N S= å j=1 n Sj = åx ×g i i (4) i=1 з виходу 18 суматора 6 подається через комутатор 9 на інформаційний вихід 14 результату пристрою. Таким чином, при цьому режимі роботи на кожному j-му етапі пристрій реалізує функцію n æ ö (5) Y = signç Q - å xi × g i ÷, ç ÷ i =1 è ø що відповідає алгоритму формального нейрона і крім того суматором 6 виконується операція скалярного добутку векторів вигляду (4) Операцію (4) можна реалізувати окремо, якщо в якості компонент одного вектора взяти вхідні сигнали х1,...,хn, які поступають на групу інформаційних входів 11,...,1n пристрою, а в якості компонент другого вектора - значення синаптичних ваг g1 ,...,gn , які поступають на групу інформаційних входів 21,...,2n пристрою. При цьому на установний вхід 4 і керуючі входи 5 і 12 пристрою подаються Таблиця 1 нульові потенціали, тобто код даної операції 000 (табл. 1), а на вхід 11 порогу також подається Керуючі входи нульовий потенціал. У цьому випадку логічний 4 5 12 блок 10 не задіяний. В блоках 31,...,3n зміни 0 0 1 синаптичних ваг формуються добутки вигляду (1), 0 0 які з групи виходів 161,...,16n n блоків 31,...,30 зміни n 1 синаптичних ваг подаються на1 відповідні 0 входи суматора 6 паралельно. Після цього в суматорі 6 виконується формування і підсумовування часткових сум Sj цих добутків за формулою (2), поки не з'явиться одиничний сигнал дозволу на виході ознаки нуля суматора 6, а отже, на виході 13 сигналу „Кінець" пристрою. Тоді сформована остаточна сума S (4), яка є скалярним добутком компонент х1 і g1 вхідних векторів, подається через комутатор 9 на інформаційний вихід 14 результату пристрою. При налаштуванні на роботу у режимі цифрового інтегратора пристрій працює як суматор вхідних си гналів х1,...,хn, які подаються на 7 27751 груп у інформаційних входів 11,...,1n пристрою, у вигляді n S' = å xi . (6) i= 1 У цьому випадку на установний вхід 4 пристрою подається одиничний сигнал, який задає значення синаптичних ваг g 1,...,gn рівними одиниці, на керуючі входи 5 і 12 пристрою подаються одиничний і нульовий потенціали відповідно, тобто код даної операції 110 (табл. 1), а на вхід 11 порогу подається нульовий потенціал, при цьому логічний блок 10 відключається. В суматорі 6 формується за N етапів оброблення сума S' часткових сум S'j вигляду N ' S' = å Sj , j-1 (7) яка після появи одиничного сигналу на виході ознаки нуля суматора 6, а отже, на виході 13 сигналу „Кінець" пристрою, подається з виходу 18 суматора 6 через комутатор 9 на інформаційний вихід 14 результату пристрою. На початку роботи і-го блока 3i зміни синаптичних ваг (Фіг.2) здійснюють його настроювання на необхідний режим функціонування. При настроюванні пристрою на режим формального нейрона і скалярного добутку векторів на установний вхід 4 і керуючий вхід 5 пристрою подаються нульові потенціали (табл. 1). Це дозволяє проходження значення синаптичної ваги gi через мультиплексор 20, оскільки на його адресний вхід подається значення нуля, що означає дозвіл для проходження сигналу з входу 2i на вихід мультиплексора 20. Отже, блок 3і готовий до прийому двійкового коду вхідного сигналу хi і значення синаптичної ваги gi, які поступають відповідно на інформаційні входи 1i і 2i пристрою. Значення синаптичної ваги gi з виходу мультиплексора 20 надходить на вхід помножувального елемента 19, в якому воно перемножується зі значенням вхідного сигналу хi, тобто формується добуток зваженого вхідного сигналу а i вигляду (1), який знімається з виходу 16i блока 3i зміни синаптичних ваг. При настроюванні пристрою на режим цифрового інтегратора на установний вхід 4 і керуючий вхід 5 пристрою подаються одиничні потенціали (табл. 1). Блок 3i готовий до прийому двійкового коду вхідного сигналу xi, який подається на інформаційний вхід 1i пристрою. Одиничний сигнал з установного входу 4 пристрою подається на D-вхід D-тригера 21 і встановлює його в одиничний стан. Одиничний сигнал на керуючому вході 5 пристрою забороняє проходження значення синаптичної ваги gi через мультиплексор 20 і дозволяє проходження на його вихід одиничного сигналу з виходу D-тригера 21. Через мультиплексор 20 одиничний сигнал надходить на другий вхід помножувального елемента 19, в якому він перемножується зі значенням вхідного сигналу xi. Отриманий результат вигляду хi знімається з виходу 16i блока 3i зміни синаптичних ваг. 8 Суть робота суматора 6 (Фіг.3) полягає в тому, що порогове оброблення n чисел зводиться до обчислення і підсумовування N часткових сум, де N - кількість різноманітних вхідних величин а i, порівняння цих сум з порогом Q і формування підсумкового сигналу вигляду n N ì ï1, якщо S = ai = qjdj ³ Q, ï Y=í (8) i=1 j=1 ï ï0 у протилежно випадку, му î де Y - результуючий сигнал пристрою, qj загальна значуща частина доданків (мінімальний елемент) j-гo етапу, dj - кратність загальної частини q на j-му етапі, Q - значення порогу оброблення, j - етап оброблення. Процес підсумовування у суматорі 6 має такий вигляд. Спочатку визначається загальна значуща частина всіх доданків на j-му етапі, тобто å { }i=1 q j = min ai, j-1 n , j = 1 N , å , (9) де аi,0 - і-й доданок на вході суматора 6, і перевіряється умова qj=0. (10 ) Якщо умова (10) виконується, то процес підсумовування припиняється. У протилежному випадку виділяється різницевий зріз Аj, тобто сукупність величин різниці всіх доданків j-гo етапу з їхньою загальною частиною qj, тобто n n (11 A j = a i, j = ai, j-1 - q j i =1 i =1 . ) В подальшому отриманий різницевий зріз Aj є вхідною множиною доданків для наступного (j+1)гo етапу. Далі формується часткова сума Sj як кратне загальної частини qj, де кратність dj визначається кількістю додатних доданків j-гo етапу: Sj=qjdj. (12 ) Після цього відбувається підсумовування часткових сум Sj за формулою (2). Виконання умови (10) свідчить про закінчення підсумовування і про формування остаточного результату S підсумовування вигляду (4). Отже, суматор 6 (Фіг.3) працює таким чином. На вхід 16i і-ої комірки 22 надходить і-ий операнд аi,0 з групи операндів, кількість яких n. Запис операндів в комірки 22 виконується паралельно. Через мультиплексор 23 і-ий операнд аi,0 надходить в регістр 24 і-ої комірки 22, після чого виконується послідовне виділення загальної (мінімальної значущої) частини двох операндів - (і1)-го та і-го мініматором 28 і запис результату в регістр 29 і-ої комірки 22. Згідно з виразом (9) ця операція виконується послідовно, починаючи з другої комірки 22. Кінцевий результат q1 виділення загальної частини всіх n операндів на першому етапі формується в n-ій комірці 22 і з виходу 46 мініматора 28 цієї комірки 22 записується в регістри 30 всіх n комірок 22 паралельно по входу 45. Після цього в і-й комірці відбувається порівняння в АЛП 25 і-го операнда аi,0, що { } { } 9 27751 надходить з регістра 24, та загальної частини q1 всіх операндів, що надходить з регістра 30. Порівняння відбувається в процесі віднімання від величини операнда загальної частини всіх величин операндів згідно з виразом (11) і ця різниця записується з виходу 36 АЛП 25 через мультиплексор 23 в регістр 24. При цьому на виході 37 знака АЛП 25 формується знак різниці. При відсутності одиничного сигналу знака від'ємного результату одиничний сигнал з інверсного виходу D-тригера 27 подається на керуючий вхід комутатора 31 і дозволяє проходження в і-й комірці через комутатор 31 загальної частини q1 операндів з регістра 30 в суматор 26 (і-1)-ої комірки 22, де відбувається накопичування загальної частини операндів. У випадку, якщо на виході 37 знака АЛП 25 і-ої комірки 22 з'явиться одиничний сигнал знака від'ємного результату, то наявність нульового сигналу на інверсному виході D-тригера 27, а отже, на керуючому вході комутатора 31 заборонить надходження загальної частини q1 операндів на даному етапі оброблення через комутатор 31 на вхід суматора 26 (і-1)-ої комірки 22. В суматорі 26 кожної комірки 22 відбувається послідовне підсумовування загальних частин q1 групи з n операндів, а в результаті на виході 17 суматора 26 (n-1)-ої комірки 22 формується часткова сума S1 операндів згідно з виразом (12). Так виконується перший етап оброблення. В подальшому процес підсумовування виконується аналогічно першому етапу оброблення згідно з формулами (9)-(12). Процес підсумовування припиняється тоді, коли загальна значуща частина qj всіх поточних доданків на j-му етапі дорівнює нулю, тобто присутній одиничний сигнал на виході ознаки нуля мініматора 28 n-ої комірки 22, а отже на виході 13 n-ої комірки 22. Суть роботи логічного блока 10 (Фіг.4) полягає в тому, що після сформування часткової суми S1 за формулою (12) на першому етапі формується різниця між заданим порогом Q та частковою сумою S1, о триманою на цьому етапі, тобто (13 D1=Q-S1, ) перевіряється умова (14 D1£0 ) і в разі її виконання формується одиничний результуючий сигнал Y пристрою і порогове оброблення припиняється. В протилежному випадку процес порогового оброблення продовжується і в подальшому поточна різниця Dj-1 є поточним значенням порогу на наступному j-му етапі оброблення згідно з формулою (3). На j-му етапі перевіряється умова (15) Dj£0. Процес порогового оброблення повторюється до виконання умови (15) або до визначення нульової величини qj (10). Отже, логічний блок 10 (Фіг.4) працює таким чином. За одиничним сигналом на вході 7 скидання пристрою, який подається на R-вхід RS-тригера 10 55, він встановлюється у нульовий стан, тобто на його прямому виході, а отже, і на виході 15 результуючого сигналу Y пристрою встановлюється нульовий сигнал, а на інверсному виході - одиничний сигнал. Потім на вхід мультиплексора 50 надходить значення порогу Q з входу 11 порогу пристрою, яке при наявності одиничного сигналу на адресному вході 8 пристрою через мультиплексор 50 надходить у регістр 51. Перед початком роботи на керуючий вхід 12 подається одиничний сигнал, а на вхід 17 послідовно надходять часткові суми Sj вигляду (12). В результаті на першому етапі на інформаційному ви ході 57 АЛП 53 формується поточна різниця D1 згідно із виразом (13), яка через мультиплексор 50 при наявності нульового сигналу на адресному вході 8 пристрою знову записується у регістр 51, оскільки вона буде поточним значенням порогу на наступному етапі оброблення згідно із виразом (3). При цьому сигнали з виходів 58 знака і 59 ознаки нуля АЛП 53 надходять на входи елемента АБО 54. Це необхідно для перевірки умови (14). Вихід елемента АБО 54 формує результуючий сигнал Y, який буде одиничним в разі виконання умови (14) і нульовим в протилежному випадку, і який надходить на S-вхід RS-тригера 55. При наявності нульового сигналу на виході елемента АБО 54, а отже і на прямому ви ході RS-тригера 55, на інверсному виході RS-тригера 55 присутній одиничний сигнал, який надходить на другий вхід елемента І 56 і при наявності одиничного сигналу на керуючому вході 12 пристою надходить на керуючий вхід комутатора 52 і дозволяє проходження на його вихід часткової суми Sj з його інформаційного входу 17. При появі одиничного сигналу на виході елемента АБО 54, а потім на прямому виході RSтригера 55, на інверсному ви ході RS-тригера 55 з'являється нульовий сигнал, який надходить на другий вхід елемента І 56 і проходить на керуючий вхід комутатора 52, що забороняє проходження часткових сум Sj вигляду (12) з інформаційного входу 17. Отже, присутність одиничного сигналу хоча б на одному з виходів 58 знака чи 59 ознаки нуля АЛП 53, тобто наявність нульової чи від'ємної різниці D1 призведе до появи одиничного сигналу на виході 15 результуючого сигналу Y пристрою, в результаті чого порогове оброблення припиняється, оскільки не будуть надходити часткові суми Sj з інформаційного входу 17. Так виконується перший етап порогового оброблення. У випадку нульового сигналу на ви ході 15 результуючого сигналу Y пристрою виконуються процес наступного етапу оброблення. На всіх етапах, починаючи з другого, виконується операція (3) і перевіряється умова (15). У випадку, якщо умова (15) на всіх етапах не виконується, тобто на виході 15 результуючого сигналу Y пристрою присутній нульовий сигнал, процес порогового оброблення закінчується тоді, коли загальна частина qj всіх поточних доданків дорівнює нулю, тобто присутній одиничний сигнал на виході ознаки нуля суматора 6. При появі 11 27751 нульового сигналу на керуючому вході 12 порогове оброблення також припиняється. У табл. 2 наведено приклад реалізації роботи суматора 6 і логічного блока 10, в яких відбувається підсумовування і порогове оброблення п'яти чисел: 11, 3, 5, 8, 15. Знак (-) у таблиці означає від'ємний різницевий елемент, який не враховується у подальшому розгляді. Час підсумовування залежить від розмірності вхідної множини чисел. За рахунок виконання суматора у вигляді просторово-часового суматора, який працює за методом різницевих зрізів, задіяно всі n операндів, що значно збільшує паралелізм оброблення. Розглянемо часові співвідношення для всіх режимів функціонування пристрою: ì ï ïT = t + t × N = (n - 1)t com + (t sub + n × t sm ) × N, ï sm ac c ï Tmul = t mul + Tsm, í ï N ï j TQ = t mul + t ac + t com + Tsm , ï ï j =1 î å( ) (16 ) де Тsm, Т mul, Т Q - час виконання операцій у режимах цифрового інтегратора, скалярного добутку векторів і формального нейрона відповідно; tac - час розгону суматора; tc - час тіла цикла; N - кількість етапів оброблення; tcom - час виконання операції порівняння двох чисел; tsub час виконання віднімання двох чисел; ts m - час підсумовування двох чисел; tmul - час виконання x × g , i = 1, n операції множення двох чисел виду i i ; j Tsm = (t sub + n × t sm ) - час формування часткової суми Sj на j-му етапі. Отже, мінімальний і максимальний час виконання операції підсумовування можна визначити таким чином: min j Tsm = t ac + Tsm × Nmin , max j Tsm = t ac + Tsm × Nmax , де Nmax=n, N min=1. Відомо, що особливістю порогового оброблення векторного масиву чисел за методом різницевих зрізів є нефіксоване (нестале) значення часу оброблення. Це значення залежить 12 від кількості елементів на вході і кількості однакових елементів у масиві. Тому кількість етапів оброблення можна визначити за формулою: R N = n å (m - 1) (17) , де n - кількість елементів вхідного вектора; R кількість груп з кількістю mr однакових чисел; m r, R - випадкові величини. Отже, принцип роботи пристрою для моделювання нейрона наближається до роботи біологічного нейрона, час спрацювання якого залежить від кількості вхідних елементів і закону їх розподілу. r =1 r 13 27751 14

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for simulating a neuron

Автори англійськоюKozhemyako Volodymyr Prokopovych, Martyniuk Tetiana Borysivna, Kozhemiako Andrii Viktorovych, Moroz Iryna Vitaliivna

Назва патенту російськоюУстройство для моделирования нейрона

Автори російськоюКожемяко Владимир Прокофьевич, Мартынюк Татьяна Борисовна, Кожемьяко Андрей Викторович, Мороз Ирина Витальевна

МПК / Мітки

МПК: G06G 7/60

Мітки: пристрій, моделювання, нейрона

Код посилання

<a href="https://ua.patents.su/7-27751-pristrijj-dlya-modelyuvannya-nejjrona.html" target="_blank" rel="follow" title="База патентів України">Пристрій для моделювання нейрона</a>

Попередній патент: Буферний каскад

Наступний патент: Центрифуга з імпульсним вивантаженням осаду

Випадковий патент: Колінчатий вал