Декодер згорткового коду

Номер патенту: 25556

Опубліковано: 30.10.1998

Автори: Дунець Богдан Романович, Мельник Анатолій Олексійович

Формула / Реферат

Декодер згорткового коду, що містить перший віднімач, блок тактування, перший, другий, третій виходи якого з'єднані відповідно з першим входом блока обчислення метрик гілок, першим входом блока обчислення метрик, першим входом регістра, який відрізняється тим, що в нього введені перший, другий і третій комутатори, блок прийняття рішення, другий віднімай, регістр корекції, кодер, блок порівняння, перший, другий, третій, четвертий регістри зсуву, перший вхід першого регістра зсуву об'єднано з першим входом другого комутатора і є першим входом пристрою, перший вхід другого регістра зсуву об'єднано з першим входом третього комутатора і є другим входом пристрою, другі входи першого і другого регістрів зсуву об'єднані і під'єднані до четвертого виходу блока тактування, вихід першого регістра зсуву під'єднано до другого входу другого комутатора, вихід другого регістра зсуву під'єднаний до другого входу третього комутатора, треті входи другого і третього комутаторів об'єднані і під'єднані до п'ятого виходу блока тактування, вихід другого комутатора під'єднаний до другого входу блока обчислення метрик гілок, під'єднаний до другого входу блока обчислення метрик, під'єднаний до першого входу третього регістра зсуву, вихід третього комутатора під'єднаний до третього входу блока обчислення метрик гілок, під'єднаний до третього входу блока обчислення метрик, під'єднаний до першого входу четвертого регістра зсуву, другі входи третього і четвертого регістрів зсуву об'єднані і підключені до шостого виходу блока тактування, вихід третього регістра під'єднаний до першого входу блока порівняння, вихід четвертого регістра зсуву під'єднаний з другим входом блока порівняння, третій і четвертий входи блока порівняння під'єднані відповідно до першого і другого виходів кодера, перший вхід кодера під'єднаний до сьомого виходу блока тактування, другий вхід кодера під'єднано до першого входу блока тактування і вихода блока прийняття рішення і є виходом пристрою, третій і четвертий входи пристрою є відповідно другим і третім входами блока тактування, вихід блока порівняння під'єднаний до першого входу регістра корекції, вихід регістра корекції під'єднаний до перших входів першого і другого віднімачів і під'єднаний до першого входу блока прийняття рішення, другий вхід регістра корекції під'єднаний до восьмого виходу блока тактування, дев'ятий вихід блока тактування під'єднаний до другого входу блока прийняття рішення, десятий вихід блока тактування під'єднаний до першого входу першого комутатора, 1 - V - тий виходи, причому V = 2P, де P - число перших оброблюваних гілок вхідної послідовності, і P ³ (2K - 1), де K - довжина кодового обмеження згорткового коду, блока обчислення метрик гілок під'єднані до відповідних 2 - 2 + V входів першого комутатора, виходи 1 - V першого комутатора під'єднані до відповідних 4 - 4 + V входів блока обчислення метрик, виходи 1 - 2V якого під'єднані до відповідних 2 - 2 + 2V входів регістра, виходи 1 - 2V регістра під'єднані до відповідних 3 - 3 + 2V входів блока прийняття рішення, виходи 1 - V регістра також під'єднані до відповідних 2 - 2 + V входів першого віднімача, виходи V + 1 - 2V регістра також під'єднані до відповідних 2 - 2V входів другого віднімача, виходи 1 - V першого віднімача під'єднані до відповідних 3 + V - 3 + 2V входів першого комутатора, виходи 1 - V другого віднімача під'єднані до відповідних 4 + 2V - 4 + 3V входів першого комутатора.

Текст

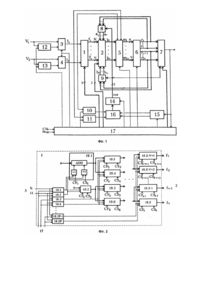

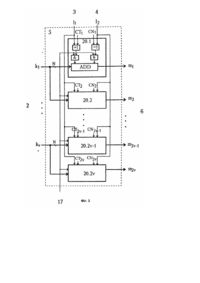

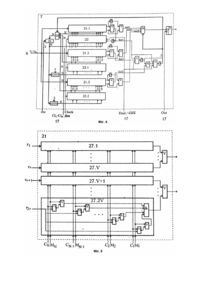

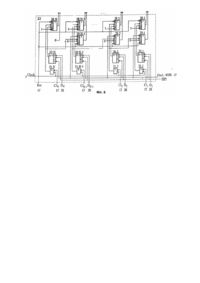

Винахід належить до систем передачі інформації по каналах зв'язку і може бути використаний в цифрових системах передачі згортковим кодом при декодуванні по алгоритму Вітербі. З відомих пристроїв аналогом до винаходу є пристрій для декодування згорткового коду (Авт. св. СРСР №1725400, кл. H03M13/12, опубл. 07.04.92, Бюл. №13), який містить комутатор, вихід якого з'єднаний з першими входами першого - n - го блоків додавання-порівняння-вибору (n = 2V, де V - довжина кодового обмеження згорткового коду), перші виходи яких під'єднані до входів першого - n - го буферних регістрів у відповідності з решітчатою діаграмою згорткового коду, виходи (2i - 1) - i (2i) - го буферних регістрів (i = 1, ..., n/2) з'єднані відповідно з другими і третіми входами (2i - 1) - i (2i) - го блоків додавання-порівняння-вибору, другі виходи першого - n - го блоків додавання-порівняння-вибору під'єднані до відповідних блоків пам'яті рішень, (n + 1) - 1 (n + 2) - й буферні регістри, блок індикації, блок управління і мультиплексор, інформаційні виходи якого під'єднані до виходів першого n - го буферних регістрів, перший інформаційний і керуючий входи комутатора є відповідно інформаційним входом і входом вибору режиму пристрою, вихід блока пам'яті рішень під'єднаний до інформаційного входу (n + 2) - го буферного регістра і є виходом пристрою, виходи мультиплексора об'єднані з відповідними виходами (n + 2) - го буферного регістра і під'єднані до інформаційних входів блока індикації і (n + 1) - го буферного регістра і до двохнаправленої шини даних блока управління, перший і другий виходи якого є відповідно входами пуску і управління пристрою, вихід (n + 1) - го буферного регістра з'єднаний з другим інформаційним входом комутатора, адресні входи блока управління під'єднані до адресних входів мультиплексора, перший - четвертий керуючі виходи блока управління з'єднані з керуючими входами відповідно блока індикації, (n + 1) - го буферного регістра, мультиплексора i (n + 2) - го буферного регістра. Даний пристрій для декодування згорткового коду характеризується низькою швидкодією, обумовленою структурою його побудови, яка відображає декодування згорткового коду з використанням кодової решітки представлення коду. Найбільш близьким аналогом до винаходу є декодер згорткового коду (Авт. св. СРСР №1660178, кл. H03M13/12, опубл. 30.06.91, Бюл. №24), який містить перший віднімач, блок тактування, перший, другий, третій виходи якого з'єднані відповідно з першим входом блока обчислення метрик гілок, першим входом блока обчислення метрик, першим входом регістра. Даний декодер згорткового коду характеризується низькою швидкодією, обумовленою структурою його побудови, яка має низьку степінь паралелізму обчислень при декодуванні. В основу винаходу поставлено задачу створити декодер згорткового коду, в якому введення нових блоків і удосконалення існуючих дозволило б спростити алгоритм роботи, і тим самим забезпечити зростання швидкодії пристрою. Поставлена задача вирішується тим, що в декодер згорткового коду, який містить перший віднімач, блок тактування, перший, другий, третій виходи якого з'єднані відповідно з першим входом блока обчислення метрик гілок, першим входом блока обчислення метрик, першим входом регістра, згідно з винаходом, додатково введені перший, другий і третій комутатори, блок прийняття рішення, другий віднімач, регістр корекції, кодер, блок порівняння, перший, другий, третій, четвертий регістри зсуву, перший вхід першого регістра зсуву об'єднано з першим входом другого комутатора і є першим входом пристрою, перший вхід другого регістра зсуву об'єднано з першим входом третього комутатора і є другим входом пристрою, другі входи першого і другого регістрів зсуву об'єднані і під'єднані до четвертого виходу блока тактування, вихід першого регістра зсуву під'єднано до другого входу другого комутатора, вихід другого регістра зсуву під'єднаний до другого входу третього комутатора, треті входи другого і третього комутаторів об'єднані і під'єднані до п'ятого виходу блока тактування, вихід другого комутатора під'єднаний до другого входу блока обчислення, метрик гілок, під'єднаний до другого входу блока обчислення метрик, під'єднаний до першого входу третього регістра зсуву, вихід третього комутатора під'єднаний до третього входу блока обчислення метрик гілок, під'єднаний до третього входу блока обчислення метрик, під'єднаний до першого входу четвертого регістразсуву, другі входи третього і четвертого регістрів зсуву об'єднані і підключені до шостого виходу блока тактування, вихід третього регістра під'єднаний до першого входу блока порівняння, вихід четвертого регістра зсуву під'єднаний з другим входом блока порівняння, третій і четвертий входи блока порівняння під'єднані відповідно до першого і другою виходів кодера, перший вхід кодера під'єднаний до сьомого виходу блока тактування, другий вхід кодера під'єднано до першого входу блока тактування і виходу блока прийняття рішення і є виходом пристрою, третій і четвертий входи пристрою є відповідно другим і третім входами блока тактування, вихід блока порівняння під'єднаний до першого входу регістра корекції, вихід регістра корекції під'єднаний до перших входів першого і другого віднімачів і під'єднаний до першого входу блока прийняття рішення, другий вхід регістра корекції під'єднаний до восьмого виходу блока тактування, дев'ятий вихід блока тактування під'єднаний до другого входу блока прийняття рішення, десятий вихід блока тактування під'єднаний до першого входу першого комутатора, 1 - V - тий виходи, причому V = 2P, де P - число перших оброблюваних гілок вхідної послідовності, і P ³ (2K - 1), де K - довжина кодового обмеження згорткового коду, блока обчислення метрик гілок під'єднані до відповідних 2 - 2 + V входів першого комутатора, виходи 1 - V першого комутатора під'єднані до відповідних 4 - 4 + V входів блока обчислення метрик, виходи 1 - 2V якого під'єднані до відповідних 2 - 2 + 2V входів регістра, виходи 1 - 2V регістра під'єднані до відповідних 3 - 3 + 2V входів блока прийняття рішення, виходи 1 - V регістра також під'єднані до відповідних 2 - 2 + V входів першого віднімача, виходи V + 1 - 2V регістра також під'єднані до відповідних 2 - 2V входів другого віднімача, виходи 1 - V першого віднімача під'єднані до відповідних 3 + V - 3 + 2V входів першого комутатора, виходи 1 - V другого віднімача під'єднані до відповідних 4 + 2V - 4 + 3V входів першого комутатора. В основу декодера покладено модифікований алгоритм декодування згорткових кодів зі зворотнім зв'язком. В даному алгоритмі, для підвищення швидкодії за рахунок паралелізму, використовується представлення згорткового коду бінарним деревом, а не кодовою решіткою, яка використовується в інших декодерах. Такий підхід дозволяє проводити пошук найкращого шляху при декодуванні кодової послідовності, паралельно і одночасно аналізуючи всі можливі шляхи, що суттєво підвищує швидкодію декодера. На фіг.1 представлена структурна схема декодера згорткового коду; на фіг.2 - структурна схема блока обчислена метрик гілок; на фіг.3 - структурна схема блока обчислення метрик; на фіг.4 - структурна схема блока прийняття рішення; на фіг.5 - функціональна схема блока асоціативного пошуку; на фіг.6 - функціональна схема блока формування маски і компаранда. Декодер складається з блока обчислення метрик гілок 1, першого комутатора 2, другого комутатора 3, третього комутатора 4, блока 5 обчислення метрик, регістра 6, блока 7 прийняття рішення, першого віднімача 8, другого віднімача 9, першого регістра зсуву 10, другого регістра зсуву 11, третього регістра зсуву 12, четвертого регістра зсуву 13, регістра корекції 14, кодера 15, блока 16 порівняння, блока 17 тактування. Виходи f 1 - f v блока обчислення метрик гілок 1, причому V = 2P, де P - число перших оброблюваних гілок вхідної послідовності, і P ³ (2 * K - 1), де K - довжина кодового обмеження згорткового кода, з'єднані з входами f 1 - f v першого комутатора 2. Виходи k1 - kv першого комутатора 2 з'єднані з входами k1 - kv блока 5 обчислення метрик. Виходи m1 m2v блока 5 обчислення метрик з'єднані з інформаційними входами m1 - m2v регістра 6. Інформаційні виходи r1 - r v регістра 6 з'єднані з входами r1 - rv блока 7 прийняття рішення. Інформаційні виходи r1 - rv регістра 6 з'єднані з входами r1 - r v першого віднімача 8. Інформаційні виходи rv+1 - r2v регістра 6 з'єднані з входами r v+1 - r2v другого віднімача 9. Виходи a1 - av першого віднімача 8 з'єднані з входами a1 - av першого комутатора 2. Виходи b1 - b v другого віднімача 9 з'єднані з входами b1 - b v першого комутатора 2. Блок обчислення метрик гілок 1, перший комутатор 2, блок обчислення метрик 5, регістр 6, блок прийняття рішення 7, перший віднімай 8, другий віднімач 9 оперують N-розрядними числами (N = ]log2(2 * (P + 2)[). Однорозрядний вихід блока прийняття рішення 7 являється виходом пристрою в цілому і інформаційним входом кодера згорткового коду 15 і входом блока 17 тактування. Перший вихід кодера 15 з'єднаний з першим входом блока 16 порівняння, другий вихід кодера 15 з'єднаний з другим входом блока 16 порівняння. Вхід пристрою V1 є інформаційним входом N + 1 тактового третього регістра зсуву 12 і першим інформаційним входом однорозрядного другого комутатора 3, вхід пристрою V2 є інформаційним входом N + 1 тактового четвертого регістрасуву 13 і першим інформаційним входом однорозрядного третього комутатора 4. Законодавча інформація в каналі передачі між передавачем і приймачем, в склад якого входить даний пристрій, може передаватися як в поралельній формі (V1, V2), так і послідовній формі, тоді приймач додатково перетворює послідовне поступлення символів V1 і V2 в паралельне. Інформаційний вихід третього регістра зсуву 12 з'єднаний з другим інформаційним входом другого однорозрядного комутатора 3. Інформаційний вихід четвертого регістра зсуву 13 з'єднаний з другим інформаційним входом третього однорозрядного комутатора 4. Інформаційний вихід I 1 другого однорозрядного комутатора 3 з'єднаний з входом її блока 5 обчислення метрик, з'єднаний з входом I 1 блока 1 обчислення метрик гілок, з'єднаний з інформаційним входом P + 2 тактового першого регістра зсуву 10. Інформаційний вихід I 2 третього однорозрядного комутатора 4 з'єднаний з входом I 2 блока 5 обчислення метрик, з'єднаний з входом I 2 блока 1 обчислення метрик гілок, з'єднаний з інформаційним входом P + 2 тактового другого регістра зсуву 11. Вихід першого регістра зсуву 10 з'єднаний з третім входом блока 16 порівняння. Вихід другого регістра зсуву 11 з'єднаний з четвертим входом блока 16 порівняння. Дворозрядний вихід блока 16 порівняння з'єднаний з входом регістра корекції 14. Вихід cor регістра корекції 14 з'єднаний з входом cor першого віднімача 8, з'єднаний з входом cor другого віднімача 9, з'єднаний з входом cor блока 7 прийняття рішення. Блок тактування 17 з'єднаний лініями керування з блоком обчислення метрик гілок 1, першим комутатором 2, другим комутатором 3, третім комутатором 4, блоком обчислення метрик 5, регістром 6, блоком прийняття рішення 7, першим регістром зсуву 10, другим регістром зсуву 11, третім регістром зсуву 12, четвертим регістром зсуву 13, регістром корекції 14, кодером 15. Блок 1 обчислення метрик гілок (фіг.2) містить регістри 18.1 - 18.2P, блоки 19.1 - 19.22 накопичення метрик, де Z визначається за формулою Перші входи регістрів 18.1, 18.3, ..., 18.2P - 1 об'єднані і є входом I 1 блока 1 обчислення метрик гілок. Перші входи регістрів 18.2. 18,4, ..., 18.2P об'єднані і є входом I 2 блока 1 обчислення метрик гілок. Другі входи регістрів 18.1, 18.2 об'єднані і є першим керуючим входом блока 1 обчислення метрик гілок, другі входи регістрів 18.3, 18.4 об'єднані і є другим керуючим входом блока 1 обчислення метрик гілок, і так далі, другі входи регістрів 18.2P - 1, 18.2P об'єднані і є P - им керуючим входом блока 1 обчислення метрик гілок. Вихід регістра 18.1 є першим входом блоків 19.1 і 19.2, вихід регістра 18.2 є другим входом блоків 19,1 і 19.2. Вихід регістра 18.3 є першим входом блоків 19.3 - 19.6, вихід регістра 18.4 є другим входом блоків 19.3 - 19.6, і так далі, вихід регістра 18.2P - 1 є першим входом блоків 19.Z - V + 1 - 19.Z, вихід регістра 18.2P є другим входом блоків 19.Z - V + 1 - 19.Z. На третій вхід блоків 19.1 і 19.2 поступає 0. Блоки накопичення метрик 19.1 - 19.Z об'єднуються за правилом бінарного дерева: вихід блока 19.1 є третім входом блока 19.3 і 19.4, вихід блока 19.2 є третім входом блоків 19.5 і 19.6, і так далі, вихід блока 19.Z - V є третім входом блоків 19.Z - 1 і 19.Z. Четвертий вхід блока 19.1 призначений для поступлення константи CF1, п'ятий вхід блока 19.1 призначений для поступлення константи CS1, і так далі, четвертий вхід блока 19.Z призначений для поступлення константи CFz, п'ятий вхід блока 19.Z призначений для поступлення константи CSz. Вихід блока 19.Z - V + 1 є виходом f 1 блока 1 обчислення метрик гілок, вихід блока 19.Z - V + 2 є виходом f2 блока 1 обчислення метрик гілок, і так далі, вихід блока 19.Z є виходом f v блока 1 обчислення метрик. Блок накопичення метрик 19.1 - 19.Z містить в собі два суматори по модулю два і N розрядний суматор, перший вхід якого є входом блока, вихід суматора є виходом блока накопичення метрик 19.1 - 19.Z. Блок 5 обчислення метрик (фіг.3) містить блоки 20.1 - 20.2V накопичення метрик. Перші входи блоків 20.1 - 20.2v об'єднані і є входом I 1 блока 5 обчислення метрик, другі входи блоків 20.1 - 20.2v об'єднані і є входом I 2 блока 5 обчислений метрик. Треті входи блоків 20.1 і 20.2 об'єднані і є входом k1 блока 5 обчислення метрик, треті входи блоків 20.3 і 20.4 об'єднані і є входом k2 блока 5 обчислення метрик, і так далі, треті входи блоків 20.2v - 1 і 20.2v об'єднані і є входом kv блока 5 обчислення метрик. Четвертий вхід блока 20.1 призначений для поступлення константи CT1, п'ятий вхід блока 20.1 - для поступлення константи CN1, четвертий вхід блока 20.2 - для поступлення константи CT2, п'ятий вхід блока 20.2 - для поступлення константи CN2, і так далі, четвертий вхід блока 20.2v - для поступлення константи CT2v, п 'ятий вхід блока 20.2v - для поступлення константи CN2v. Шостий вхід блоків 20.1 - 20.2v призначений для поступлення керуючого сигналу режимом роботи, який є керуючим сигналом блока 5 обчислення метрик. Перший вихід блока 20.1 є виходом m1 блока 5 обчислення метрик, перший вихід блока 20.2 є виходом m2 блока 5 обчислення метрик, і так далі, перший вихід блока 20.2v є виходом m2v блока 5 обчислення метрик. Блок накопичення метрик 20.1 - 20.2v складається з двох суматорів по модулю два, двох кон'юнкторів, перші входи яких об'єднані і є шостим входом блока накопичення метрик, N-розрядного суматора, перший вхід якого є третім входом блока накопичення метрик, вихід суматора є виходом блока накопичення метрик. Блок прийняття рішений 7 (фіг.4) складається з 21.1 - 21.3 блоків асоціативного пошуку, блока 22 формування маски і компаранда, регістрів 23.1, 23.2, комутаторів 24, 25, двох суматорів ADD1 і ADD2, віднімача 26, шести двовходових диз'юнкторів, двох трьохвходових диз'юнкторів, двовходового кон'юнктора, шести інверторів, вихідного тригера. Входи r1 - r2v блока 7 прийняття рішення є N-розрядними входами r1 - r2v блоків 21.1 - 21.3 асоціативного пошуку. Перший вихід блока 21.1 асоціативного пошуку є першим входом першого двовходового диз'юнктора, другий вихід блока 21.1 асоціативного пошуку є другим входом першого двовходового диз'юнктора, даний диз'юнктор призначений для формування сигнала hit1. Перший вихід блока 21.1 асоціативного пошуку через інвертор під'єднаний до першого входу другого двовходового диз'юнктора, другий вихід блока 21.1 асоціативного пошуку є другим входом другого двовходового диз'юнктора, даний диз'юнктор призначений для формування сигнала rez1. Перший вихід блока 21.2 асоціативного пошуку є першим входом третього двовходового диз'юнктора, другий вихід блока 21.2 асоціативного пошуку є другим входом третього двовходового диз'юнктора, даний диз'юнктор призначений для формування сигналу hit2. Перший вихід блока 21.2 асоціативного пошуку через інвертор під'єднаний до першого входу четвертого двовходового диз'юнктора, другий вихід блока 21.2 асоціативного пошуку є другим входом четвертого двовходового диз'юнктора, даний диз'юнктор призначений для формування сигналу rez2. Перший вихід блока 21.3 асоціативного пошуку є першим входом п'ятого двовходового диз'юнктора, другий вихід блока 21.3 асоціативного пошуку є другим входом п'ятого двовходового диз'юнктора, даний диз'юнктор призначений для формування сигналу hit3. Перший вихід блока 21.3 асоціативного пошуку через інвертор під'єднаний до першого входу шостого двовходового диз'юнктора, другий вихід блока 21.3 асоціативного пошуку є другим входом шостого двовходового диз'юнктора, даний диз'юнктор призначений для формування-сигналу rez3. Сигнали hit1, hit2, подаються на вхід першого трьохвходового диз'юнктора, вихід даного диз'юнктора є входом інвертора, інвертор призначений для формування молодшого розряду керуючого слова управлінням комутатора. Вихід даного інвертора є першим входом кон'юнктора, на другий вхід кон'юнктора поступає сигнал hit3. Вихід кон'юнктора є першим входом другого трьохвходового диз'юнктора, на другий і третій вхід другого трьохвходового диз'юнктора поступають, відповідно сигнали hit1 і . Вихід другого трьохвходового диз'юнктора є входом інвертора, інвертор призначений для формування старшого розряду керуючого слова управлінням комутатором. Керуюче слово управлінням комутатором призначене для поступлення наоднорозрядний комутатор 24, 25. Перший інформаційний вхід комутатора 24 призначений для поступлення сигналу rez1, другий - rez2, третій - rez3. Комутатор 24 призначений для комутування на свій вихід сигналу з першого інформаційного входу, якщо керуюче слово дорівнює 0, сигналу з другого інформаційного входу, якщо керуюче слово дорівнює 1, сигналу з третього інформаційного входу, якщо керуюче слово дорівнює 2. Вихід комутатора 24 є інформаційним входом однорозрядного регістра, запис в який виконується керуючим сигналом Out блока 7 прийняття рішення. Вихід однорозрядного регістра є виходом блока 7 прийняття рішення в цілому. Керуюче слово управлінням комутатором поступає також на N-розрядний комутатор 25, на перший інформаційний вхід якого поступає інформація з блока 22 формування маски і компаранда, на другий - інформація з регістра 23.1, на третій - інформація з регістра 23.2. Комутатор 25 призначений для комутування на свій N-розрядний вихід N-розрядний сигнал з першого інформаційного входу, якщо керуюче слово дорівнює 0, з другого - якщо керуюче слово дорівнює 1, з третього якщо керуюче слово дорівнює 2. Вихід комутатора 25 є першим входом віднімача 26, на другий вхід віднімана поступає двохрозрядне слово cor. Віднімач 26 призначений для віднімання від інформації на першому вході інформацію на другому вході. Вихід віднімача 26 є інформаційним входом блока 22 формування маски і компаранда, вихід віднімача 26 є першим входом суматора ADD1 і першим входом суматора ADD2. На другий вхід суматора ADD1 поступає число 1, на другий вхід суматора ADD2 поступає число 2. Вихід суматора ADD1 є інформаційним входом регістра 23.1, вихід суматора ADD2 є інформаційним входом регістра 23.2. Запис N-розрядної інформації з віднімача в блок 22 формування маски і компаранда, інформації з суматора ADD1 в регістр 23.1, інформації з суматора ADD2 в регістр 23.2 виконується керуючим сигналом Clock блока 7 прийняття рішення. Крім того в блок 22 формування маски і компаранда поступають керуючі сигнали CI 1 - CI N, Res, та інверсія інформаційного сигнала hit1. Ключовими елементами блока 7 прийняття рішення є блоки 21.1 - 21.3 асоціативного пошуку. Блок асоціативного пошуку 21.1 - 21.3 (фіг.5) складається з асоціативних комірок 27.1 - 27.2v. На вхід кожної комірки поступає N розрядів компарандів C1 - CN, N розрядів маски M1 - MN. Вхідний сигнал r1 є входом блока 27.1, вхідний сигнал r2 є входом блока 27.2, і так далі, вхідний сигнал r2v є входом блока 27.2v. Вихід асоціативної комірки 27.1 є першим входом першого диз'юнктора, і так далі вихід асоціативної комірки 27.v є v - им входом першого диз'юнктора. Вихід першого диз'юнктора є виходом блока асоціативного пошуку в цілому. Вихід асоціативної комірки 27.v 4 + 1 є першим входом другого диз'юнктора, і так далі, вихід асоціативної комірки 27.2v є v - тим входом другого диз'юнктора. Вихід другого диз'юнктора є виходом блока асоціативного пошуку в цілому. Блок 22 формування маски і компаранда (фіг.6) містить тригери 28.1 - 28.N компаранда, тригери 29.1 - 29.N - 1 маски, мультиплексори 30.1 - 30.N, диз'юнктори 31.1 - 31.N. Вхідний сигнал Clock є першим входом диз'юнкторів 31.1 - 31.N. Вхідний сигнал порозрядного тактування CI 1 є другим входом диз'юнктора 31.1, і так далі, вхідний сигнал поразрядного тактування CIN є другим входом диз'юнктора 31.N. Вхідний сигнал під'єднаний до керуючого розряду мультиплексорів 30.1 - 30.N, під'єднаний до входу R тригерів 29.1 - 29.N - 1. Вхідний сигнал Res під'єднаний до входу R тригерів 28.1 - 28.N і входи S тригерів 29.1 - 29.N - 1. Перший інформаційний вхід мультиплексора 30.1 призначений для поступлення вхідного сигналу D1, і так далі, перший інформаційний вхід мультиплексора 30.N призначений для поступлення вхідного сигналу DN. Другі інформаційні входи мультиплексорів 30.1 - 30.N призначені для поступлення вхідного сигналу hit1. Пристрій декодування згорткового коду працює наступним чином. На вхід пристрою V1, V2 синхронно з тактовим сигналом поступає вхідна інформація, початок поступлення послідовності індикується сигналом Beg. Перші P пар (V1, V2) вхідної послідовності через другий комутатор 3 і через третій комутатор 4 поступають в блок 1 обчислення метрик гілок, блок тактування 17 формує сигнали управління для запису вхідної інформації у внутрішні регістри блока 1 обчислення метрик гілок. Вхідна інформація також постійно записується в перший регістр зсуву 10 і другий регістр зсуву 11. Після прийому P-пар вхідної інформації блок тактування 17 сигналом управління встановлює перший комутатор 2 в режим комутування, при якому на вихід передаються сигнали з входів f 1 - fv. Після прийому P + 1 інформаційної пари, блок 5 обчислень метрик проводить обчислення метрик для одного ярусу на основі обчислених метрик з блока 1 обчислення метрик гілок, працює в режимі накопичення. Обчислена інформація заноситься в регістр 6, одночасно інформація з блока 16 порівняння = 1 блок тактування 17 ініціалізує режим пошуку заноситься в регістр корекції 14. Після цього сигналом мінімального числа в блоці 7 прийняття рішення. Оскільки пошук мінімального числа виконується не за один такт, а за N + 1, то вхідна інформація, яка поступала цей час у пристрій, записується в третій регістр зсуву 12 і четвертий регістр зсуву 13, і другий комутатор 3 та третій комутатор 4 передають на свої виходи інформацію з регістрів зсуву. Після завершення пошуку сигнал фіксується в лог. 0, на вихід пристрою з блока 7 поступає перший декодований біт. Декодований біт поступає на кодер 15, інформація з кодера за допомогою блока порівняння порівнюється з інформацією з першого регістра зсуву 10 і другого регістра зсуву 11. Перший 8 та другий 9 віднімачі віднімають від кожного вхідного числа з блока 6 число cor, блок 17 тактування на основі декодованої інформації керує першим комутатором 2 наступним чином: якщо декодований біт рівний 0, то перший комутатор 2 на вихід комутує інформацію з входів a1 - av, а якщо ж декодований біт рівний 1, то перший комутатор 2 на вихід комутує інформацію з входів b1 - bv. Цикли декодування продовжується. Після закінчення вхідної послідовності, про що індикує сигнал Beg, пристрій 5 обчислення метрик керуючим сигналом з блока 17 тактування переводиться в режим пропускання і пристрій повторює P циклів декодування. Робота блока 1 обчислення метрик гілок полягає в наступному. Блок 1 обчислення метрик гілок приймає вхідні сигнали I 1 і I 2, які записуються в регістри 18.2 - 18.2P керуючими сигналами. Перша прийнята пара вхідних сигналів I 1 і I 2 записується в регістри 18.1 і 18.2, друга пара вхідних сигналів I 1 і I 2 записується в регістри 18.3 і 18.4 і так далі, P - та пара вхідних сигналів записується в регістри 18.2P 1, 18.2P. Інформація, що поступає на перший вхід блока накопичення метрик 19.1 - 19.Z порівнюється з константою на четвертому вході блока 19.1 - 19.Z за допомогою суматора по модулю два, - формується однорозрядна метрика, яка поступає на другий вхід суматора; інформація на другому вході блока накопичення метрик 19.1 - 19.Z порівнюється з константою на п'ятому вході блоку за допомогою суматора по модулю два, - формується однорозрядна метрика, яка поступає на третій вхід суматора. Суматор виконує додавання інформації першого, другого і третього входів. Константи CF1 -CFz і CS1 - CSz - це двійкові однобітні числа, значення яких визначаються кодовим деревом представлення конкретного згорткового коду. Так константи CF1, CS1, CF2, CS2 визначаються першим ярусом кодового дерева, константи CF3 - CF6, CS3 - CS6 визначаються другим ярусом кодового дерева, і так далі, константи CFz-v+1 - CFz, CSz-v+1 - CSZ визначаються P-им ярусом кодового дерева. Блок 1 обчислення метрик гілок на основі прийнятих P пар вхідних сигналів за допомогою блоків накопичення метрик 19.1 - 19.Z виконує обчислення метрик f 1 - f v. Робота блока 5 обчислення метрик полягає в наступному. Блок 5 обчислення метрик на кожному такті виробляє і подає на свої виходи нові значення метрик стану для відповідного яруса кодового дерева. Якщо керуючий сигнал режимом роботи блока 5 обчислення метрик дорівнює лог "1" (режим накопичення), то блок 5 обчислення метрик за допомогою блоків накопичення метрик 20.1 - 20.2v виконує збільшення вхідних метрик на величину однорозрядних метрик, які формуються шляхом порівняння вхідних сигналів з відповідними константами: Інформація, що поступає на перший вхід блока накопичення метрик 20.1 20.2v порівнюється з константою на четвертому вході блока за допомогою суматора по модулю два, - формується однорозрядна метрика, яка через кон'юнктор поступає на другий вхід суматора; інформація на другому вході блока накопичення метрик 20.1 - 20.2v порівнюється з константою на п'ятому вході блока за допомогою суматора по модулю два, - формується однорозрядна метрика, яка через кон'юнктор поступає на третій вхід суматора. Суматор виконує додавання інформації першого, другого і третього своїх входів. Константи CT1 - CT2v і CN1 - CN2v - це двійкові однобітні числа, значення яких визначаються P + 1 - им ярусом кодового дерева предсталення конкретного згорткового коду. Якщо керуючий сигнал режимом роботи блока 5 обчислення метрик дорівнює лог "0" (режим пропускання), то блок 5 обчислення метрик не виконує збільшення вхідних метрик. Робота блока 7 прийняття рішення в цілому полягає в наступному. При першому поступленні на вхід Nрозрядних чисел r1 - r2v, блок 7 прийняття рішення повинен знайти серед них мінімальне, для цього блок 7 прийняття рішення сигналом (лог. 1) переводиться в режим пошуку. Сигналом Res (лог. 0) відбувається встановлення в початкове положення регістрів 28.1 - 28.N, 29.1 - 29.N - 1 блока 22: маска (M) дорівнює 01 ... 11, компаранд (C) дорівнює 00 ... 00. Блок асоціативного пошуку 21.1 виконує асоціативний пошук серед чисел r1 - r2v таких, в яких старший розряд (N - ий) рівний 0. Якщо таке число існує, то сигнал hit1 дорівнює лог. 1, якщо не існує, то hit1 дорівнює відповідно лог. 0. Інверсія сигналу hit1 керуючим сигналом записується в старший (N - ий) розряд компаранда (регістр 28.N), цим же сигналом відбувається встановлення N - 1 розряда маски (регістр 29.N - 1) в 1. Допустимо, що hit = 0, тоді маска і компаранд будуть рівні: M = 001 … 11, C = 100 ... 00. Процедура пошуку продовжується доти, поки не дійдемо до молодшого розряду, - тобто знайдемо шукане мінімальне число. Керуючий сигнал (лог. 1) фіксує керуюче слово управлінням комутатором в 0, - відповідно на вихід комутатора 24 поступає сигнал rez1, який запам'ятовується у вихідному тригері сигналом Out. На вхід віднімача 26 поступає інформація з блока 22 (знайдене мінімальне число). Керуючий сигнал встановлюється в стан лог. 0. За допомогою керуючого сигналу Clock відбувається запис числа (A) з блока 26 в регістри блока 22, запис збільшеного на 1 числа (A + 1) з блока 26 в регістр 23.1, запис збільшеного на 2 числа (A + 2) з блока 26 в регістр 23.2. При подальших тактах пристрій працює в режимі дорівнює лог. 0. При поступленні вхідних чисел r1 - r2v блоки 21.1 і 22 визначають чи є серед них число A, блоки 21.2 і 23.1 визначають чи є серед них число A + 1, блоки 21.3 і 23.2 визначають чи є серед них число A + 2. Якщо число A є, то сигнал hit1 дорівнює лог. 1, якщо число A + 1 є, то сигнал hit2 дорівнює лог. 1, якщо число A + 2 є, то сигнал hit3 дорівнює лог. 1. На основі цієї інформації формується керуюче слово управлінням комутатором, - знову на вхід віднімача подасться мінімальне число. Декодований біт на кожному такті запам'ятовується у вихідному тригері сигналом Out. Блок 21.1 - 21.3 асоціативного пошуку працює наступним чином. Асоціативні комірки за допомогою суматорів по модулю два з інверсією порівнюють порозрядно вхідну інформацію з відповідними розрядами компаранда, якщо має місце співпадіння, то на виході N-розрядного кон'юнктора асоціативної комірки буде лог. 1. За допомогою сигналів маски M1 - M2 можна замаскувати всі або деякі розряди при асоціативному пошуку (1 - відповідний розряд замасковано, 0 - відповідний розряд не замасковано). Робота блока 22 формування маски і компаранда полягає в наступному. Блок 22 формування маски і . Коли сигнал компаранда може працювати в двох режимах, які задаються керуючим сигналом дорівнює лог. 1, то блок 22 працює в режимі пошуку, - за допомогою сигналів CI 1 - СI N, можливий запис інформації з в регістри 28.1 - 28.N з одночасним встановленням в стан лог. 0 на виході регістра маски наступного входу розряду. Коли сигнал дорівнює лог. 0, то блок 22 працює в режимі запису, - інформація з входів D1 - DN паралельно сигналом запису Clock записується в регістри 28.1 - 28.N. Блок тактування 17 на основі сигналів супроводу вхідної інформації CIk (сигнал тактування) і Beg (сигнал індикації початку поступлення інформації) і декодованої інформації з блоку прийняття рішення 7 формує сигнали управління для блока обчислення метрик гілок 1, першого комутатора 2, другого комутатора 3, третього комутатора 4, блока обчислення метрик 5, регістра 6, блока прийняття рішення 7, першого регістра зсуву 10, другого регістра зсуву 11, третього регістра зсуву 12, четвертого регістра зсуву 13, регістра корекції 14, кодера 15.

ДивитисяДодаткова інформація

Автори англійськоюMelnyk Anatolii Oleksiiovych

Автори російськоюМельник Анатолий Алексеевич

МПК / Мітки

МПК: H03M 13/23

Мітки: декодер, згорткового, коду

Код посилання

<a href="https://ua.patents.su/8-25556-dekoder-zgortkovogo-kodu.html" target="_blank" rel="follow" title="База патентів України">Декодер згорткового коду</a>