Захисний пристрій багатофункціонального перетворювача напруги

Номер патенту: 5795

Опубліковано: 15.03.2005

Автори: Масліков Анатолій Дмитрович, Бекіров Ескендер Алімович

Формула / Реферат

Захисний пристрій багатофункціонального перетворювача напруги, який містить блок мостового випрямляча, реалізований на першому - четвертому діодах, вхід якого з'єднаний з виходом першого трансформатора струму, а його вихід через перший резистивний подільник, реалізований на першому-третьому резисторах, з'єднаний з першим входом блоку порівняння й установки порога захисту, що являє собою компаратор, виконаний на операційному підсилювачі, другий вхід якого з'єднаний із движком потенціометра другого резистивного подільника напруги, реалізованого на четвертому-шостому резисторах, а вихід через третій резистивний подільник, реалізований на сьомому і восьмому резисторах, з'єднаний з першим входом «S» блоку пам'яті, вхід «R» якого з'єднаний із блоком установки схеми в нуль, прямий вихід блоку пам'яті з'єднаний зі схемою керування, а інверсний вихід блоку пам'яті з'єднаний із блоком захисного відключення, при цьому блок пам'яті виконаний на першому і другому логічних елементах «І-НІ», на яких реалізований «RS»-тригер, блок установки в нуль виконаний на послідовно з'єднаних дев'ятому резисторі і першому конденсаторі, середня точка яких підключена до входу «R» блоку пам'яті, який відрізняється тим, що пристрій містить два блоки захистів - блок струмового захисту і блок захисту від «наскрізних» струмів, при цьому блок струмового захисту додатково містить двополярне джерело опорної напруги, реалізоване на десятому гасильному резисторі, один вивід якого підключений до плюсового виводу джерела живлення, а другий вивід підключений до двох послідовно включених другого і третього конденсаторів, паралельно яким включені два - п'ятий і шостий - діоди-стабілітрони в запірному напрямку, причому до двополярного джерела опорної напруги підключений другий резистивний подільник, движок потенціометра якого підключений до інверсного входу компаратора, прямий вхід якого через перший резистивний подільник підключений до блоку мостового випрямляча, а блок захисту від «наскрізних» струмів додатково містить два однопівперіодних випрямлячі, зібраних на двох шунтуючих резисторах - одинадцятому і дванадцятому, одні виводи яких з'єднані між собою і з об'єднаними виводами другого і третього трансформаторів струму, і двох діодах - сьомому і восьмому, катоди яких з'єднані і підключені до тринадцятого гасильного резистора й аноду запірного - дев'ятого - діода, катод якого підключений до середнього виводу двополярного джерела опорної напруги, при цьому катоди двох однопівперіодних випрямлячів підключені до других виводів шунтуючих резисторів, до яких, у свою чергу, підключені другі виводи другого і третього трансформаторів струму, причому другий вивод гасильного резистора через логічний формивач-інвертор, реалізованого на третьому логічному елементі «І-НІ», надходить на другий вхід «S» блоку пам'яті на «RS»-тригері, при цьому блок захисного відключення складається з генератора імпульсів, одновібратора, підсилювального транзисторно-трансформаторного каскаду, мостового мережного випрямляча, вихід якого навантажений на тиристор з LC-згладжувальним фільтром, причому інверсний вихід «RS»-тригера підключений до першого входу генератора імпульсів, реалізованого на двох - четвертому і п'ятому - двовходових логічних елементах «І-НІ», чотирнадцятому резисторі, підключеному до другого входу генератора імпульсів і до виходу четвертого логічного елемента «І-НІ», вихід якого підключений до об'єднаних входів п'ятого логічного елемента «І-НІ», і четвертому конденсаторі, підключеному між другим входом генератора імпульсів і його виходом, до якого підключений вхід одновібратора, реалізованого на двох - шостому і сьомому - двовходових логічних елементах «І-НІ», при цьому входи шостого логічного елемента «І-НІ» об'єднані і підключені до виходу генератора імпульсів, а вихід шостого логічного елемента «І-НІ» через п'ятнадцятий резистор підключений до першого входу сьомого логічного елемента «І-НІ», другий вхід якого підключений до виходу генератора імпульсів, при цьому перший вивод п'ятого конденсатора підключений до першого входу сьомого логічного елемента «І-НІ», а другий вивід п'ятого конденсатора підключений до мінуса джерела, причому вихід одновібратора через четвертий резистивний подільник, реалізований на шістнадцятому і сімнадцятому резисторах, підключений до підсилювального транзисторно-трансформаторного каскаду, реалізованого на транзисторі, у колекторний ланцюг якого включена первинна обмотка імпульсного трансформатора, зашунтована ланцюжком з десятого діода і восімнадцятого резистора, а вторинна обмотка імпульсного трансформатора навантажена через дев'ятнадцятий резистор на перехід катод - керуючий електрод тиристора, включеного на виході мостового випрямляча на діодах одинадцять - чотирнадцять, вхід якого підключений до напруги мережі змінного струму, причому вихід тиристора з'єднаний через п'ятнадцятий діод з LC-згладжувальним фільтром, реалізованим на дроселі і шостому конденсаторі, при цьому перший резистор підключений також до анода шістнадцятого розв’язувального діода, катод якого з'єднаний із плюсом двополярного джерела опорної напруги.

Текст

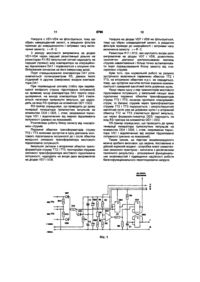

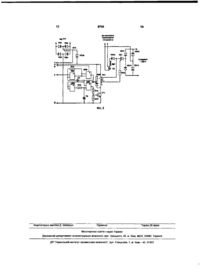

Захисний пристрій багатофункціонального перетворювача напруги, який містить блок мостового випрямляча, реалізований на першому - четвертому діодах, вхід якого з'єднаний з виходом першого трансформатора струму, а його вихід через перший резистивний подільник, реалізований на першому-третьому резисторах, з'єднаний з першим входом блоку порівняння й установки порога захисту, що являє собою компаратор, виконаний на операційному підсилювачі, другий вхід якого з'єднаний із движком потенціометра другого резистивного подільника напруги, реалізованого на четвертому-шостому резисторах, а вихід через третій резистивний подільник, реалізований на сьомому і восьмому резисторах, з'єднаний з першим входом «S» блоку пам'яті, вхід «R» якого з'єднаний із блоком установки схеми в нуль, прямий вихід блоку пам'яті з'єднаний зі схемою керування, а інверсний вихід блоку пам'яті з'єднаний із блоком захисного відключення, при цьому блок пам'яті виконаний на першому і другому логічних елементах «І-НІ», на яких реалізований «RS»тригер, блок установки в нуль виконаний на послідовно з'єднаних дев'ятому резисторі і першому конденсаторі, середня точка яких підключена до входу «R» блоку пам'яті, який відрізняється тим, що пристрій містить два блоки захистів - блок струмового захисту і блок захисту від «наскрізних» струмів, при цьому блок струмового захисту додатково містить двополярне джерело опорної напруги, реалізоване на десятому гасильному резисторі, один вивід якого підключений до плюсового виводу джерела живлення, а другий вивід підключений до двох послідовно включених другого і третього конденсаторів, паралельно яким включені два п'ятий і шостий - дюди-стабілітрони в запірному напрямку, причому до двополярного джерела опорної напруги підключений другий резистивний подільник, движок потенціометра якого підключений до інверсного входу компаратора, прямий вхід якого через перший резистивний подільник під ключений до блоку мостового випрямляча, а блок захисту від «наскрізних» струмів додатково містить два однопівперюдних випрямлячі, зібраних на двох шунтуючих резисторах - одинадцятому і дванадцятому, одні виводи яких з'єднані між собою і з об'єднаними виводами другого і третього трансформаторів струму, і двох діодах - сьомому і восьмому, катоди яких з'єднані і підключені до тринадцятого гасильного резистора й аноду запірного - дев'ятого - діода, катод якого підключений до середнього виводу двополярного джерела опорної напруги, при цьому катоди двох однопівперюдних випрямлячів підключені до других виводів шунтуючих резисторів, до яких, у свою чергу, підключені другі виводи другого і третього трансформаторів струму, причому другий вивод гасильного резистора через логічний формивач-інвертор, реалізованого на третьому логічному елементі «І-НІ», надходить на другий вхід «S» блоку пам'яті на «RS»-Tpnrepi, при цьому блок захисного відключення складається з генератора імпульсів, одновібратора, підсилювального транзисторнотрансформаторного каскаду, мостового мережного випрямляча, вихід якого навантажений на тиристор з LC-згладжувальним фільтром, причому інверсний вихід «RSw-тригера підключений до першого входу генератора імпульсів, реалізованого на двох - четвертому і п'ятому - двовходових логічних елементах «І-НІ», чотирнадцятому резисторі, підключеному до другого входу генератора імпульсів і до виходу четвертого логічного елемента «І-НІ», вихід якого підключений до об'єднаних входів п'ятого логічного елемента «І-НІ», і четвертому конденсаторі, підключеному між другим входом генератора імпульсів і його виходом, до якого підключений вхід одновібратора, реалізованого на двох - шостому і сьомому - двовходових логічних елементах «І-НІ», при цьому входи шостого логічного елемента «І-НІ» об'єднані і підключені до виходу генератора імпульсів, а вихід шостого логічного елемента «І-НІ» через п'ятнадцятий резистор підключений до першого входу сьомого логічного елемента ЛІНІ», другий вхід якого підключений до виходу генератора імпульсів, при цьому перший вивод п'ятого конденсатора підключений до першого входу сьомого логічного елемента «І-НІ», а другий вивід п'ятого конденсатора підключений до мінуса джерела, причому вихід одновібратора через четвер ю о 5795 тий резистивний подільник, реалізований на шістнадцятому і сімнадцятому резисторах, підключений до підсилювального транзисторнотрансформаторного каскаду, реалізованого на транзисторі, у колекторний ланцюг якого включена первинна обмотка імпульсного трансформатора, зашунтована ланцюжком з десятого діода і восімнадцятого резистора, а вторинна обмотка імпульсного трансформатора навантажена через дев'ятнадцятий резистор на перехід катод - керуючий електрод тиристора, включеного на виході мостового випрямляча на діодах одинадцять - чотирнадцять, вхід якого підключений до напруги мережі змінного струму, причому вихід тиристора з'єднаний через п'ятнадцятий діод з LC-згладжувальним фільтром, реалізованим на дроселі і шостому конденсаторі, при цьому перший резистор підключений також до анода шістнадцятого розв'язувального діода, катод якого з'єднаний із плюсом двополярного джерела опорної напруги Корисна модель відноситься до пристроїв захисту джерел живлення від перевантажень і коротких замикань і може бути використана в різних перетворювачах напруги ВІДОМІ стабілізатори з струмовим захистом від короткого замикання [1 Журнал «Радіо», №2 1975р, с 23, 2 У допомогу радіоаматору, изд ДТСААФ СРСР, вып №47, с 35, 3 Те ж, вип 49 с 47, 4 Те ж, вип 56 с 43], що містять схеми стабілізаторів напруги на складених транзисторах, у яких реалізоване схемотехничне рішення струмового захисту від короткого замикання Недоліками відомих пристроїв є неможливість точної установки спрацьовування струмового захисту, незважаючи на простоту цих пристроїв, а також обмежені функціональні можливості пристрою, що не дозволяють захищати перетворювач напруги від «наскрізних» струмів у мостової підсилювачі потужності Відомий пристрій струмового захисту, описаний в [«Інверторі квазісінусощальної напруги» Патент України №57451 А, МПК-7 Н02М7/5395, бюл №6, 2003р ], який складається з блоку випрямляча, блоку порівняння й установки порога захисту, блоку пам'яті, блоку установки схеми в нуль, блоку індикації «перевантаження» Недоліком відомого пристрою є обмежені функціональні можливості пристрою, що не дозволяють захищати перетворювач напруги від «наскрізних» струмів у мостової підсилювачі потужності Найбільш близьким по технічній сутності і результату, що досягається, і обраним як прототип є «Пристрій струмового захисту - 2», який містить блок мостового випрямляча, вхід якого з'єднаний з виходом трансформатора струму, а його вихід з'єднаний із входом блоку, що інвертує, порівняння й установки порога захисту, що представляє собою компаратор, виконаний на операційному підсилювачі, прямий вхід якого з'єднаний із движком потенціометра резистивного дільника напруги, а вихід з'єднаний із входом «S» блоку пам'яті, вхід «R» якого з'єднаний із блоком установки схеми в нуль, а прямої вихід блоку пам'яті з'єднаний зі схемою імпульсного стабілізатора, а інверсний вихід блоку пам'яті з'єднаний із блоком індикації «перевантаження», виконаного на транзисторному підсилювальному каскаді зі світлодюдним індикатором, при цьому блок пам'яті виконаний на двох логічних елементах «И», на яких реалізований «RSw-тригер, причому інверсний вихід блоку пам'яті з'єднаний із блоком індикації через інвертор, вихід блоку мостового випрямляча зашунтован резистором, блок установки в нуль виконаний на послідовно з'єднаних резисторі і конденсаторі, середня крапка яких підключена до входу «R» блоку пам'яті, а конденсатор блоку установки схеми в нуль зашунтован резистором Недоліком прототипу є обмежені функціональні можливості пристрою, що не дозволяють захищати перетворювач напруги від «наскрізних» струмів у мостової підсилювачі потужності Задачею дійсної корисної моделі є розробка нової схемотехники захисного пристрою з досягненням технічного результату - розширення функціональних можливостей і підвищення надійності роботи багатофункціонального перетворювача напруги Поставлена задача досягається тим, що в «Захисний пристрій багатофункціонального перетворювача напруги», який містить блок мостового випрямляча, реалізований на першому - четвертому діодах, вхід якого з'єднаний з виходом першого трансформатора струму, а його вихід через перший резистивний дільник, реалізований на першому - третьому резисторах, з'єднаний з першим входом блоку порівняння й установки порога захисту, що представляє собою компаратор, виконаний на операційному підсилювачі, другий вхід якого з'єднаний із движком потенціометра другого резистивного дільника напруги, реалізованого на четвертому - шостому резисторах, а вихід через третій резистивний дільник, реалізований на сьомому і восьмому резисторах, з'єднаний з першим входом «S» блоку пам'яті, вхід «R» якого з'єднаний із блоком установки схеми в нуль, прямий вихід блоку пам'яті з'єднаний зі схемою керування, а інверсний вихід блоку пам'яті з'єднаний із блоком захисного відключення, при цьому блок пам'яті виконаний на першому і другому логічних елементах «І-НІ», на яких реалізований «RS»-Tpnrep, блок установки в нуль виконаний на послідовно з'єднаних дев'ятому резисторі і першому конденсаторі, середня крапка яких підключена до входу «R» блоку пам'яті, при цьому пристрій містить два блоки захистів - блок струмового захисту і блок захисту від «наскрізних» струмів, при цьому блок струмового захисту додатково містить двохполярне джерело опорної напруги, реалізоване на десятому гасильному резисторі, один вивід якого підключений до плюсовому виводу джерела живлення, а другий вивід підключений до двох послідовно включеного другому і третьому конденсаторам, паралельно яким включені два - п'ятий і шостий дюди-стабілітрони в запірному напрямку, причому 5795 до двохполярного джерела опорної напруги підключений другий резистивнии дільник, движок потенціометра якого підключений до інверсного входу компаратора, прямий вхід якого через перший резистивный дільник підключений до блоку мостового випрямляча, а блок захисту від «наскрізних» струмів додатково містить два однопівперюдних випрямляча, зібраних на двох шунтуючих резисторах - одинадцятому і дванадцятому, одні виводи яких з'єднані між собою і з об'єднаними виводами другого і третього трансформаторів струму, і двох діодах - сьомому і восьмому, катоди яких з'єднані і підключені до тринадцятого гасильному резистору, й аноду запірного - дев'ятого діода, катод якого підключений до середнього виводу двухполярного джерела опорної напруги, при цьому катоди двох однопівперюдних випрямлячів підключені до других виводів шунтуючих резисторів, до яких, у свою чергу, підключені другі виводи другого і третього трансформаторів струму, причому другий вивід гасильного резистора, через логічний формувач-інвертор, реалізований на третьому логічному елементі «І-НІ», надходить на другий вхід «S» блоку пам'яті на «RS»-Tpnrepi, при цьому блок захисного відключення складається з генератора імпульсів, одновібратора, підсилювального транзисторно-трансформаторного каскаду, мостового мережного випрямляча, вихід якого навантажений на тиристор з LC-фільтром, що згладжує, причому інверсний вихід «RS»-Tpnrepa підключений до першого входу генератора імпульсів, реалізованого на двох - четвертому і п'ятому двохвходових логічних елементах «І-НІ», чотирнадцятому резисторі, підключеному до другого входу генератора імпульсів і до виходу четвертого логічного елемента «ІИ-НІ», вихід якого підключений до об'єднаних входів п'ятого логічного елемента «IНІ», і четвертому конденсаторі, підключеним між другим входом генератора імпульсів і його виходом, до якого підключений вхід одновібратора, реалізованого на двох - шостому і сьомому - двох входових логічних елементах «І-НІ», при цьому входи шостого логічного елемента «І-НІ» об'єднані і підключені до виходу генератора імпульсів, а вихід шостого логічного елемента «І-НІ» через п'ятнадцятий резистор підключений до першого входу сьомого логічного елемента «І-НІ», другий вхід якого підключений до виходу генератора імпульсів, при цьому перший вивід п'ятого конденсатора підключений до першого входу сьомого логічного елемента «І-НІ», а другий вивід п'ятого конденсатора підключений до мінуса джерела, причому вихід одновібратора через четвертий резистивнии дільник, реалізований на шістнадцятому і сімнадцятому резисторах, підключений до підсилювального транзисторно-трансформаторного каскаду, реалізованому на транзисторі, у колекторний ланцюг якого включена первинна обмотка імпульсного трансформатора, зашунтована ланцюжком з десятого діода і вісімнадцятого резистора, а вторинна обмотка імпульсного трансформатора навантажена через дев'ятнадцятий резистор на перехід катодий-керуючий електрод тиристора, включеного на виході мостового випрямляча на діодах одинадцять - чотирнадцять, вхід якого підключений до напруги мережі перемінного струму, причому вихід тиристора з'єднаний через п'ятнадцятий діод з LCфільтром, що згладжує, реалізованим на дроселі і шостому конденсатора, при цьому перший резистор підключений також до анода шістнадцятого діода, що розв'язує, катод якого з'єднаний із плюсом двохполярного джерела опорної напруги Новим у пристрої, що заявляється, є нова схемотехніка побудови захисного пристрою, що дозволяє - розширити функціональні можливості в порівнянні з прототипом, - підвищити надійність роботи багатофункціонального перетворювача напруги, - відключати багатофункціональний перетворювач напруги, що захищається, без ушкоджень при перевантаженнях і коротких замиканнях у навантаженні, - відключати багатофункціональний перетворювач напруги, що захищається, без ушкоджень при протіканні «наскрізних» струмів у мостовому підсилювачі потужності Тому очевидно, що реалізація пристрою, що заявляється, дозволить виконати задачу, поставлену в ДІЙСНІЙ корисній моделі, з досягненням технічного результату - розширення функціональних можливостей і підвищення надійності роботи багатофункціонального перетворювача напруги Суттєвими ознаками пристрою, що заявляється, співпадаючими з прототипом, є наступні ознаки - блок мостового випрямляча, реалізований на першому - четвертому діодах, - вхід блок мостового випрямляча з'єднаний з виходом першого трансформатора струму, - вихід блок мостового випрямляча через перший резистивнии дільник, реалізований на першому - третьому резисторах, з'єднаний з першим входом блоку порівняння й установки порога захисту, - блоку порівняння й установки порога захисту являє собою компаратор, виконаний на операційному підсилювачі, - другий вхід компаратора з'єднаний із движком потенціометра другого резистивного дільника напруги, реалізованого на четвертому - шостому резисторах, - вихід компаратора через третій резистивный дільник, реалізований на сьомому і восьмому резисторах, з'єднаний з першим входом «S» блоку пам'яті, - вхід «R» блоку пам'яті з'єднаний із блоком установки схеми в нуль, - прямий вихід блоку пам'яті з'єднаний зі схемою керування, - інверсний вихід блоку пам'яті з'єднаний із блоком захисного відключення, - блок пам'яті виконаний на першому і другому логічних елементах «І-НІ», на яких реалізований «RS»-Tpnrep, - блок установки в нуль виконаний на послідовно з'єднаних дев'ятому резисторі і першому конденсаторі, середня крапка яких підключена до входу «R» блоку пам'яті 5795 ВІДМІТНИМИ ВІД прототипу суттєвими ознаками пристрою, що заявляється, є наступні ознаки - пристрій містить два блоки захистів - блок струмового захисту і блок захисту від «наскрізних» струмів, - при цьому блок струмового захисту додатково містить - двохполярне джерело опорної напруги, реалізований на десятому гасильному резисторі, один вивід якого підключений до плюсового виводу джерела живлення, а другий вивід підключений до двох послідовно включеного другому і третьому конденсаторам, паралельно яким включені два п'ятий і шостий - дюди-стабілітрони в запірному напрямку, - до двохполярного джерела опорної напруги підключений другий резистивний дільник, движок потенціометра якого підключений до інверсного входу компаратора, - прямий вхід компаратора через перший резистивний дільник підключений до блоку мостового випрямляча, - блок захисту від «наскрізних» струмів додатково містить - два однопівперюдних випрямляча, зібраних на двох шунтуючих резисторах - одинадцятому і дванадцятому, одні виводи яких з'єднані між собою і з об'єднаними виводами другого і третього трансформаторів струму, і двох діодах - сьомому і восьмому, катоди яких з'єднані і підключені до що гасить - тринадцятому - резистору й аноду запірного - дев'ятого - діода, катод якого підключений до середнього виводу двохполярного джерела опорної напруги, - катоди двох однопівперюдних випрямлячів підключені до других виводів шунтуючих резисторів, до яких, у свою чергу, підключені другі виводи другого і третього трансформаторів струму, - другий вивід гасильного резистора, через логічний формувач-інвертор, реалізованому на третьому логічному елементі «І-НІ», надходить на другий вхід «S» блоку пам'яті на «RS»-Tpnrepi, - блок захисного відключення складається з - генератора імпульсів, одновібратора, підсилювального транзисторно-трансформаторного каскаду, мостового мережного випрямляча, вихід якого навантажений на тиристор з LC-фільтром, що згладжує, - інверсний вихід «RS»-Tpnrepa підключений до першого входу генератора імпульсів, реалізованого на двох - четвертому і п'ятому - двохвходових логічних елементах «І-НІ», чотирнадцятому резисторі, підключеному до другого входу генератора імпульсів і до виходу четвертого логічного елемента «І-НІ», вихід якого підключений до об'єднаних входів п'ятого логічного елемента «І-НІ», і четвертому конденсаторі, підключеним між другим входом генератора імпульсів і його виходом, - до виходу генератора імпульсів підключений вхід одновібратора, реалізованого на двох - шостому і сьомому - двохвходових логічних елементах «І-НІ», при цьому входи шостого логічного елемента «І-НІ» об'єднані і підключені до виходу генератора імпульсів, а вихід шостого логічного елемента «І-НІ» через п'ятнадцятий резистор підключений 8 до першого входу сьомого логічного елемента «IНІ», другий вхід якого підключений до виходу генератора імпульсів, при цьому перший вивід п'ятого конденсатора підключений до першому входу сьомого логічного елемента «І-НІ», а другий вивід п'ятого конденсатора підключений до мінуса джерела, - вихід одновібратора через четвертий резистивный дільник, реалізований на шістнадцятому і сімнадцятому резисторах, підключений до підсилювального транзисторно-трансформаторного каскаду, реалізованому на транзисторі, у колекторний ланцюг якого включена первинна обмотка імпульсного трансформатора, зашунтована ланцюжком з десятого діода і вісімнадцятого резистора, - вторинна обмотка імпульсного трансформатора навантажена через дев'ятнадцятий резистор на перехід катод-керуючий електрод тиристора, включеного на виході мостового випрямляча на діодах одинадцять - чотирнадцять, вхід якого підключений до напруги мережі перемінного струму, - вихід тиристора з'єднаний через п'ятнадцятий діод з LC-фільтром, що згладжує, реалізованим на дроселі і шостому конденсатора, - перший резистор підключений також до анода шістнадцятого діода, що розв'язує, катод якого з'єднаний із плюсом двухполярного джерела опорної напруги Між суттєвими ознаками корисної моделі, що заявляється, і технічним результатом, який досягається, існує наступний причинно-наслщковий зв'язок Дійсно, нова схемотехніка пристрою, що заявляється, відрізняється більш широкими функціональними можливостями, що дозволяють, у порівнянні з прототипом, підвищити надійність роботи багатофункціонального перетворювача напруги і відключати напругу багатофункціонального перетворювача без ушкоджень при перевантаженнях і коротких замиканнях у навантаженні, а також при протіканні «наскрізних» струмів у мостовому підсилювачі потужності Корисна модель ілюстрована наступними кресленнями На Фіг 1 і Фіг 2 зображена принципова електрична схема пристрою Захисний пристрій багатофункціонального перетворювача напруги містить блок мостового випрямляча, реалізований на діодах VD1-VD4, вхід якого з'єднаний з виходом першого трансформатора струму ТТ1 (умовно не показаного), що контролює струм навантаження багатофункціонального перетворювача напруги (умовно не показаний) Вихід МОСТОВОГО випрямляча через перший резистивний дільник, реалізований на резисторах R1-R3, з'єднаний з першим (прямим) входом блоку порівняння й установки порога захисту, що представляє собою компаратор, виконаний на операційному підсилювачі DA1, другий (інверсний) вхід з'єднаний із движком потенціометра R5, встановленого в послідовному ланцюзі з резисторами R4 і R6, підключеного до двохполярного джерела опорної напруги, при цьому вихід компаратора навантажений на третій резистивний дільник R7, R8, 5795 середня крапка якого з'єднана з входом «S» блоку пам'яті, вхід «R» якого з'єднаний із блоком установки схеми в нуль. Блок пам'яті виконаний на двох логічних елементах «І-НІ» DD1 і DD2, на яких реалізований «RS»-Tpnrep, при цьому прямий вихід блоку пам'яті з'єднаний зі схемою керування багатофункціонального перетворювача напруги, а інверсний вихід блоку пам'яті з'єднаний із блоком захисного відключення багатофункціонального перетворювача напруги. Блок установки в нуль виконаний на послідовно з'єднаних резисторі R9 і конденсаторі С1, середня крапка яких підключена до входу «R» блоку пам'яті. Пристрій, що заявляється, містить два блоки захистів - блок струмового захисту і блок захисту від «наскрізних» струмів. Блок струмового захисту додатково містить двуополярне джерело опорної напруги, реалізоване на гасильному резисторі R10, один вивід якого підключений до плюсового виводу джерела харчування, а другий вивід підключений до двох послідовно включених конденсаторів - С2 і СЗ, паралельно яким включені два діоди-стабілітрони VD5 і VD6 у запірному напрямку. Блок захисту від «наскрізних» струмів додатково містить два однопівперіодних випрямляча, зібраних на двох шунтуючих резисторах - R11 і R12, одні виводи яких з'єднані між собою і з об'єднаними виводами другого і третього трансформаторів струму (умовно не показані), і двох діодах VD7 і VD8, катоди яких з'єднані і підключені до гасильного резистора R13, і аноду запірного діода VD9, а його катод підключений до середнього виводу двохполярного джерела опорної напруги. Катоди двох однопівперіодних випрямлячів на двох діодах - VD7 і VD8 - підключені до других виводів шунтуючих резисторів - R11 і R12, до яких, у свою чергу, підключені другі виводи другого і третього трансформаторів струму, причому другий вивід гасильного резистора R13, через логічний формувач-інвертор, реалізований на третьому логічному елементі «І-НІ», надходить на другий вхід «S» блоку пам'яті на «RS»-Tpnrepi. Блок захисного відключення складається з генератора імпульсів, одновібратора, підсилювального транзисторно-трансформаторного каскаду, мостового мережного випрямляча , вихід якого навантажений на тиристор з LC-фільтром, що згладжує. Інверсний вихід «RS»-Tpnrepa підключений до першого входу генератора імпульсів, реалізованого на двох - четвертому і п'ятому - двохвходових логічних елементах «І-НІ» DD4 і DD5, чотирнадцятому резисторі R14, підключеному до другого входу генератора імпульсів і до виходу четвертого логічного елемента «І-НІ» DD4, вихід якого підключений до об'єднаних входів п'ятого логічного елемента «І-НІ» DD5, і четвертому конденсаторі С4, підключеним між другим входом генератора імпульсів і його виходом. До виходу генератора імпульсів підключений вхід одновібратора, реалізованого на двох - шостому і сьомому - двухвходових логічних елементах 10 «І-НІ» DD6 і DD7, при цьому входи шостого логічного елемента «І-НІ» DD6 об'єднані і підключені до виходу генератора імпульсів, а вихід шостого логічного елемента «І-НІ» DD6 через п'ятнадцятий резистор R15 підключений до першого входу сьомого логічного елемента «І-НІ» DD7, другий вхід якого підключений до виходу генератора імпульсів, при цьому перший вивід п'ятого конденсатора С5 підключений до першого входу сьомого логічного елемента «І-НІ» DD7, а другий виводу п'ятого конденсатора С5 підключений до мінуса джерела живлення. Вихід одновібратора через четвертий резистивний дільник, реалізований на шістнадцятому R16 і сімнадцятому резисторах R17, підключений до підсилювального транзисторнотрансформаторного каскаду, реалізованому на транзисторі VT1, у колекторний ланцюг якого включена первинна обмотка імпульсного трансформатора TV1, зашунтована ланцюжком з десятого діода DD10 і вісімнадцятого резистора R18. Вторинна обмотка імпульсного трансформатора TV1 навантажена через дев'ятнадцятий резистор R19 на перехід катод-керуючий електрод тиристора VS1, включеного на виході мостового мережного випрямляча на діодах одинадцять чотирнадцять VD11-VD14, вхід якого підключений до напруги мережі перемінного струму. Вихід тиристора VS1 з'єднаний через п'ятнадцятий діод VD15 з LC-фільтром, що згладжує, реалізованим на дроселі Др1 і шостому конденсатора С6. Перший резистор R1 підключений також до анода шістнадцятого діода, що розв'язує, VD16, катод якого з'єднаний із плюсом двухполярного джерела опорної напруги. Пристрій працює в такий спосіб Розглянемо роботу пристрою, який заявляється, у нормальному режимі, при відсутності спрацьовування захистів. Працює генератор прямокутних імпульсів на елементах DD4 і DD5, імпульси з якого надходять на одновібратор на елементах DD6 і DD7 для підвищення крутості фронтів сигналу, а, отже, для більш чіткої роботи всього пристрою при коливаннях живильної напруги і наявності імпульсних перешкод. Сформовані одновібратором сигнали надходять на підсилювальний транзисторнотрансформаторний каскад на транзисторі VT1, у колекторний ланцюг якого включена первинна обмотка імпульсного трансформатора TV1. Тут сигнали підсилюються і з вторинної обмотки імпульсного трансформатора TV1 через резистор R19 надходять на проміжок «катод-керуючий електрод» тиристора VS1. Тиристор VS1 при цьому відкривається і напруга харчування надходить на вихідний каскад мостового підсилювача потужності. Розглянемо роботу блоку струмового захисту Імпульсний сигнал із вторинної обмотки трансформатора струму Т И , пропорційний току силового трансформатора мостового підсилювача потужності, надходить на вхід мостового випрямляча на діодах VD1-VD4. 11 Напруга з VD1-VD4 не фільтрується, тому що обран швидкодіючий захист, а уведення фільтра приведе до инерционности і затримки часу включення захисту: т = R • С З виходу мостового випрямляча на діодах VD1-VD4 через перший резистивный дільник на резисторах R1-R3 імпульсний сигнал надходить на перший (прямої) вхід компаратора на операційному підсилювачі DA1 і порівнюється з опорним стабілізованим сигналом на його інверсному вході. Поріг спрацьовування компаратора DA1 установлюється потенціометром R5, движок якого з'єднаний із другим (інверсним) входом компаратора DA1. При перевищенні сигналу (тобто при перевищенні вихідного струму підсилювача потужності) на прямому вході компаратора DA1 порога спрацьовування, на виході компаратора DA1 з'являються негативні прямокутні імпульси, що надходять на вхід RS-тригера на елементах DD1 і DD2. RS-тригер спрацьовує, що приводить до зриву генерації генератора прямокутних імпульсів на елементах DD4 і DD5, і, отже, закриванню тиристора VS1 і відключенню від мережі підсилювача потужності (умовно не показаний). Розглянемо роботу блоку захисту від «наскрізних» струмів Первинні обмотки трансформаторів струму ТТ2 і ТТЗ включені зустрічне в одну діагональ мостового підсилювача потужності до і після обмотки вихідного силового трансформатора мостового підсилювача потужності. Імпульсні сигнали з вторинних обмоток трансформаторів струму ТТ2 і ТТЗ, пропорційні струмам силового трансформатора мостового підсилювача потужності, надходять на входи двох випрямлячів на діодах VD7 і VD8. 5795 12 Напруги на діодах VD7 і VD8 не фільтрується, тому що обран швидкодіючий захист, а уведення фільтрів приведе до инерційності і затримки часу включення захисту: т = R • С Резистори R11 і R12, яки шунтують входи двох випрямлячів на діодах VD7 і VD8, дозволяють «розтягти» діапазон контрольованих значень струмів навантаження і більш точно встановлювати поріг спрацьовування блоку захисту від «наскрізних» струмів. Крім того, при нормальній роботі за рахунок зустрічного включення первинних обмоток ТГ2 і ТТЗ, на вторинних обмотках е.р.с. не наводиться, тому, що зустрічні магнітні потоки взаємно компенсуються і сумарний магнітний потік дорівнює нулю. Якщо через одну з пар транзисторів мостового підсилювача потужності, у загальний ланцюг яких підключені первинні обмотки трансформаторів струму ТТ2 і ТТЗ, починає протікати «наскрізний» струм, то баланс струмів через трансформатори струмів ТТ2 і ТТЗ порушується, і результируючий магнітний потік уже не дорівнює нулю і у вторинній обмотці ТТ2 чи ТТЗ з'являється фронт імпульсу, що через формувач-інвертор DD3, надходить на вхід RS-тригера на елементах DD1 і DD2. RS-тригер спрацьовує, що приводить до зриву генерації генератора прямокутних імпульсів на елементах DD4 і DD5, і, отже, закриванню тиристора VS1 і відключенню від мережі підсилювача потужності (умовно не показаний). Таким чином, на підставі вищевикладеного можна зробити висновок, що задача, поставлена в дійсній корисній моделі - розробка нової схемотехніки захисного пристрою - виконана з досягненням технічного результату - розширення функціональних можливостей і підвищення надійності роботи багатофункціонального перетворювача напруги. ФІГ. 1 13 S795 14 Фіг. 2 Комп'ютерна верстка Д Шеверун Підписне Тираж 28 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул Урицького, 45, м Київ, МСП, 03680, Україна ДП "Український інститут промислової власності", вул Глазунова, 1, м Київ-42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюProtection device for a multifunctional voltage converter

Автори англійськоюBekirov Eskender Alimovych, Maslikov Anatolii Dmytrovych

Назва патенту російськоюУстройство защиты многофункционального преобразователя напряжения

Автори російськоюБекиров Эскендер Алимович, Масликов Анатолий Дмитриевич

МПК / Мітки

МПК: H02M 7/539

Мітки: багатофункціонального, захисний, пристрій, напруги, перетворювача

Код посилання

<a href="https://ua.patents.su/8-5795-zakhisnijj-pristrijj-bagatofunkcionalnogo-peretvoryuvacha-naprugi.html" target="_blank" rel="follow" title="База патентів України">Захисний пристрій багатофункціонального перетворювача напруги</a>

Попередній патент: Декоративний чохол для пляшки

Наступний патент: Привід гідроклинового пристрою – 1

Випадковий патент: Регулятор довжини лямки ременя безпеки транспортного засобу