Пристрій для адресації функціональних блоків

Номер патенту: 82286

Опубліковано: 25.07.2013

Автори: Одноралов Ігор Васильович, Гавриленко Валерій Володимирович, Шульга Олександр Васильович, Козелкова Катерина Сергіївна

Формула / Реферат

Пристрій для адресації функціональних блоків, що містить RS-тригери, тактовий вхід пристрою та виходи вибірки функціональних блоків, при цьому перший та другий Q-виходи (i-1)-го RS-тригера з'єднано, відповідно, з входами S та R i-го RS-тригера, тактові входи RS-тригерів з'єднано і об'єднано у С-вхід кожного RS-тригера кожного з функціональних блоків, а перший Q-вихід кожного RS-тригера додатково підключено до виходів вибірки функціональних блоків кожного із зазначених функціональних блоків, який відрізняється тим, що до складу пристрою додатково введено тригери вибірки, перші та другі вузли переносу по кількості функціональних блоків та канали зв'язку вузлів переносу, перший вузол переносу розміщено в ланцюзі між Q-виходом (і-1)-го RS-тригера та S-входом i-го RS-тригера, а другий вузол переносу розміщено в ланцюзі між Q-виходом (і-1)-го RS-тригера та R-входом i-го RS-тригера, перший та другий вузли переносу містять елемент АБО та два елементи ТА, при цьому перші виходи першого та другого вузлів переносу (і-1)-го RS-тригера з'єднано, відповідно, з S та R входами (і-1)-го RS-тригера, Q-виходи (і-1)-го RS-тригера з'єднано з першими входами першого та другого вузлів переносу відповідно i-го RS-тригера, Q-виходи i-го RS-тригера з'єднано з першими входами першого та другого вузлів переносу відповідно (i+1)-го RS-тригера, перші виходи першого та другого вузлів переносу i-го RS-тригера з'єднано, відповідно, з S та R входами i-го RS-тригера, другі виходи першого та другого вузлів переносу (і-1)-го RS-тригера з'єднано з другими входами першого та другого вузлів переносу відповідно i-го RS-тригера каналом зв'язку, другі виходи першого та другого вузлів переносу i-го RS-тригера з'єднано з другими входами першого та другого вузлів переносу відповідно (i+1)-го RS-тригера каналом зв'язку, треті входи першого та другого вузлів переносу (і-1)-го RS-тригера з'єднано з виходом (і-1)-го тригера придатності (і-1)-го функціонального блока, треті входи першого та другого вузлів переносу i-го RS-тригера з'єднано з виходом і-го тригера придатності i-го функціонального блока, треті входи першого та другого вузлів переносу (i+1)-го RS-тригера з'єднано з виходом (i+1)-го тригера придатності (i+1)-го функціонального блока, перший вихід першого вузла переносу (i-1)-го функціонального блока з'єднано з першими входами першого вузла переносу (i+l)-го RS-тригера через S-вхід та Q-вихід, відповідно, (i-1)-го та i-го RS-тригера, перший вихід другого вузла переносу (i-1)-го функціонального блока з'єднано з першими входами другого вузла переносу (i+1)-го RS-тригера через R-вхід та Q-вихід, відповідно, (i-1)-го та і-го RS-тригера, причому безпосередньо в кожному першому та другому вузлах переносу перші та другі входи зазначених першого та другого вузлів переносу з'єднано з входом елемента АБО, вихід елемента АБО з'єднано з першими входами елементів ТА, другий інверсний вхід першого елемента ТА та другий прямий вхід другого елемента ТА з'єднано з третім входом першого та другого вузлів переносу, а виходи першого та другого елементів ТА є, відповідно, першим та другим виходами першого та другого вузлів переносу.

Текст

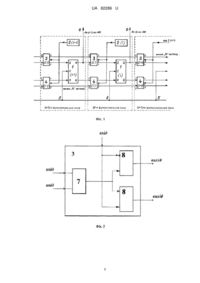

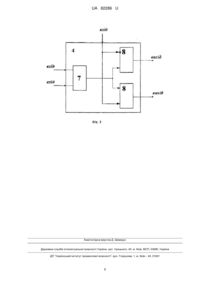

Реферат: Пристрій для адресації функціональних блоків містить RS-тригери, тактовий вхід пристрою та виходи вибірки функціональних блоків. До складу пристрою додатково введено тригери вибірки, перші та другі вузли переносу по кількості функціональних блоків та канали зв'язку вузлів переносу. UA 82286 U (12) UA 82286 U UA 82286 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до галузі автоматики та обчислювальної техніки, зокрема до приладів та пристроїв обчислювальної техніки, а саме, до пристроїв для адресації функціональних блоків, і може бути використана при комплектуванні обчислювальної техніки для адресації будь-яких функціонально закінчених блоків, саме - процесорів, блоків пам'яті тощо. Відомий пристрій для адресації блоків пам'яті, який містить групу перемикачів, регістр адреси, інформаційний вхід регістра адреси, дешифратор адреси та групу елементів АБО, при цьому інформаційний вхід регістра адреси є адресним входом пристрою [1]. До недоліків відомого пристрою для адресації блоків пам'яті належить їх вузька область застосування, оскільки пристрій орієнтовано на роботу з адресами в паралельному коді. Відомий пристрій для адресації пам'яті, що містить групу перемикачів, групу суматорів, групу елементів порівняння, групу блоків пам'яті, групу дешифраторів та групу комутаторів [2]. До недоліків відомого пристрій для адресації пам'яті належить їх вузька область застосування, оскільки пристрій розроблено для роботи з адресами в паралельному коді. У тому випадку, якщо адреси представлені послідовним одиничним кодом, необхідно їх попереднє перетворення у паралельний код, але при цьому неможливий перехід до наступного блока подачею ще одного імпульсу (по типу покрокового шукача). Найбільш близьким технічним рішенням як за суттю, так і за задачею, що вирішується, яке вибрано за найближчий аналог (прототип), є пристрій для адресації функціональних блоків, що містить RS-тригери, тактовий вхід пристрою та виходи вибірки функціональних блоків, при цьому перший та другий Q-виходи (i-1)-го RS-тригера з'єднано, відповідно, з входами S та R і-го RS-тригера, тактові входи RS-тригерів з'єднано і об'єднано у С-вхід кожного RS-тригера кожного з функціональних блоків, а перший Q-вихід кожного RS-тригера додатково підключено до виходів вибірки функціональних блоків кожного із зазначених функціональних блоків [3]. До недоліків відомого пристрою для адресації функціональних блоків, який вибрано за найближчий аналог (прототип), належить його низька функціональна спроможність, пов'язана з неможливістю виключення з обігу відключених та непридатних функціональних блоків. Якщо Qвиходи розрядів пристрою з'єднати з входами вибірки функціональних блоків, то зазначений пристрій для адресації функціональних блоків можна використовувати для адресації функціональних блоків, якщо адреси представлено послідовним одиничним кодом, в якому число "1" представляється послідовністю із l одиниць. В основу корисної моделі поставлено задачу шляхом введення до складу пристрою тригерів вибірки та вузлів переносу забезпечити розширення функціональних можливостей пристрою. Суть технічного рішення у пристрої для адресації функціональних блоків, що містить RSтригери, тактовий вхід пристрою та виходи вибірки функціональних блоків, при цьому перший та другий Q-виходи (i-1)-го RS-тригера з'єднано, відповідно, з входами S та R і-го RS-тригера, тактові входи RS-тригерів з'єднано і об'єднано у С-вхід кожного RS-тригера кожного з функціональних блоків, а перший Q-вихід кожного RS-тригера додатково підключено до виходів вибірки функціональних блоків кожного із зазначених функціональних блоків, полягає в тому, що до складу пристрою додатково введено тригери вибірки, перші та другі вузли переносу по кількості функціональних блоків та канали зв'язку вузлів переносу, перший вузол переносу розміщено у ланцюзі між Q-виходом (i-1)-го RS-тригера та входом S-входом і-го RS-тригера, а другий вузол переносу розміщено у ланцюзі між Q-виходом (i-1)-го RS-тригера та R-входом і-го RS-тригера, перший та другий вузли переносу містять елемент АБО та два елементи ТА. Суть корисної моделі полягає і в тому, що перші виходи першого та другого вузлів переносу (i-1)-го RS-тригера з'єднано, відповідно, з S та R входами (i-1)-го RS-тригера, Q-виходи (i-1)-го RSтригера з'єднано з першими входами першого та другого вузлів переносу відповідно і-го RSтригера, Q-виходи і-го RS-тригера з'єднано з першими входами першого та другого вузлів переносу відповідно (i+1)-го RS-тригера, перші виходи першого та другого вузлів переносу і-го RS-тригера з'єднано, відповідно, з S та R входами і-го RS-тригера, другі виходи першого та другого вузлів переносу (i-1)-го RS-тригера з'єднано з другими входами першого та другого вузлів переносу відповідно і-го RS-тригера каналом зв'язку, другі виходи першого та другого вузлів переносу і-го RS-тригера з'єднано з другими входами першого та другого вузлів переносу відповідно (i+1)-го RS-тригера каналом зв'язку, треті входи першого та другого вузлів переносу (i-1)-го RS-тригера з'єднано з виходом (i-1)-го тригера придатності (i-1)-го функціонального блока, треті входи першого та другого вузлів переносу і-го RS-тригера з'єднано з виходом і-го тригера придатності і-го функціонального блока, треті входи першого та другого вузлів переносу (i+1)-го RS-тригера з'єднано з виходом (i+1)-го тригера придатності (i+1)-го функціонального блока, перший вихід першого вузла переносу (i-1)-го функціонального блока з'єднано з першими входами першого вузла переносу (i+1)-го RS-тригера через S-вхід та Q-вихід, відповідно, (i-1)-го 1 UA 82286 U 5 10 15 20 25 30 35 40 45 50 55 та і-го RS-тригера, перший вихід другого вузла переносу (i-1)-го функціонального блока з'єднано з першими входами другого вузла переносу (i+1)-го RS-тригера через R-вхід та Q-вихід, відповідно, (i-1)-го та і-го RS-тригера. Суть корисної моделі полягає також і в тому, що безпосередньо в кожному першому та другому вузлах переносу перші та другі входи зазначених першого та другого вузлів переносу з'єднано з входом елемента АБО, вихід елемента АБО з'єднано з першими входами елементів ТА, другий інверсний вхід першого елемента ТА та другий прямий вхід другого елемента ТА з'єднано з третім входом першого та другого вузлів переносу, а виходи першого та другого елементів ТА є, відповідно, першим та другим виходами першого та другого вузлів переносу. Рішення поставленої задачі дійсно можливе тому, що поставлена задача виконується внесенням змін до схемно-технічного рішення пристрою для адресації функціональних блоків, а саме - додатково вводяться тригери вибірки та вузли переносу, що дозволяє виключити з обігу вимкнуті та непридатні функціональні блоки. При цьому адресі звернення «l» буде завжди відповідати i-тий функціональний блок із числа не вимкнених з придатних функціональних блоків (відповідно, функціональних блоків «(i-1,)» та «i»). Вибір наступного, (i-1)-го не вимкнутого функціонального блока буде здійснюватися подачею тільки одного синхроімпульсу. Отримання позитивного ефекту при реалізації суті технічного рішення, покладеного в основу корисної моделі, досягається введенням вузлів переносу та тригерів вибірки у склад пристрою для адресації функціональних блоків. У даному випадку пристрій для адресації функціональних блоків, що заявляється, дозволить здійснювати обминання непридатних блоків пам'яті у відповідності зі станом тригерів придатності та, крім того, дозволить перейти до наступних блоків пам'яті. Так, для того, щоб після вибірки і-го функціонального блока перейти до (і+m)-го функціонального блока, потрібно подати лише m синхроімпульсів, а не подавати після обнуління новий код (і+m), тобто (і+m) синхроімпульсів, з подальшим перетворенням їх у паралельний бінарний код. Таким чином, пристрій для адресації функціональних блоків, що заявляється, відповідає критерію корисної моделі "новизна". Суть корисної моделі, що заявляється, пояснюється кресленнями, де на Фіг. 1 показано блок-схему пристрою для адресації функціональних блоків, що заявляється, на Фіг. 2-3 показано блок-схему варіанту використання вузла переносу (відповідно, першого та другого). Пристрій для адресації функціональних блоків, що заявляється, містить (як варіант конструктивного виконання - див. блок-схему на Фіг. 1) безпосередньо RS-тригери 1, тригери 2 придатності, перший 3 та другий 4 вузли переносу, тактовий вхід 5 RS-тригерів І, вихід 6 вибірки функціональних блоків та канали "К" з'вязку вузлів переносу. При цьому перший 3 вузол переносу розміщено в ланцюзі між Q-виходом (i-1)-го RS-тригера 1 та входом S-входом i-го RS-тригера І, а другий 4 вузол переносу розміщено в ланцюзі між Qвиходом (i-1)-го RS-тригера 1 та входом R-входом i-го RS-тригера 1 (див. блок-схему на Фіг. 1). Зазначене присутнє для всіх функціональних блоків, починаючи з першого (наприклад, «(і-1)») до наступного функціонального блока (і+m), де m>і. Конструктивно перший 3 та другий 4 вузли переносу пристрою для адресації функціональних блоків, що заявляється, містять (як варіант конструктивного виконання) елемент 7 АБО та два елементи 8 ТА (див., відповідно, блок-схеми на Фіг. 2 і 3). Конструктивно і технологічно елементи пристрою для адресації функціональних блоків, що заявляється, з'єднано між собою таким чином (див. блок-схему на Фіг. 1): - перший та другий Q-виходи (i-1)-го RS-тригера з'єднано, відповідно, з входами S та R і-го RS-тригера; - тактові входи RS-тригерів з'єднано і об'єднано у С-вхід кожного RS-тригера кожного з функціональних блоків; - перший Q-вихід кожного RS-тригера І додатково підключено до виходів 6 вибірки функціональних блоків кожного із зазначених функціональних блоків; - перші виходи першого 3 та другого 4 вузлів переносу (i-1)-го RS-тригера 1 з'єднано, відповідно, з S та R входами (i-1)-го RS-тригера І; - Q-виходи (i-1)-го RS-тригеру 1 з'єднано з першими входами першого 3 та другого 4 вузлів переносу відповідно і-го RS-тригера І; - Q-виходи і-го RS-тригера І з'єднано з першими входами першого 3 та другого 4 вузлів переносу відповідно (i-1)-го RS-тригера І; - перші виходи першого 3 та другого 4 вузлів переносу і-го RS-тригера 1 з'єднано, відповідно, з S та R входами і-го RS-тригера І; 2 UA 82286 U 5 10 15 20 25 30 35 40 45 50 55 - другі виходи першого 3 та другого 4 вузлів переносу (i-1)-го RS-тригера 1 з'єднано з другими входами першого 3 та другого 4 вузлів переносу відповідно i-го RS-тригера 1 каналом "К" зв'язку; - другі виходи першого 3 та другого 4 вузлів переносу і-го RS-тригера І з'єднано з другими входами першого 3 та другого 4 вузлів переносу відповідно (i+1)-го RS-тригера 1 каналом "К" зв'язку; - треті входи першого 3 та другого 4 вузлів переносу (i-1)-го RS-тригера 1 з'єднано з виходом (i-1)-го тригера 2 придатності (i-1)-го функціонального блока; - треті входи першого 3 та другого 4 вузлів переносу і-го RS-тригера І з'єднано з виходом і-го тригера 2 придатності і-го функціонального блока; - треті входи першого 3 та другого 4 вузлів переносу (i+1)-го RS-тригера 1 з'єднано з виходом (i+1)-го тригера 2 придатності (i+1)-го функціонального блока; - перший вихід першого 3 вузла переносу (i-1)-го функціонального блока з'єднано з першими входами першого 3 вузла переносу (i+1)-го RS-тригера 1 через S-вхід та Q-вихід, відповідно, (i1)-го та і-го RS-тригера І; - перший вихід другого 4 вузла переносу (i-1)-го функціонального блока з'єднано з першими входами другого 4 вузла переносу (i+1)-го RS-тригера 1 через R-вхід та Q-вихід, відповідно, (i1)-го та і-го RS-тригера І; Безпосередньо в кожному першому 3 та другому 4 вузлах переносу (кожного з функціональних блоків - (i-1)-го, (i)-го та (i+1)-го) їх складові елементи з'єднано між собою таким чином (див, , відповідно, блок-схеми на Фіг. 2 та на Фіг. 3): - перші та другі входи зазначених першого 3 та другого 4 вузлів переносу з'єднано з входом елемента 7 АБО; - вихід зазначеного елемента 7 АБО з'єднано з першими входами елементів 8 ТА; - другий інверсний вхід першого елемента 8 ТА та другий прямий вхід другого елемента 8 ТА з'єднано з третім входом першого 3 та другого 4 вузлів переносу. При цьому виходи першого та другого елементів 8 "ТА" є, відповідно, першим та другим виходами першого 3 та другого 4 вузлів переносу. Пристрій для адресації функціональних блоків, що заявляється, працює таким чином (згідно з блок-схемою на Фіг. 1). Після обнуління усіх розрядів регістра (ланцюги обнуління опущені), відбувається установка в одиничний стан нульового тригера, Q-вихід якого не підключається до входу функціонального блока, а підключається лише до входу першого RS-тригера І через перший вузол переносу 3. Після установки положень тригера 2 придатності, пристрій готовий до роботи у режимі зовнішніх звернень. Для вибірки першого блока із числа невимкнених функціональних блоків, належить подати з Q та Q виходів (i-1)-го першого RS-тригера І синхроімпульси на вхід першого 3 та другого 4 вузлів переносу. Зазначені перший 3 та другий 4 вузли переносу у відповідності з положенням тригерів 2 придатності забезпечують автоматичне обминання тих функціональних блоків, тригери (позиції 1 і 2) яких знаходяться у положенні низького рівня ("непридатний") синхроімпульси проходять по першому 3 та другому 4 вузлам переносу і далі через S та Rвходи відповідно і-го RS-тригера І. Таким чином, ведення вузлів переносу, тригерів вибірки та каналів зв'язку вузлів переносу до складу пристрою для адресації функціональних блоків, що заявляється, дозволить здійснювати обминання непридатних блоків пам'яті у відповідності зі станом тригерів придатності та, крім того, дозволить перейти до наступних блоків пам'яті, чим і досягається розширення функціональних можливостей пристрою. Підвищення ефективності застосування пристрою для адресації функціональних блоків, що заявляється, у порівнянні з прототипом, досягається шляхом ведення до складу зазначеного пристрою вузлів переносу, тригерів вибірки та каналів зв'язку вузлів переносу, робота яких забезпечує виключення з обігу вимкнутих та непридатних функціональних блоків, а вибір наступного, (i+1)-го не вимкнутого функціонального блока буде здійснюватися подачею тільки одного синхроімпульсу. Джерела інформації: 1. Авторське свідоцтво СРСР № 1388877, бюл. № 14, 1988 г. - аналог. 2. Авторське свідоцтво СРСР № 1355977, бюл. № 44, 1987 г. - аналог. 3. Шило В.Л. "Полярные цифровые микросхемы". Справочник. - Μ., 1988. - С. 104. прототип. 3 UA 82286 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 30 35 Пристрій для адресації функціональних блоків, що містить RS-тригери, тактовий вхід пристрою та виходи вибірки функціональних блоків, при цьому перший та другий Q-виходи (i-1)-го RSтригера з'єднано, відповідно, з входами S та R i-го RS-тригера, тактові входи RS-тригерів з'єднано і об'єднано у С-вхід кожного RS-тригера кожного з функціональних блоків, а перший Qвихід кожного RS-тригера додатково підключено до виходів вибірки функціональних блоків кожного із зазначених функціональних блоків, який відрізняється тим, що до складу пристрою додатково введено тригери вибірки, перші та другі вузли переносу по кількості функціональних блоків та канали зв'язку вузлів переносу, перший вузол переносу розміщено в ланцюзі між Qвиходом (і-1)-го RS-тригера та S-входом i-го RS-тригера, а другий вузол переносу розміщено в ланцюзі між Q-виходом (і-1)-го RS-тригера та R-входом i-го RS-тригера, перший та другий вузли переносу містять елемент АБО та два елементи ТА, при цьому перші виходи першого та другого вузлів переносу (і-1)-го RS-тригера з'єднано, відповідно, з S та R входами (і-1)-го RSтригера, Q-виходи (і-1)-го RS-тригера з'єднано з першими входами першого та другого вузлів переносу відповідно i-го RS-тригера, Q-виходи i-го RS-тригера з'єднано з першими входами першого та другого вузлів переносу відповідно (i+1)-го RS-тригера, перші виходи першого та другого вузлів переносу i-го RS-тригера з'єднано, відповідно, з S та R входами i-го RS-тригера, другі виходи першого та другого вузлів переносу (і-1)-го RS-тригера з'єднано з другими входами першого та другого вузлів переносу відповідно i-го RS-тригера каналом зв'язку, другі виходи першого та другого вузлів переносу i-го RS-тригера з'єднано з другими входами першого та другого вузлів переносу відповідно (i+1)-го RS-тригера каналом зв'язку, треті входи першого та другого вузлів переносу (і-1)-го RS-тригера з'єднано з виходом (і-1)-го тригера придатності (і-1)го функціонального блока, треті входи першого та другого вузлів переносу i-го RS-тригера з'єднано з виходом і-го тригера придатності i-го функціонального блока, треті входи першого та другого вузлів переносу (i+1)-го RS-тригера з'єднано з виходом (i+1)-го тригера придатності (i+1)-го функціонального блока, перший вихід першого вузла переносу (i-1)-го функціонального блока з'єднано з першими входами першого вузла переносу (i+l)-го RS-тригера через S-вхід та Q-вихід, відповідно, (i-1)-го та i-го RS-тригера, перший вихід другого вузла переносу (i-1)-го функціонального блока з'єднано з першими входами другого вузла переносу (i+1)-го RS-тригера через R-вхід та Q-вихід, відповідно, (i-1)-го та і-го RS-тригера, причому безпосередньо в кожному першому та другому вузлах переносу перші та другі входи зазначених першого та другого вузлів переносу з'єднано з входом елемента АБО, вихід елемента АБО з'єднано з першими входами елементів ТА, другий інверсний вхід першого елемента ТА та другий прямий вхід другого елемента ТА з'єднано з третім входом першого та другого вузлів переносу, а виходи першого та другого елементів ТА є, відповідно, першим та другим виходами першого та другого вузлів переносу. 4 UA 82286 U 5 UA 82286 U Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for functional block addressing

Автори англійськоюOdnoralov Ihor Vasyliovych, Kozelkova Kateryna Serhiivna, Havrylenko Valerii Volodymyrovych, Shulha Oleksandr Vasyliovych

Назва патенту російськоюУстройство для адресации функциональных блоков

Автори російськоюОдноралов Игорь Васильевич, Козелкова Екатерина Сергеевна, Гавриленко Валерий Владимирович, Шульга Александр Васильевич

МПК / Мітки

МПК: G06F 12/00, G11C 8/00, H04J 3/24, B41L 49/00, B41L 45/00

Мітки: пристрій, блоків, адресації, функціональних

Код посилання

<a href="https://ua.patents.su/8-82286-pristrijj-dlya-adresaci-funkcionalnikh-blokiv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для адресації функціональних блоків</a>

Попередній патент: Універсальний матричний обчислювальний пристрій

Випадковий патент: Пристрій електропривода системи кондиціонування транспортного засобу