Пристрій обробки логічних сигналів

Формула / Реферат

1. Пристрій логічної обробки сигналів, який містить програмовану логічну матрицю FPGA, вузол логіки, вузол діагностики, вузли комунікації, інтерфейс зв'язку, вузол живлення, внутрішній таймер, який відрізняється тим, що пристрій містить вузол індикації, вузол синхронізації єдиного часу, елемент перевірки безперервної роботи FPGA, інтерфейс синхронізації з іншими пристроями логічної обробки сигналів, дубльовані незалежні канали прямої передачі діагностичної інформації, дубльовані незалежні канали прямої передачі реєстраційної інформації, інтерфейс зв'язку містить швидкодіючі шини LVDS, множину незалежних гальванічно розділених вузлів LVDS приймання/передачі, множину незалежних вузлів оптичних приймання-передачі, множину незалежних вузлів приймання/передачі промислової мережі Ethernet, множину незалежних вхідних вузлів приймання дискретних сигналів, множину незалежних вихідних вузлів дискретних сигналів, незалежний вузол зв'язку з переносним персональним комп'ютером, при цьому кожен з вузлів інтерфейсу містить щонайменше один цифровий канал зв'язку з FPGA, вузол логіки містить щонайменше один цифровий канал зв'язку з вузлами діагностики і комунікації, вузол діагностики містить щонайменше один цифровий канал зв'язку з вузлом комунікації, вузлом індикації і вузлом синхронізації єдиного часу, FPGA з'єднана з елементом перевірки безперервної роботи FPGA і вузлом живлення.

2. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що вузол логіки, вузол діагностики, вузол комунікації і вузол індикації реалізовані в FPGA.

3. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що вузол логіки реалізований в одній FPGA, вузол діагностики, вузол комунікації і вузол індикації реалізовані в іншій FPGA.

4. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що інтерфейс синхронізації з іншими пристроями обробки логічних сигналів використовує шину RadICS.

5. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що LVDS використовує індивідуальні лінії цифрового зв'язку "точка-точка".

6. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що вузол індикації містить вузол відображення внутрішнього стану пристрою і кодів помилок і вузол керування параметрами відображення від кнопок на лицьовій панелі.

7. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що містить механічні штифти кодування типів модулів.

Текст

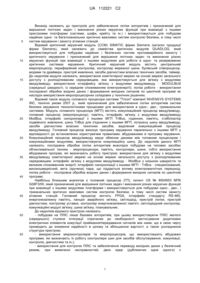

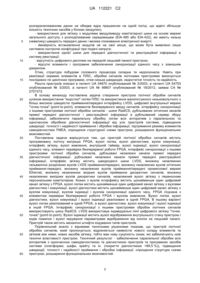

Реферат: Винахід належить до пристроїв для забезпечення логіки алгоритмів і призначений для вирішення логічних задач і виконання різних керуючих функцій при взаємодії з іншими пристроями платформи (системи, шафи, крейту та ін.) і використовується для побудови надійних одно- та багатоканальних критично важливих систем контролю безпеки, в тому числі систем керування і захисту атомних станцій. Пристрій логічної обробки сигналів містить множину незалежних вузлів 1 LVDS послідовного приймання/передачі даних, множину незалежних швидкодіючих вузлів 2 оптичних приймання-передачі, множину незалежних швидкодіючих вузлів 3 приймання/передачі промислової мережі Ethernet, незалежний вузол 4 зв'язку з переносним (бортовим) персональним комп'ютером RS-232, множину незалежних швидкодіючих вузлів 5 приймання дискретних сигналів, вузол 6 синхронізації єдиного часу зовнішнього джерела, FPGA 7, вузол 8 логіки, вузол 9 діагностики, вузол 10 індикації, вузол 11 комунікації, елемент 12 безперервної роботи FPGA, множину незалежних швидкодіючих вузлів 13 передавання дискретних сигналів, вузол 14 живлення. Вузол 10 індикації містить вузол 15 відображення внутрішнього стану блоків і кодів помилок та вузол 16 керування параметрами відображення. Технічний результат полягає у забезпеченні паралельної обробки всіх алгоритмів з одночасною самодіагностикою та діагностикою пристроїв та програмних засобів системи (платформи, шафи, крейту та ін. (покриття діагностикою >99,5 %)), підвищенні швидкодії, точності і надійності приймання і обробки інформації, спрощенні структури схеми пристрою, розширенні функціональних можливостей. UA 112221 C2 (12) UA 112221 C2 UA 112221 C2 5 10 15 20 25 30 35 40 45 50 55 Винахід належить до пристроїв для забезпечення логіки алгоритмів і призначений для вирішення логічних задач і виконання різних керуючих функцій при взаємодії з іншими пристроями платформи (системи, шафи, крейту та ін.) і використовується для побудови надійних одно- та багатоканальних критично важливих систем контролю безпеки, в тому числі систем керування і захисту атомних станцій. Відомий критичний керуючий модуль (ССМ) SIMATIC фірми Siemens (каталог продукції фірми Siemens), який належить до сімейства критичних модулів QUADLOG, який використовується для побудови надійних і безпечних систем протиаварійного захисту і критичного керування і призначений для вирішення логічних задач та виконання різних керуючих функцій при взаємодії з іншими модулями для роботи в одно- та резервованих критичних системах керування. Критичний керуючий модуль містить центральний мікропроцесор, периферійний контролер, контролер мережної шини, булівській співпроцесор, модеми та драйвери, пристрій живлення, засоби діагностики власних технічних засобів, таймер. До недоліків модуля належать: використання комп'ютерної мережі на основі мережі загального доступу з розподілюваним середовищем, яка використовується для зв'язку з модулями вводу/виводу; використання інтерфейсу зв'язку з модулями вводу/виводу - MODULBUS (середньої швидкості, із середнім споживанням електроенергії); логіка роботи - використання послідовної обробки вхідних даних і формування вихідних сигналів по циклічній програмі як наслідок використання мікропроцесорних складових у технічних рішеннях. Відомий також модуль головного процесора системи "Tricon" компанії INVENSYS SYSTEMS INC, технічні умови 2007 p., який призначений для забезпечення логіки алгоритмів систем безпеки керування технологічними процесами для використання в одно-, дво-, триканальних системах. Модуль головного процесора (МГП) містить комунікаційний процесор вводу/виводу, головний процесор (мікропроцесор), пам'ять, інтерфейс зв'язку з модулями вводу/виводу ModBus, інтерфейс синхронізації з іншими МГП TriBus, годинник, пам'ять, стабілізатор подвійного живлення, шину TriBus для з'єднання з іншими МГП, потроєну шину вводу/виводу, засоби діагностики власних технічних засобів, виділений комунікаційний процесор вводу/виводу. Головний процесор виконує програму керування паралельно з іншими МГП у відповідності до встановлених користувачем правилами, вбудованими в програму керування. Комунікаційний процесор вводу/виводу керує обміном даними між головним процесором і комунікаційними модулями, використовуючи комунікаційну шину. До недоліків даного МГП належать: послідовна обробка логіки алгоритмів внаслідок побудови на типових засобах обчислювальної техніки - мікропроцесори, пам'ять, контролери, шини, тобто використання вбудованих програм, які визначають роботу пристрою; використання для зв'язку з модулями вводу/виводу комп'ютерної мережі на основі мережі загального доступу з розподілюваним середовищем; інтерфейс зв'язку з модулями вводу/виводу - ModBus з низькою швидкістю та великим споживанням енергії; інтерфейс синхронізації з іншими МГП - TriBus - спеціалізований, високошвидкісний, вита (кручена) пара, що піддається впливу електромагнітних перешкод; логіка роботи - послідовна обробка вхідних даних і формування вихідних сигналів по циклічній програмі. Найбільш близьким аналогом є головний процесор (ГП), патент US № 8554953 МПК G06F3/00, який призначений для вирішення логічних задач і виконання різних керуючих функцій при взаємодії з іншими модулями платформи і використовується для побудови одно-, дво-, і триканальних критично важливих систем контролю безпеки, в тому числі систем захисту атомних станцій. Головний процесор містить FPGA, інтерфейс стандарту RS-485, енергонезалежну пам'ять, ланцюг аварійного зв'язку, світлодіод, пристрій логіки, пристрій діагностики, контролер уставок, контролер енергонезалежної пам'яті, світлодіодний контролер, комунікаційні модулі зв'язку, шина зв'язку, планувальник. До недоліків відомого пристрою належать: - побудова на ПЛІС лише базових алгоритмів, при цьому використовуючи ПЛІС малого (середнього) ступеня інтеграції спричиняє до необхідності застосування додаткових електричних елементів комутації приймання/передавання сигналів між ними, що в свою чергу призводить до зниження надійності в цілому та збільшенню вартості, а також ускладнення структури пристрою; - використання мікроконтролерів та мікропроцесорів, що використовують вбудовані програми, які визначають їх роботу (контролери шин для засобів обслуговування, комунікації, контролю, діагностики та ін.); - використання для контролю ПЛІС та забезпечення переводу вихідних даних у безпечний режим, при виявленні несправностей, двох ядер (дублюючих одне одного) з 1 UA 112221 C2 5 10 15 20 25 30 35 40 45 50 55 60 розпаралелюванням даних на обидва ядра працюючих на одній логіці, що вдвічі збільшує кількість технічних засобів у блоках (модулях); - використання для зв'язку з модулями вводу/виводу комп'ютерної шини на основі мережі загального доступу з розподілюваним середовищем (ЕІА-485 або ЕІА-422), які мають низьку (невелику) швидкість передачі даних і велике споживання електричної енергії; - ймовірність встановлення модулів не на свої місця, що може бути виявлено лише системою контролю конфігурації при подачі напруги; - використання однієї шини для передачі діагностичної та реєстраційної інформації в систему реєстрації; - відсутність цифрового дисплею на передній лицьовій панелі пристрою; - відсутні елементи і програмне забезпечення синхронізації єдиного часу з зовнішнім джерелом. Отже, структура побудови головного процесора складна та недосконала. Навіть при реалізації окремих елементів в ПЛІС, обробка сигналів логічними пристроями виконується послідовно по циклічних програмах, отже низька швидкодія, недостатня точність та надійність. Решта пристроїв описані в патенті UA 54870 опублікований № 3/2003, в патенті UA 54753 опублікований № 3/2003, в патенті UA № 99807 опублікований № 18/2012, заявка СА № 2707373. В основу винаходу поставлена задача створення пристрою логічної обробки сигналів шляхом використання "жорсткої" логіки ПЛІС та використання малопотужного низьковольтного з більш високою швидкістю приймання/передачі інтерфейсу LVDS, цифрової внутрішньої мережі "точка-точка" (point-to-point), елементів безперервного вводу сигналів, інтерфейсу синхронізації з іншими пристроями логічної обробки сигналів - шини RadІCS, дубльованих оптичних каналів прямої передачі діагностичної і реєстраційної інформації в дубльований сервер збору інформації, забезпечити паралельну обробку логіки всіх алгоритмів з паралельною та одночасною обробкою діагностичної інформації від усіх пристроїв системи, підвищення швидкодії, точності і надійності приймання і обробки інформації, підтримання режиму елементів самодіагностики FMEA, спрощення структурної схеми пристрою, розширення функціональних можливостей. Поставлена задача вирішується тим, що пристрій логічної обробки сигналів містить програмовану логічну матрицю FPGA, вузол логіки, вузол діагностики, вузли комунікації, інтерфейс зв'язку, вузол живлення, внутрішній таймер, вузол індикації, вузол синхронізації єдиного часу, елемент перевірки безперервної роботи FPGA, інтерфейс синхронізації з іншими пристроями логічної обробки сигналів, дубльовані незалежні канали прямої передачі діагностичної інформації, дубльовані незалежні канали прямої передачі реєстраційної інформації, інтерфейс зв'язку містить швидкодіючі шини LVDS, множину незалежних гальванічно розділених вузлів LVDS приймання/передачі, множину незалежних вузлів оптичних приймання-передачі, множину незалежних вузлів приймання/передачі промислової мережі Ethernet, множину незалежних вхідних вузлів приймання дискретних сигналів, множину незалежних вихідних вузлів дискретних сигналів, незалежний вузол зв'язку з переносним персональним комп'ютером. Кожен з вузлів інтерфейсу містить щонайменше один цифровий канал зв'язку з FPGA, вузол логіки містить щонайменше один цифровий канал зв'язку з вузлами діагностики і комунікації, вузол діагностики містить щонайменше один цифровий канал зв'язку з вузлом комунікації, вузлом індикації і вузлом синхронізації єдиного часу, FPGA з'єднана з елементом перевірки безперервної роботи FPGA і вузлом живлення. Вузол логіки, вузол діагностики, вузол комунікації і вузол індикації реалізовані в одній FPGA. В іншому варіанті вузол логіки реалізований в одній FPGA, а вузол діагностики, вузол комунікації і вузол індикації в іншій FPGA. Інтерфейс синхронізації з іншими пристроями обробки логічних сигналів використовують шину RadІCS. LVDS використовує індивідуальні лінії цифрового зв'язку "точкаточка" (point-to-point). Вузол індикації містить вузол відображення внутрішнього стану пристрою і кодів помилок і вузол керування параметрами відображення від кнопок на лицьовій панелі. Пристрій також містить механічні штифти кодування типів пристроїв. Порівняльний аналіз з відомими технічними рішеннями показав, що пристрій логічної обробки сигналів, який пропонується, відрізняється наявністю нового складу елементів та зв'язків між ними, нових засобів зв'язку, тобто має нову сукупність ознак, які забезпечують нові технічні властивості пристрою. Технічний результат - забезпечення паралельної обробки всіх алгоритмів з одночасною самодіагностикою та діагностикою пристроїв та програмних засобів системи (платформи, шафи, крейту та ін. (покриття діагностикою >99,5 %)), підвищення швидкодії, точності і надійності приймання і обробки інформації, спрощення структури схеми пристрою, розширення функціональних можливостей. 2 UA 112221 C2 5 10 15 20 25 30 35 40 45 50 55 Реалізація вузлів логіки, діагностики, комунікації та індикації в FPGA дозволяє значно підвищити точність обробки сигналів і швидкодію та одночасно спростити структуру пристрою, тобто підвищити надійність пристрою в цілому та розширити функціональні можливості, зокрема виконувати діагностику всіх пристроїв і програмного забезпечення системи (платформи, шафи, крейту та ін.) Реалізація алгоритмів в FPGA, яка дозволяє в своїй структурі "жорстко" зафіксувати необхідні елементи схемотехніки для одночасної і паралельної обробки всіх необхідних алгоритмів та діагностичної інформації за один цикл роботи та на декілька порядків швидше виконувати будь-які алгоритми з одночасним виконанням самодіагностики пристрою та за необхідності діагностики інших пристроїв і програмного забезпечення всієї системи (платформи, шафи, крейду та ін.). Отже, в FPGA для кожного із закладених алгоритмів, враховуючи діагностику всієї системи, існують свої окремі технічні засоби. В той час, коли в мікроконтролері (мікропроцесорі) всі алгоритми повинні послідовно пройти через один і той же апаратний засіб, а діагностику всієї системи виконує пристрій діагностики. Відсутність збоїв та "зависань" роботи FPGA забезпечується елементом перевірки безперервної роботи FPGA, який при перевищенні тайм-ауту виконує перезавантаження FPGA. Використання множини незалежних гальванічно розділених один від одного та інших ланцюгів і елементів пристрою вузлів LVDS послідовного приймання/передачі даних та швидкодіючого малопотужного низьковольтного інтерфейсу LVDS, а також внутрішньої мережі "точка-точка" забезпечує індивідуальний зв'язок пристрою з іншими пристроями системи (платформи, шафи, крейту та ін.), тобто повна відсутність впливу пристроїв один на одного. Використання вузла синхронізації єдиного часу дозволяє забезпечити синхронний хід внутрішнього таймера пристрою з сигналами єдиного часу які надходять від зовнішнього джерела єдиного часу. Використання в якості інтерфейсу синхронізації з іншими пристроями обробки логічних сигналів спеціалізованої швидкодіючої з оптичними каналами "точка-точка" (point-to-point) шини RadІCS забезпечує гарантовану доставку інформації за мінімальний час, перевірку цілісності пакетів даних, корекцію помилок (протокол з гарантованою доставкою даних). Використання дубльованих оптичних каналів прямої передачі діагностичної інформації і дубльованих оптичних каналів прямої передачі реєстраційної інформації в дубльований сервер збору інформації дає можливість пристрою одночасно виконувати основні логічні функції і функції діагностики системи. Діагностичні технічні і програмні засоби підтримують режим самодіагностики FMEA (діагностичне покриття - 99,5 % технічних і програмних засобів пристрою). Наявність інформаційного дисплею на передній лицьовій панелі дає можливість для оперативного відображення стану внутрішньої логіки, сформованих команд, а також кодів несправностей кожного пристрою. Використання механічних штифтів кодування типів пристроїв забезпечує їх встановлення на відповідне місце. Пристрій відповідає вимогам SIL3 по стандарту IES 61508 в одноканальній системі, підтримує роботу дво -, три - і чотириканальних керуючих систем безпеки. Суть винаходу пояснюють креслення. На фіг. 1 зображена структурна схему пристрою логічної обробки сигналів з однією FPGA; На фіг. 2 - структурна схема пристрою логічної обробки сигналів з двома FPGA. Пристрій містить множину незалежних вузлів 1 LVDS послідовного приймання/передачі даних, множину незалежних швидкодіючих вузлів 2 оптичних приймання-передачі, множину незалежних швидкодіючих вузлів 3 приймання/передачі промислової мережі Ethernet, незалежний вузол 4 зв'язку з переносним (бортовим) персональним комп'ютером RS-232, множину незалежних швидкодіючих вузлів 5 приймання дискретних сигналів, вузол 6 синхронізації єдиного часу зовнішнього джерела, FPGA 7, вузол 8 логіки, вузол 9 діагностики, вузол 10 індикації, вузол 11 комунікації, елемент 12 безперервної роботи FPGA, множину незалежних швидкодіючих вузлів 13 передавання дискретних сигналів, вузол 14 живлення. Вузол 10 індикації містить вузол 15 відображення внутрішнього стану блоків і кодів помилок та вузол 16 керування параметрами відображення. Незалежні вузли 1 LVDS послідовного приймання/передачі даних гальванічно розділені один від одного та інших ланцюгів і елементів пристрою приймають/передають пакети даних по швидкодіючій шині LVDS від/в інших пристроїв кожного окремого шасі (крейту) системи (платформи, шафи та ін.) для подальшої обробки. Незалежні вузли 1 LVDS послідовного приймання/передачі даних забезпечують зв'язок логічного пристрою з: 3 UA 112221 C2 5 10 15 20 25 30 35 40 45 50 55 60 - пристроями вводу вхідних сигналів кожного окремого шасі (крейту) системи (платформи та ін.) для отримання пакетів вхідної інформації; - пристроями передачі вихідних сигналів кожного окремого шасі (крейту), системи (платформи та ін.) для передачі пакетів вихідної інформації; - пристроями оптичного зв'язку для розширення кожного окремого шасі (крейту). Незалежні швидкодіючі вузли 2 оптичних приймання-передачі гальванічно розділені один від одного та інших ланцюгів і елементів пристрою. Кожен з вузлів 2 оптичних приймання-передачі з'єднаний з пристроєм 11 комунікації і має оптичний рознімач на лицьовій панелі пристрою для оперативного підключення/відключення зовнішніх оптичних ліній зв'язку. Незалежні швидкодіючі вузли 2 оптичних приймання-передачі забезпечують зв'язок пристрою: - з метою синхронізації з іншими пристроями логічної обробки сигналів системи (платформи, шафи та ін.) при побудові дво-, три- та чотириканальних систем; - з іншими пристроями логічної обробки сигналів у віддалених шафах (крейтах та ін.) розподіленої системи (в тому числі багатоканальної). Незалежні швидкодіючі вузли 3 приймання/передачі промислової мережі Ethernet гальванічно розділені один від одного та інших ланцюгів і елементів пристрою. Кожен з вузлів 3 з'єднаний з пристроєм 11 комунікації і має рознімач оптичної мережі Ethernet на лицьовій панелі пристрою для оперативного підключення зовнішніх ліній зв'язку. Незалежні швидкодіючі вузли 3 приймання/передачі забезпечують зв'язок пристрою: - з комп'ютерною системою (оптичними кросами) збору реєстраційної та діагностичної інформації з метою архівування і відображення. Незалежний вузол 4 зв'язку з переносним (бортовим) персональним комп'ютером RS-232 гальванічно розділений від інших елементів пристрою. Незалежні швидкодіючі вузли 5 приймання дискретних сигналів гальванічно розділені один від одного та інших ланцюгів і елементів пристрою. Кожен з яких містить два індивідуальних джерела струму, швидкодіючий мультиплексор, пристрій дискретного вводу гальванічного розділення і передачі цифрових сигналів в вузол логіки. Вузли 5 приймання дискретних сигналів забезпечують можливість пристрою: - ідентифікувати власне місцезнаходження в системі (платформі, шафі та ін.) по перемичкам на відповідній стороні рознімача, які кодують його ІР-адресу; - забезпечити незалежний від шини LVDS канал приймання дискретних даних для керування режимами роботи пристрою. Вузол 6 синхронізації єдиного часу забезпечує синхронний хід внутрішнього таймеру пристрою з сигналами єдиного часу які надходять із: - мережі єдиного часу (наприклад, енергоблока); - GPRS - приймача супутникових сигналів єдиного часу. Елемент 12 безперервної роботи FPGA виконує перезавантаження FPGA при перевищенні тайм-ауту. Вузол 8 логіки забезпечує: - прийом від вузла 11 комунікації вхідних даних про технологічні параметри об'єкта керування, які надходять від пристроїв входів та сигнали про стан виконавчих механізмів об'єкта від пристроїв керування виконавчими механізмами; - обробку прийнятих сигналів у відповідності до алгоритмів захисту блокувань і функціонування об'єкта; - формування керуючих інформаційних пакетів та передачу їх у вузол 11 комунікації для подальшої передачі на вихідні пристрої для впливу на виконавчі механізми; - формування швидкодіючих ініціативних (ініціюючих) сигналів для запуску систем захисту за допомогою вузлів 13 передавання дискретних сигналів; - ідентифікацію місця знаходження пристрою в системі (платформі, шафі та ін.) та діагностичній та реєстраційній мережах при побудові багатоканальних розподільних систем; - прямий прийом дискретних сигналів з метою керування режимами роботи пристрою. Цикл виконання усіх завдань пристроєм встановлюється на етапі робочого проекту в межах від 1 до 10 мс. Вузол 11 комунікації кожні 10 мс по сигналах від вузла 8 логіки приймає і передає в послідовному коді пакети цифрових даних через вузли гальванічної приймання-передачі до/від оптичних, LVDS, Ethernet приймання-передачі. Вузол 9 діагностики по однонаправлених лініях передає отриману від вбудованих технічних засобів діагностики інформацію про стан кожного з вузлів пристрою. Множина незалежних швидкодіючих вузлів 13 передавання дискретних сигналів гальванічно розділені один від одного і від інших елементів пристрою і кожен з яких містить: 4 UA 112221 C2 5 10 15 20 25 30 35 40 45 - елементи керування станом і контролю стану твердотілого реле; - твердотіле реле, контакти якого є вихідними елементами. Пристрій виконує функції. - приймання сигналів від пристроїв збору вхідної інформації про технологічні параметри об'єкта керування; - приймання сигналів стану виконавчих механізмів об'єкта від пристрою функціонального керування виконавчими механізмами; - обробка прийнятих сигналів у відповідності до алгоритмів захисту блокувань і функціонування об'єкта; - формування керуючих інформаційних пакетів для вихідних блоків з метою дії на виконавчі механізми об'єкта; - формування швидкодіючих ініціативних керуючих дискретних сигналів для запуску системи захисту; - виконання функцій безперервної діагностики власних технічних засобів і програмного забезпечення; - виконання функцій безперервної діагностики технічних засобів і програмного забезпечення системи (платформи, шафи та ін.); - синхронізація внутрішнього годинника пристрою з сигналами єдиного часу від зовнішнього джерела. Пристрій працює наступним чином. Пристрій виконаний в двох модифікаціях: - вузли логіки, діагностики, комунікації і індикації реалізовані в єдиній (загальній) FPGA, розділення і незалежність яких забезпечується засобами розробки проекту; - вузол логіки реалізований в одній FPGA, а вузли діагностики, комунікації і індикації в іншій FPGA. В кожному циклі виконання задач (кожні 1-10 мс) пристрій приймає вхідні сигнали, які надходять від усіх джерел, обробляє їх у відповідності до закладених алгоритмів, формує і передає вихідні ініціюючі (ініціативні) сигнали для усіх приймачів у відповідності до проекту; приймає сигнали керування режимами роботи і виконує відповідні переключення внутрішньої структури; виконує функції безперервної діагностики власних технічних засобів і програмного забезпечення; забезпечує синхронізацію внутрішнього таймеру пристрою з сигналами єдиного часу. Діагностична інформація про стан всіх внутрішніх елементів пристрою надходить у вузол діагностики. Вузол діагностики упаковує діагностичні дані отримані від всіх вбудованих в пристрій елементів діагностики в стандартні пакети. Пакети даних по дубльованих оптичних каналах передачі діагностичної інформації від усіх пристроїв системи (платформи, шафи та ін.) передаються в сервер збору інформації. По дубльованих оптичних каналах прямої передачі реєстраційна інформація передається в сервер збору інформації. В процесі роботи пристрою на цифрових індикаторах на лицьовій панелі безперервно відображається внутрішній стан пристрою (справність або код помилки, яка виникла у випадку несправності). Кнопками керування відображенням на індикатори можна визвати більш докладну інформацію, що дозволить встановити несправність не вдаючись до послуг розширеної діагностики робочого стану на моніторах відображення системи реєстрації. Додатково два світлодіодні індикатори відображають стан "Робота" або "Несправність". Цикл роботи пристрою встановлюється на стадії проектування системи (платформи, шафи та ін.) в межах від 1 до 10 мс, що гарантує швидкодію роботи пристрою від 100 до 1000 циклів за секунду. ФОРМУЛА ВИНАХОДУ 50 55 60 1. Пристрій логічної обробки сигналів, який містить програмовану логічну матрицю FPGA, вузол логіки, вузол діагностики, вузли комунікації, інтерфейс зв'язку, вузол живлення, внутрішній таймер, який відрізняється тим, що пристрій містить вузол індикації, вузол синхронізації єдиного часу, елемент перевірки безперервної роботи FPGA, інтерфейс синхронізації з іншими пристроями логічної обробки сигналів, дубльовані незалежні канали прямої передачі діагностичної інформації, дубльовані незалежні канали прямої передачі реєстраційної інформації, інтерфейс зв'язку містить швидкодіючі шини LVDS, множину незалежних гальванічно розділених вузлів LVDS приймання/передачі, множину незалежних вузлів оптичних приймання-передачі, множину незалежних вузлів приймання/передачі промислової мережі Ethernet, множину незалежних вхідних вузлів приймання дискретних сигналів, множину 5 UA 112221 C2 5 10 15 20 незалежних вихідних вузлів дискретних сигналів, незалежний вузол зв'язку з переносним персональним комп'ютером, при цьому кожен з вузлів інтерфейсу містить щонайменше один цифровий канал зв'язку з FPGA, вузол логіки містить щонайменше один цифровий канал зв'язку з вузлами діагностики і комунікації, вузол діагностики містить щонайменше один цифровий канал зв'язку з вузлом комунікації, вузлом індикації і вузлом синхронізації єдиного часу, FPGA з'єднана з елементом перевірки безперервної роботи FPGA і вузлом живлення. 2. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що вузол логіки, вузол діагностики, вузол комунікації і вузол індикації реалізовані в FPGA. 3. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що вузол логіки реалізований в одній FPGA, вузол діагностики, вузол комунікації і вузол індикації реалізовані в іншій FPGA. 4. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що інтерфейс синхронізації з іншими пристроями обробки логічних сигналів використовує шину RadICS. 5. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що LVDS використовує індивідуальні лінії цифрового зв'язку "точка-точка". 6. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що вузол індикації містить вузол відображення внутрішнього стану пристрою і кодів помилок і вузол керування параметрами відображення від кнопок на лицьовій панелі. 7. Пристрій логічної обробки сигналів за п. 1, який відрізняється тим, що містить механічні штифти кодування типів модулів. 6 UA 112221 C2 7 UA 112221 C2 Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

Автори англійськоюBakhmach Yevhenii Stepanovych

Автори російськоюБахмач Евгений Степанович

МПК / Мітки

МПК: G06F 3/00

Мітки: сигналів, обробки, пристрій, логічних

Код посилання

<a href="https://ua.patents.su/10-112221-pristrijj-obrobki-logichnikh-signaliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій обробки логічних сигналів</a>

Попередній патент: Композиція інгредієнтів для приготування кондитерських виробів “prana sweets”

Наступний патент: Спосіб аналізу випаровувань палива у повітрі автозаправних станцій

Випадковий патент: Соус-майонез "aurora"