Пристрій для передачі та прийому інформації

Формула / Реферат

Устройство для передачи и приема информации, содержащее на передающей стороне генератор тактовых импульсов, выход которого соединен с тактовыми входами компаратора и дельта-модулятора, информационный вход дельта-модулятора объединен с первым информационным входом компаратора и является информационным входом устройства, на приемной стороне - селектора импульсов, вход которого подключен к каналу связи, первый, второй и третий выходы селектора импульсов соединены соответственно с тактовым, первым и вторым управляющими входами реверсивного счетчика, отличающееся тем, что, с целью повышения быстродействия устройства, в него на передающей стороне введены формирователь импульсов, генератор пилообразного напряжения и делитель частоты, выходы дельта-модулятора соединены соответственно с информационным и первым управляющим входами формирователя импульсов, выход формирователя импульсов соединен с каналом связи, вход делителя частоты подключен к выходу генератора тактовых импульсов, выход делителя частоты соединен с вторым управляющим входом формирователя импульсов и первым входом генератора пилообразного напряжения, второй вход и выход которого подключены соответственно к выходу и второму информационному входу компаратора, генератор тактовых импульсов, элемента задержки, элементы ЗАПРЕТ, блок ключей, триггер, элемент ИЛИ, блок цикловой синхронизации и счетчик, четвертый выход селектора импульсов соединен непосредственно с первым входом первого элемента ЗАПРЕТ и через первый элемент задержки - с первым входом элемента ИЛИ, второй вход которого является установочным входом устройства, выход элемента ИЛИ соединен с первым входом триггера и входом сброс счетчика, выходы счетчика соединены с одноименными информационными входами блока ключей, выходы которого соединены с одноименными информационными входами реверсивного счетчика, пятый выход селектора импульсов соединен с первым входом блока цикловой синхронизации, выход которого соединен непосредственно с третьим входом элемента ИЛИ и через второй элемент задержки - с вторым входом триггера, выход триггера соединен с инверсным входами первого и второго элементов ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с управляющим входом блока ключей, вход генератора тактовых импульсов подключен к первому выходу селектора импульсов, выход генератора тактовых импульсов соединен с вторым входом блока цикловой синхронизации и прямым входом второго элемента ЗАПРЕТ, выход которого соединен с счетным входом счетчика.

Текст

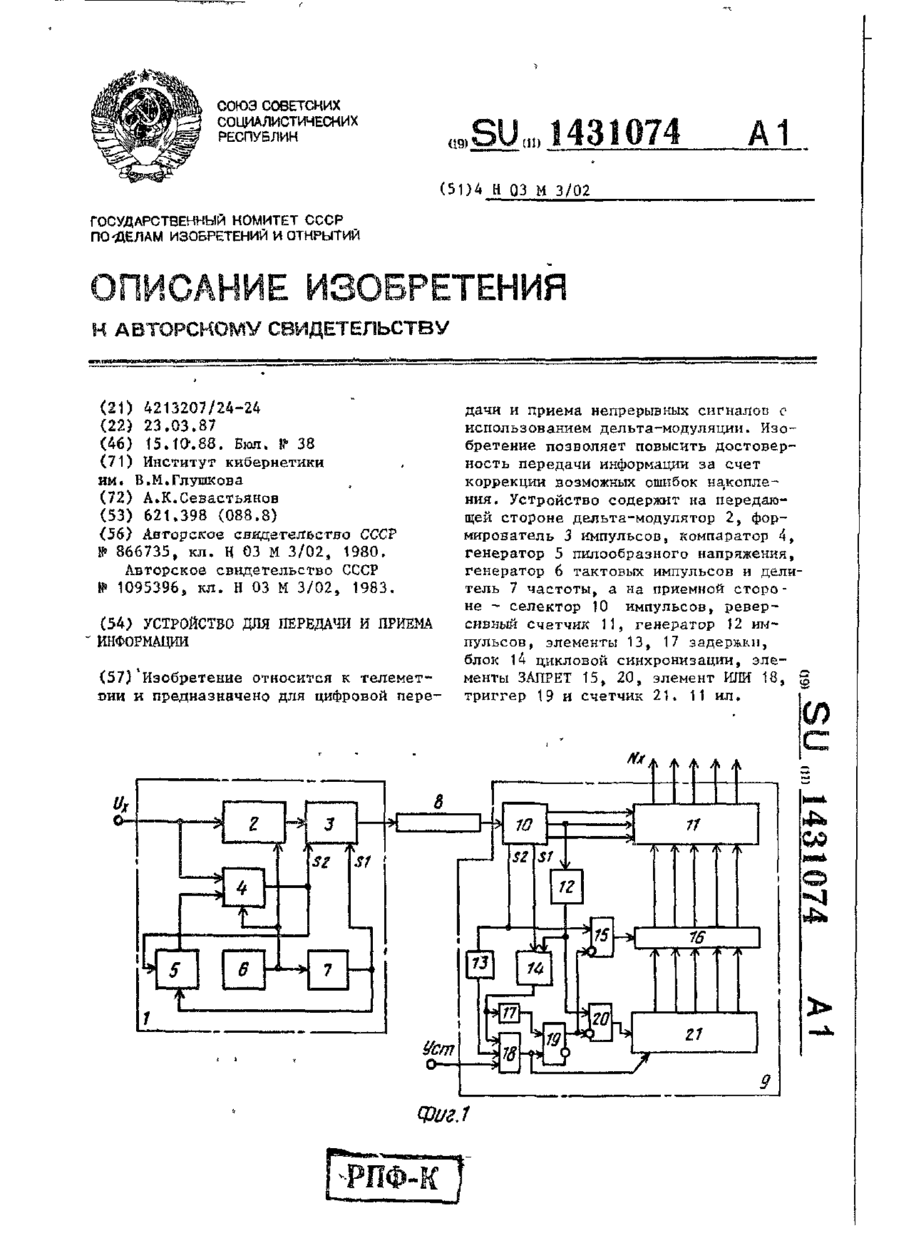

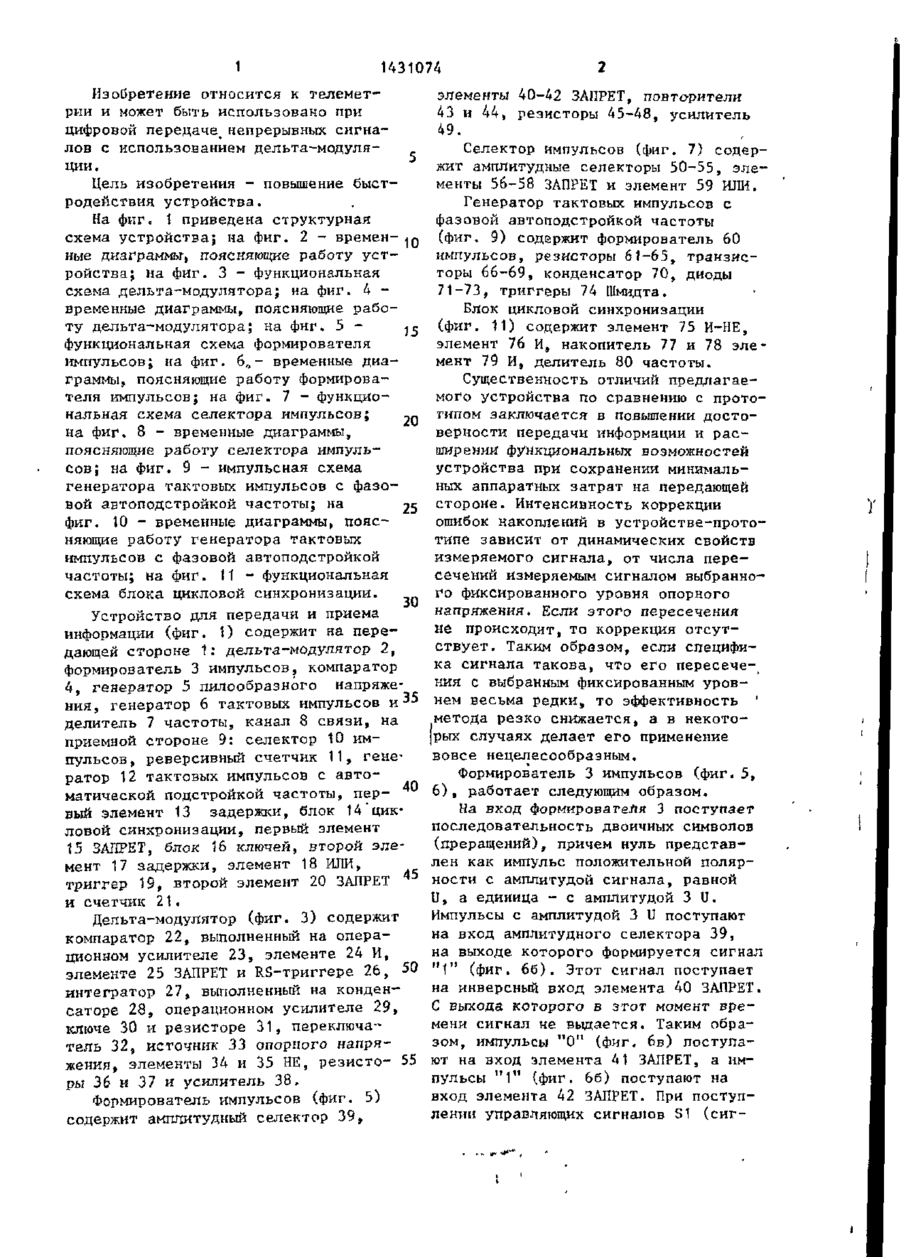

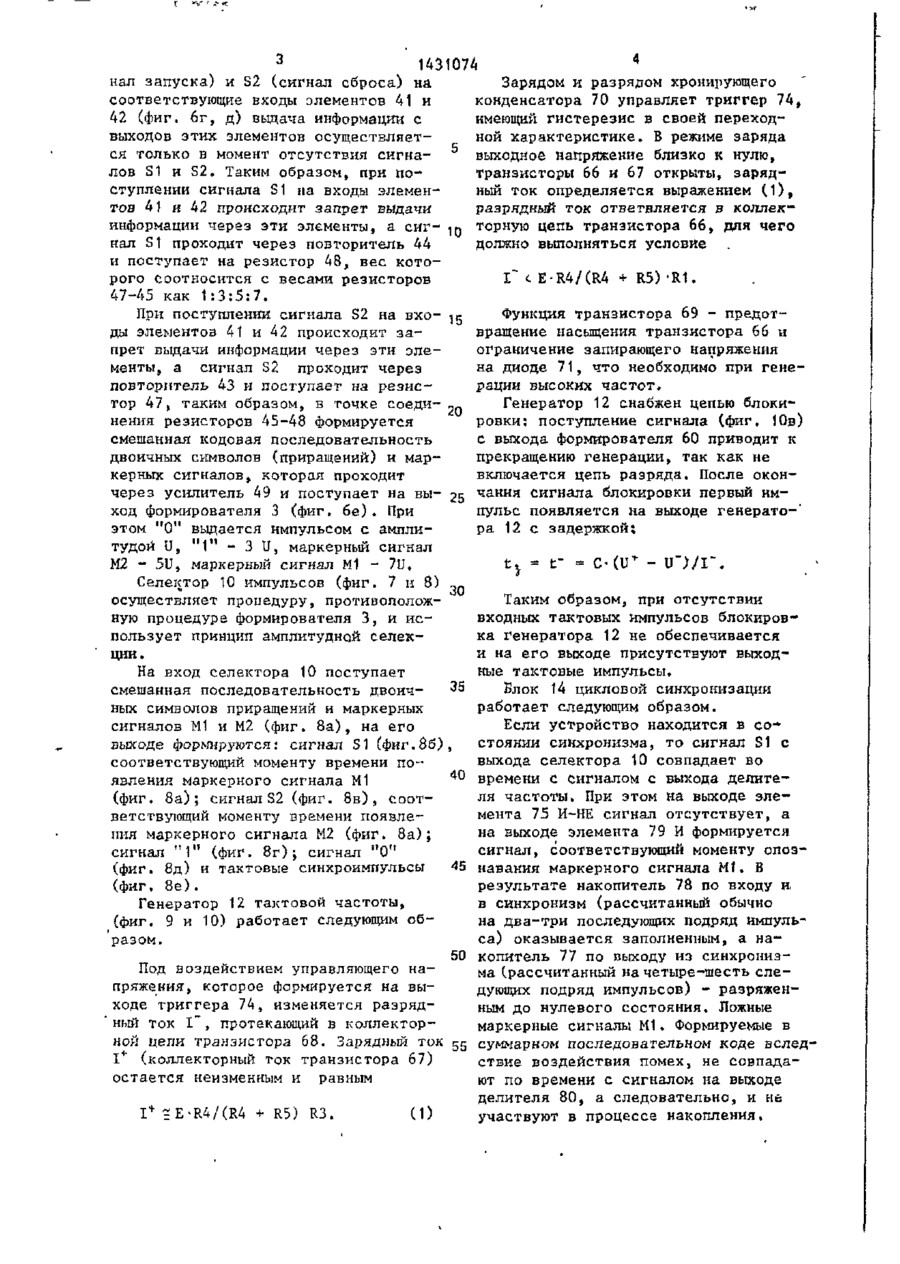

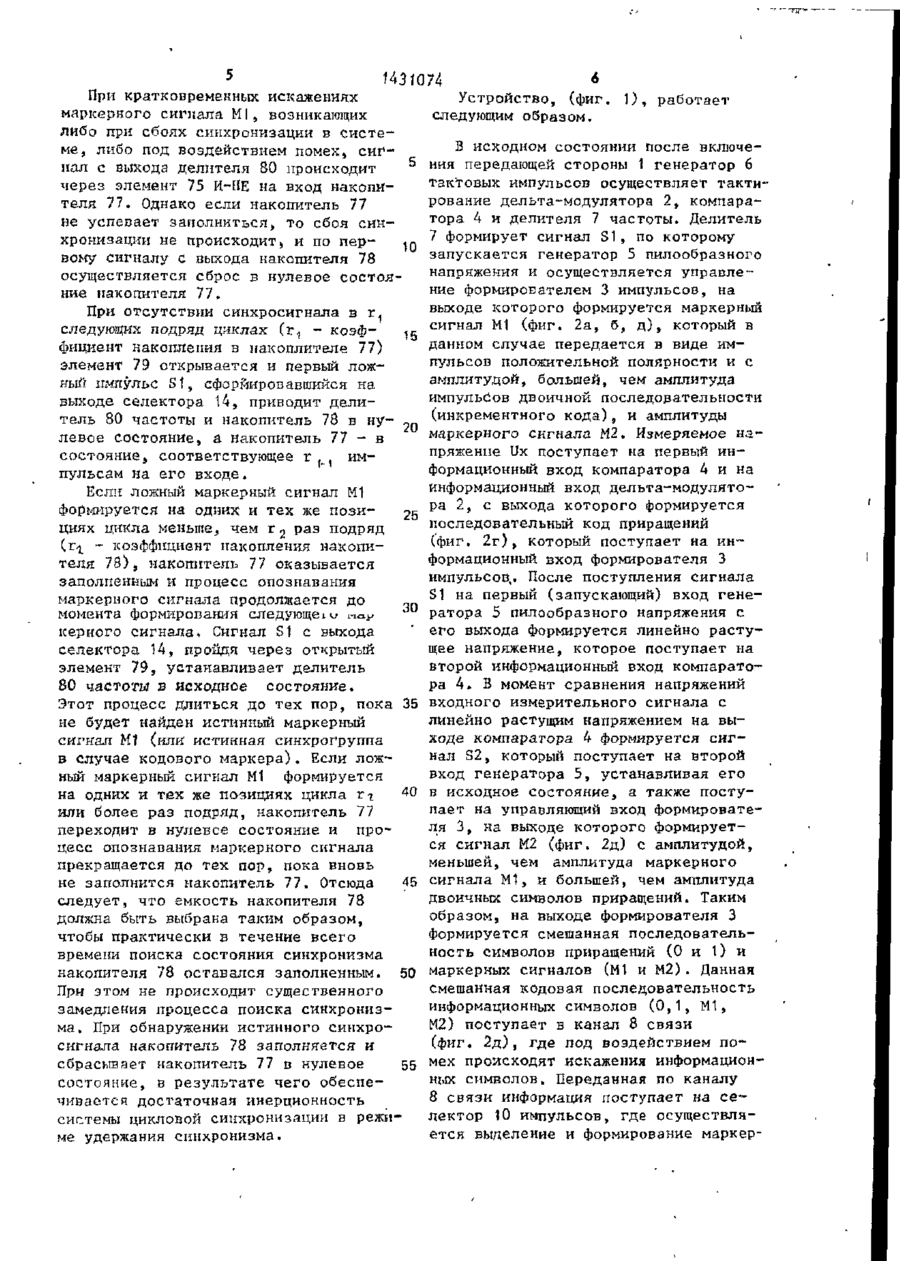

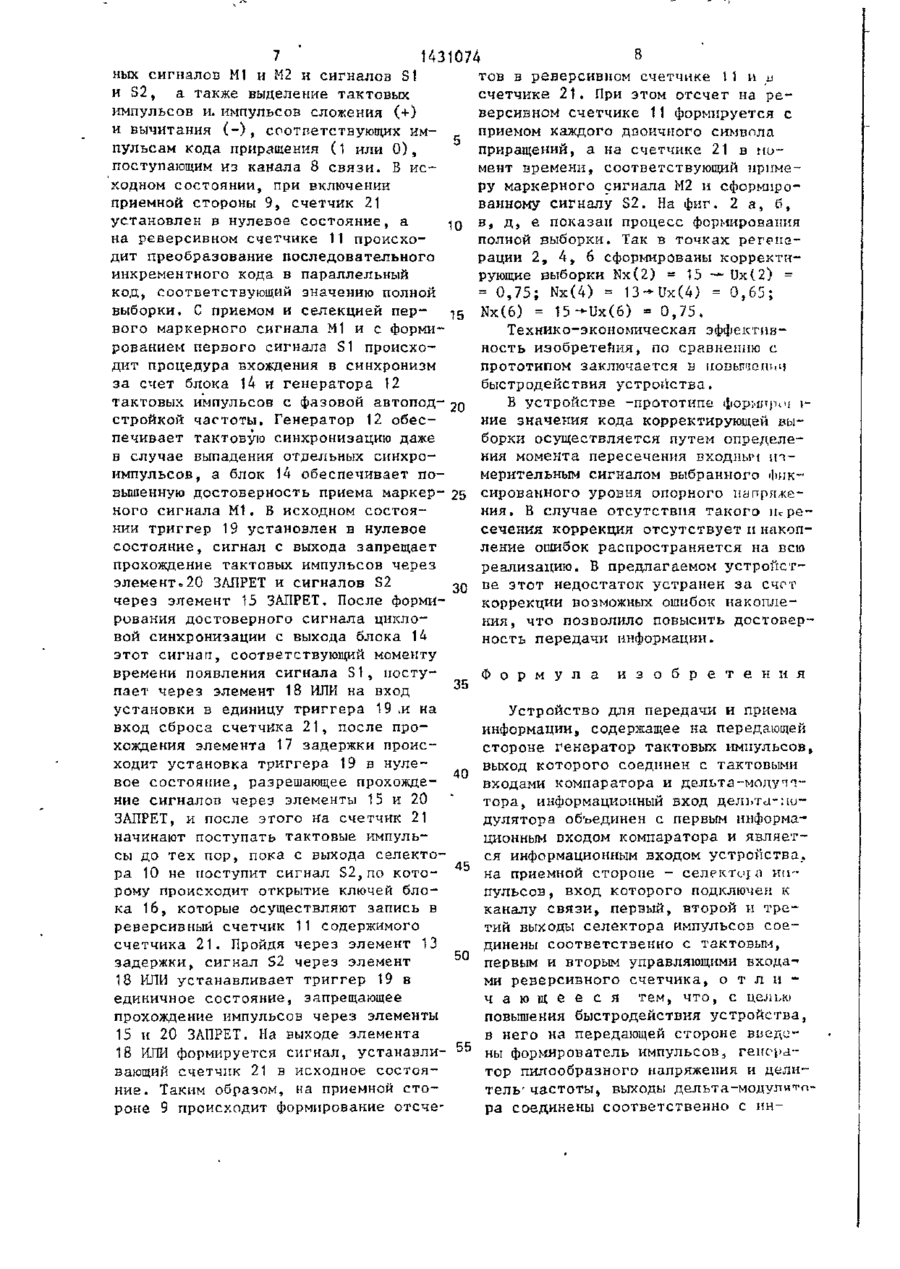

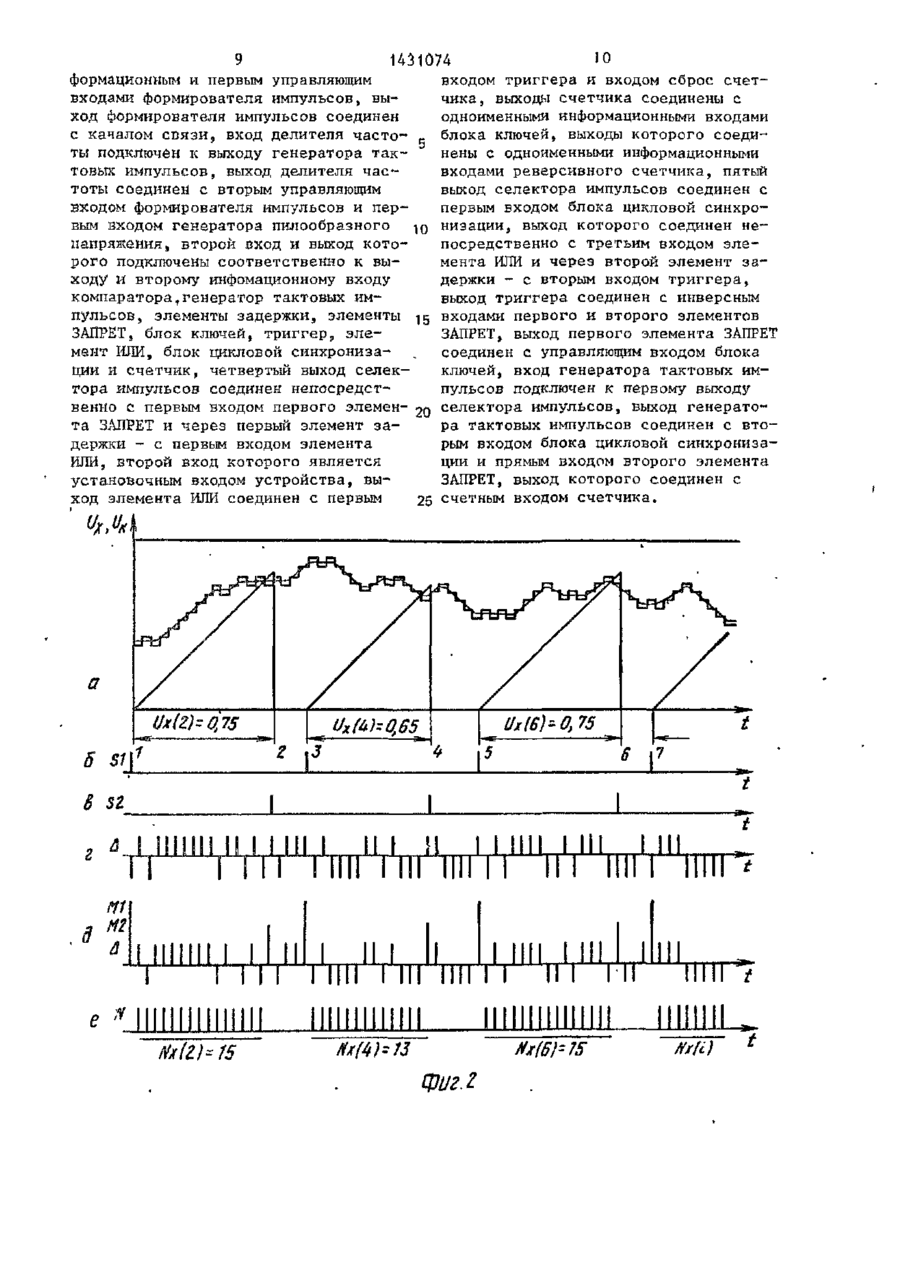

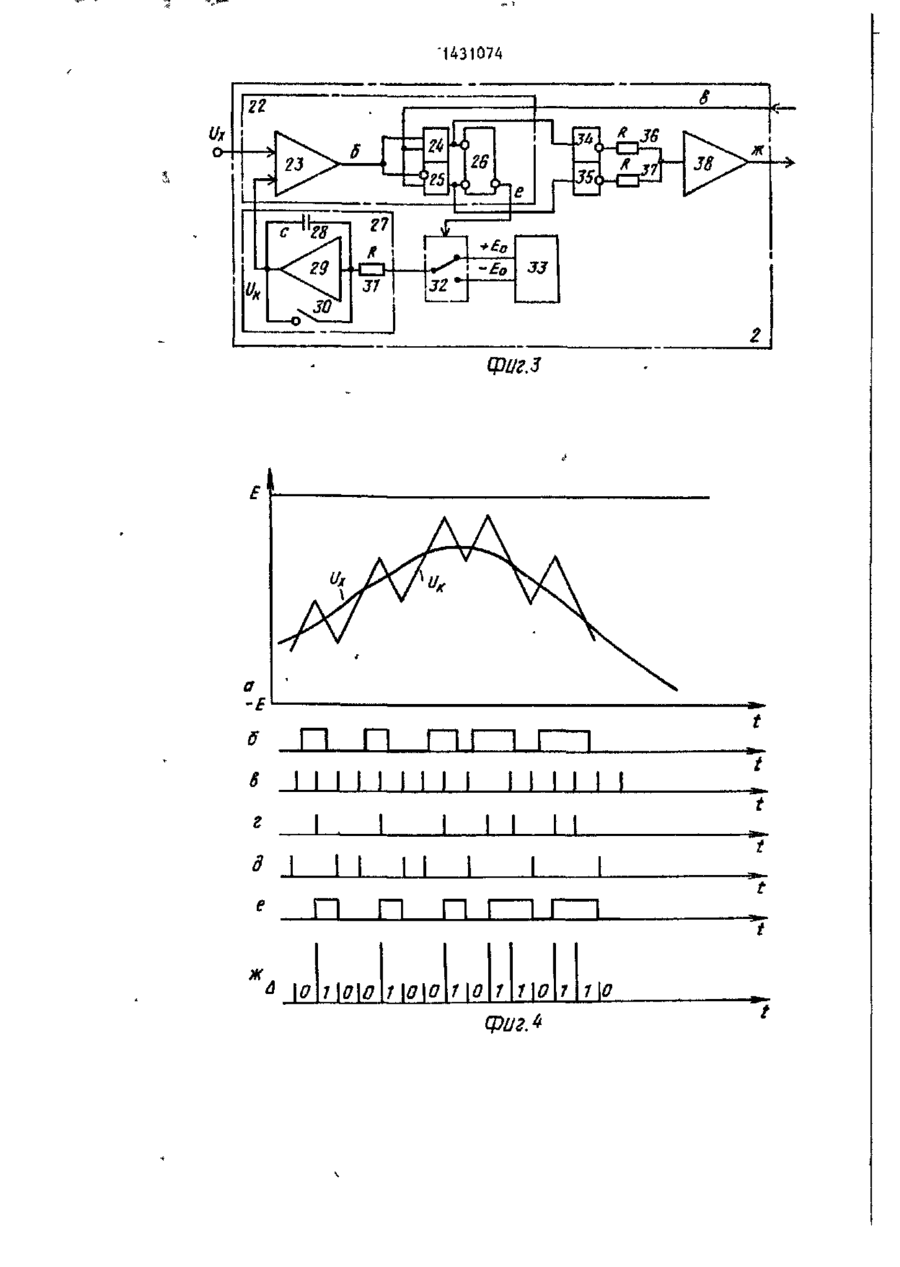

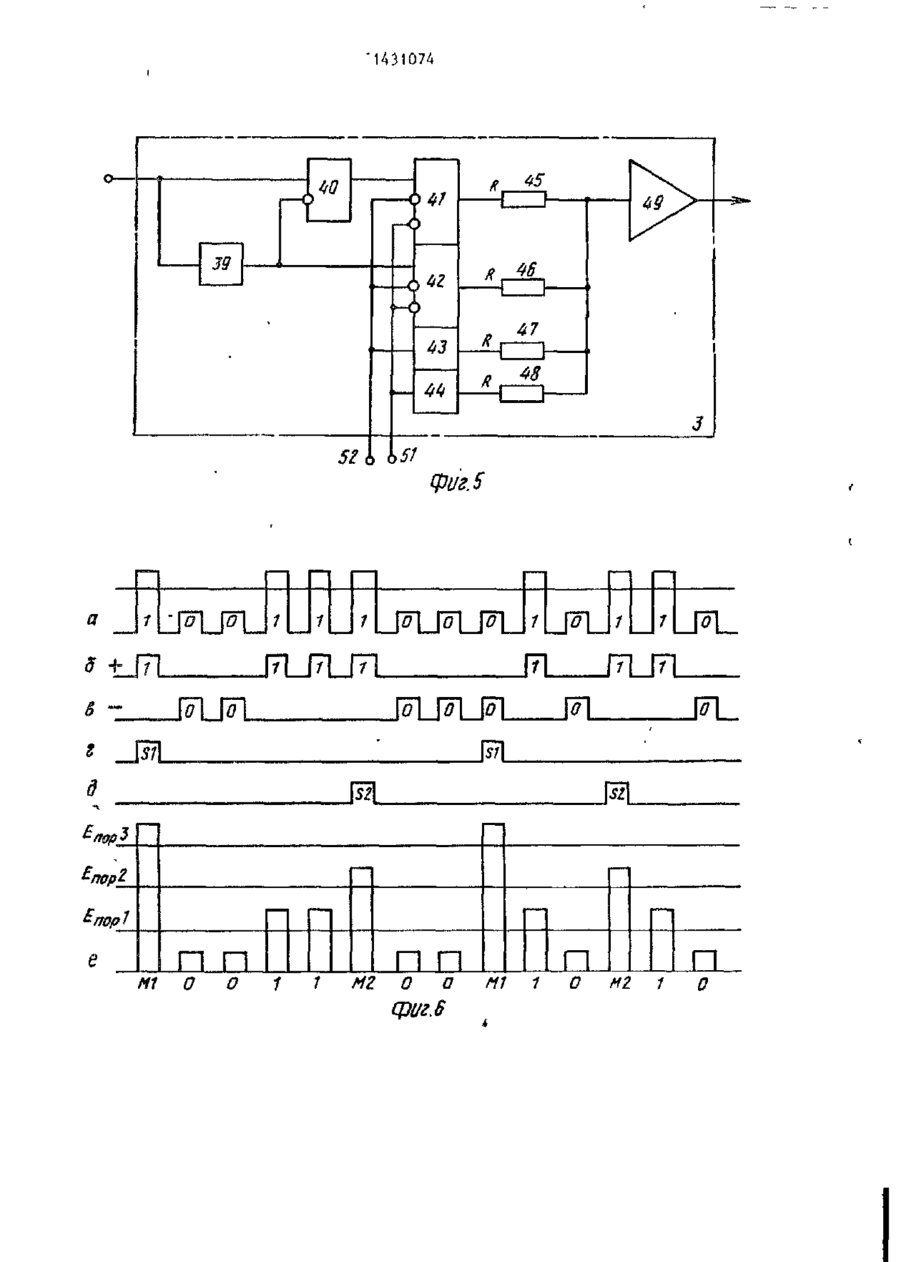

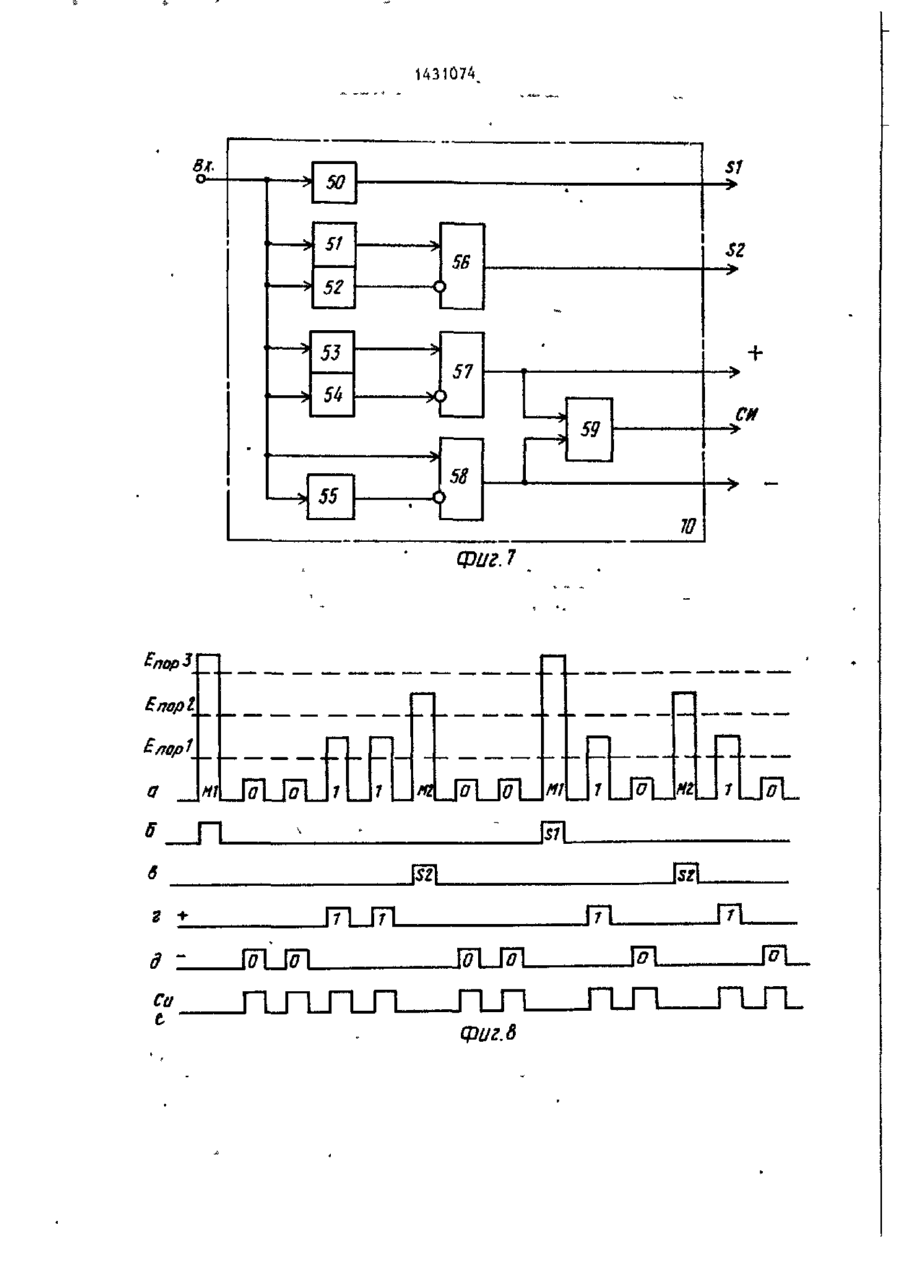

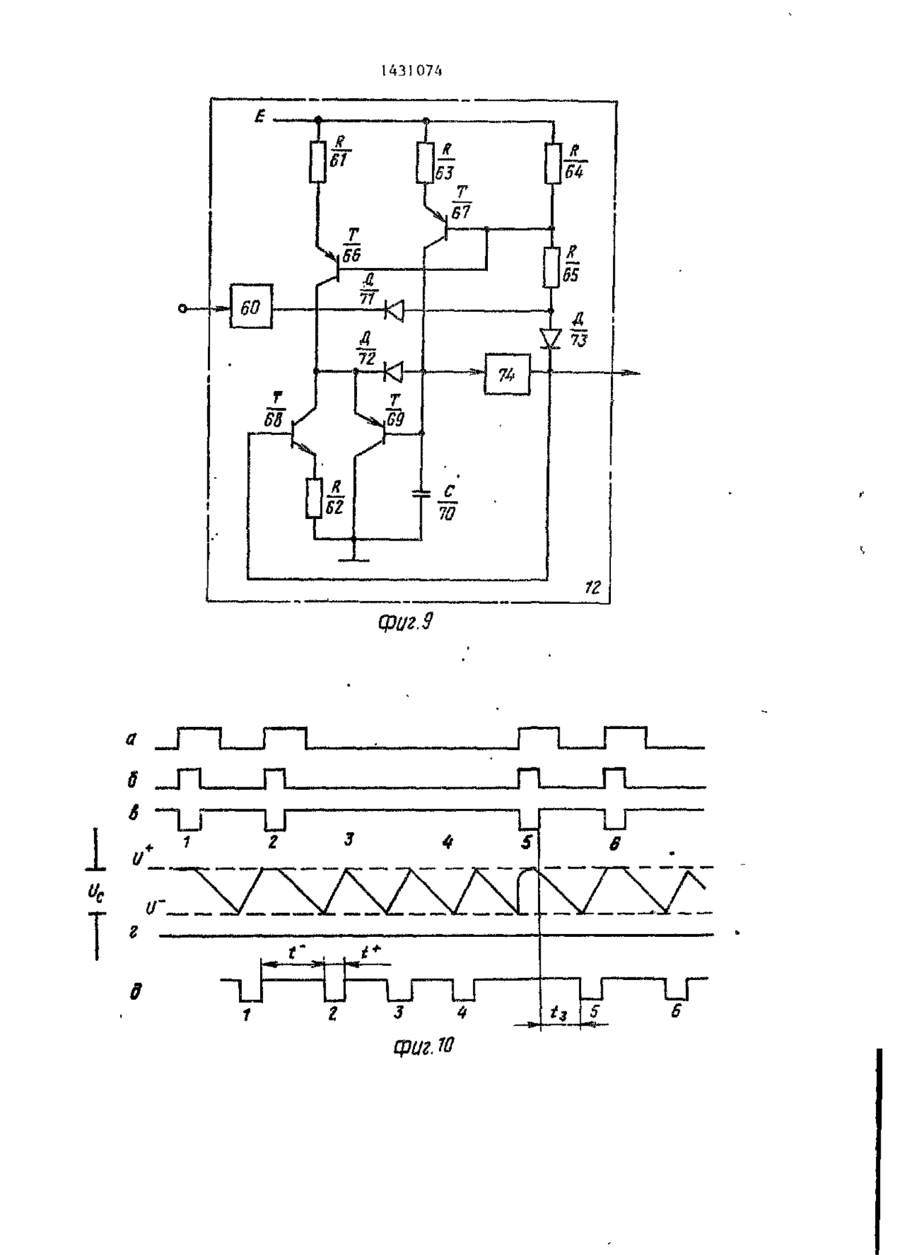

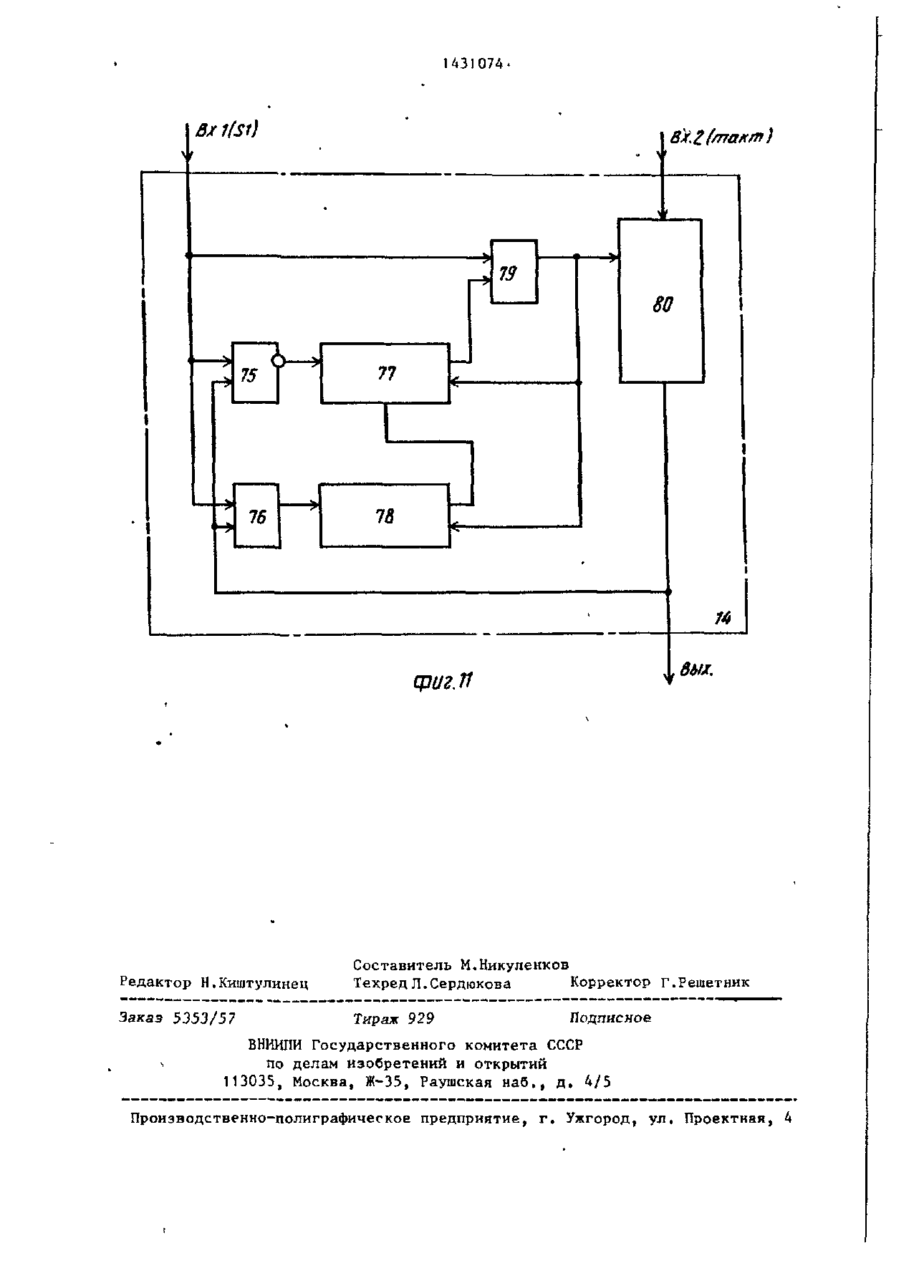

Изобретение относится к телеметсии и предназначено для цифровой пере дачи и приема непрерывных сигналов с использованием дельта-модуляции. Изобретение позволяет повысить достоверность передачи информации за счет коррекции возможных ошибок накопления. Устройство содержит на передающей стороне дельта-модулятор 2, формирователь 3 импульсов, компаратор 4, генератор 5 пилообразного напряжения, генератор 6 тактовых импульсов и дели тель 7 частоты, а на приемной стороне - селектор 10 импульсов, реверсивный счетчик 11, генератор 12 импульсов, элементы 13, 17 задержки, блок 14 цикловой синхронизации, элементы ЗАПРЕТ 15, 20, элемент ИЛИ 18, триггер 19 и счетчик 21. 11 ил. Фиг.і 1 1431074 Изобретение относится к телеметрии и может быть использовано при цифровой передачеі непрерывных сигналов с использованием дельта-модуляции. Цель изобретения - повышение быстродействия устройства. На фиг. t приведена структурная схема устройства; на фиг. 2 - времен- JQ ные диаграммы, поясняющие работу устройства; на фиг. 3 - функциональная схема дельта-модулятора; на фиг. 4 временные диаграммы, поясняющие работу дельта-модулятора; на фиг. 5 ^ функциональная схема формирователя импульсов; на фиг. 6,,- временные диаграммы, поясняющие работу формирователя импульсов; на фиг. 7 - функциональная схема селектора импульсов; 2Q на фиг. 8 - временные диаграммы, поясняющие работу селектора импульсов; на фиг. 9 - импульсная схема генератора тактовых импульсов с фазовой автоподстройкой частоты; на 25 фиг. 10 - временные диаграммы, поясняющие работу генератора тактовых импульсов с фазовой автоподстройкой частоты; на фиг. 11 - функциональная схема блока цикловой синхронизации. элементы 40-42 ЗАПРЕТ, повторители 43 и 44, резисторы 45-48, усилитель 49. Селектор импульсов (фиг. 7) содержит амплитудные селекторы 50-55, элементы 56-58 ЗАПРЕТ и элемент 59 ИЛИ. Генератор тактовых импульсов с фазовой автоподстройкой частоты (фиг. 9) содержит формирователь 60 импульсов, резисторы 61-65, транзисторы 66-69, конденсатор 70, диоды 71-73, триггеры 74 Шмидта. Блок цикловой синхронизации (фиг. 11) содержит элемент 75 И-НЕ, элемент 76 И, накопитель 77 и 78 элемент 79 И, делитель 80 частоты. Существенность отличий предлагаемого устройства по сравнению с прототипом заключается в повышении достоверности передачи информации и расширении функциональных возможностей устройства при сохранении минимальных аппаратных затрат на передающей стороне. Интенсивность коррекции ошибок накоплений в устройстве-прототипе зависит от динамических свойств измеряемого сигнала, от числа пересечений измеряемым сигналом выбранного фиксированного уровня опорного 30 напряжения. Если этого пересечения Устройство для передачи и приема не происходит, то коррекция отсутинформации (фиг. 1) содержит на перествует. Таким образом, если специфидающей стороне 1: дельта-модулятор 2, ка сигнала такова, что его пересечеформирователь 3 импульсов, компаратор ния с выбранным фиксированным уров4, генератор 5 пилообразного напряже 35 нем весьма редки, то эффективность ' ния, генератор 6 тактовых импульсов и метода резко снижается, а в некотоделитель 7 частоты, канал 8 связи, на рых случаях делает его применение приемной стороне 9: селектор 10 имвовсе нецелесообразным. пульсов, реверсивный счетчик 11, гене ратор 12 тактовых импульсов с автоФормирователь 3 импульсов (фиг. 5, матической подстройкой частоты, пер- 40 6 ) , работает следующим образом. вый элемент 13 задержки, блок 14 цик На вход формирователя 3 поступает ловой синхронизации, первый элемент последовательность двоичных символов 15 ЗАПРЕТ, блок 16 ключей, второй эле (преращений), причем нуль представмент 17 задержки, элемент 18 ИЛИ, лен как импульс положительной поляртриггер 19, второй элемент 20 ЗАПРЕТ 45 ности с амплитудой сигнала, равной и счетчик 21. U, а единица - с амплитудой 3 U. Импульсы с амплитудой 3 U поступают Дельта-модулятор (фиг. 3) содержит на вход амплитудного селектора 39, компаратор 22, выполненный на операна выходе которого формируется сигнал ционном усилителе 23, элементе 24 И, элементе 25 ЗАПРЕТ и RS-триггере 26, 50 " 1 " (фиг. 66). Этот сигнал поступает на инверсный вход элемента 40 ЗАПРЕТ. интегратор 27, выполненный на конденС выхода которого в этот момент вресаторе 28, операционном усилителе 29, мени сигнал не выдается. Таким обраключе 30 и резисторе 31, переключазом, импульсы " 0 " (фиг. 6в) лоступатель 32, источник 33 опорного напря55 ют на вход элемента 41 ЗАПРЕТ, а имжения, элементы 34 и 35 НЕ, резистопульсы " 1 " (фиг. 66) поступают на ры 36 и 37 и усилитель 38, вход элемента 42 ЗАПРЕТ. При поступФормирователь импульсов (фиг. 5) лении управляющих сигналов S1 (сигсодержит амплитудный селектор 39, 3 1431074 нал запуска) и S2 (сигнал сброса) на соответствующие входы элементов 41 и 42 (фиг. бг, д) выдача информации с выходов этих элементов осуществляется только в момент отсутствия сигналов S1 и S2. Таким образом, при поступлении сигнала S1 на входы элементов 41 и 42 происходит запрет выдачи информации через эти элементы, а сигнал S1 проходит через повторитель 44 и поступает на резистор 48, вес которого соотносится с весами резисторов 47-45 как 1:3:5:7. При поступлении сигнала S2 на входы элементов 41 и 42 происходит запрет выдачи информации через эти элементы, а сигнал S2 проходит через повторитель 43 и поступает на резистор 47, таким образом, в точке соеди20 нения резисторов 45-48 формируется смешанная кодовая последовательность двоичных символов (приращений) и маркерных сигналов, которая проходит через усилитель 49 и поступает на вы- 25 ход формирователя 3 (фиг. бе). При этом "О" выдается импульсом с амплитудой U, " 1 " - 3 U, маркерный сигнал М2 - 5U, маркерный сигнал М1 - 7U, Селектор 10 импульсов (фиг. 7 и 8) 30 осуществляет процедуру, противоположную процедуре формирователя 3, и использует принцип амплитудной селекции. На вход селектора 10 поступает 35 смешанная последовательность двоичных символов приращений и маркерных сигналов М1 и М2 (фиг. 8а), на его выходе фортіруются: сигнал S1 (фиг.86), соответствующий моменту времени по40 явления маркерного сигнала М1 (фиг, 8 а ) ; сигнал S2 (фиг. 8 в ) , соответствующий моменту времени появления маркерного сигнала М2 (фиг. 8а); сигнал " 1 " (фиг. 8г); сигнал " 0 " (фиг. 8д) и тактовые синхроимпульсы (фиг. 8е). Генератор 12 тактовой частоты, (фиг. 9 и 10) работает следующим образом. Зарядом и разрядом хронирующего конденсатора 70 управляет триггер 74, имеющий гистерезис в своей переходной характеристике. В режиме заряда выходное напряжение близко к нулю, транзисторы 66 и 67 открыты, зарядный ток определяется выражением (1), разрядный ток ответвляется в коллек* торную цепь транзистора 66, для чего должно выполняться условие Г с E-R4/(R4 + R5)-R1. Функция транзистора 69 - предотвращение насыщения транзистора 66 и ограничение запирающего напряжения на диоде 71, что необходимо при генерации высоких частот. Генератор 12 снабжен цепью блокировки: поступление сигнала (фиг, Ю в ) с выхода формирователя 60 приводит к прекращению генерации, так как не включается цепь разряда. После оконч а н и я сигнала блокировки первый импульс появляется на выходе генератора 12 с задержкой; = t" = С Ю/Ґ Таким образом, при отсутствии входных тактовых импульсов блокировка генератора 12 не обеспечивается и на его выходе присутствуют выходные тактовые импульсы. Блок 14 цикловой синхронизации работает следующим образом. Если устройство находится в состоянии синхронизма, то сигнал S1 с выхода селектора 10 совпадает во времени с сигналом с выхода делителя частоты, При этом на выходе элемента 75 И~НЕ сигнал отсутствует, а на выходе элемента 79 И формируется сигнал, соответствующий моменту опознавания маркерного сигнала МІ. В результате накопитель 78 по входу и. в синхронизм (рассчитанный обычно на два-три последующих подряд импульса) оказывается заполненным, а на50 копитель 77 по выходу из синхронизПод воздействием управляющего нама (рассчитанный на четыре-шесть слепряжения, которое формируется на выдующих подряд импульсов) - разряженходе триггера 74, изменяется разрядным до нулевого состояния. Ложные ный ток I", протекающий в коллектормаркерные сигналы М1. Формируемые в ной цепи транзистора 68. Зарядный ток 5 5 суммарном последовательном коде вследI (коллекторный ток транзистора 67) ствие воздействия помех, не совпадаостается неизменным и равным по времени с сигналом на выходе ю т делителя 80, а следовательно, и не I rE'R4/(R4 + R5) R3. (1) участвуют в процессе накопления. 1431074 При кратковременных искажениях маркерного сигнала Ml, возникающих либо при сбоях синхронизации в системе, либо под воздействием помех, сиг5 нал с выхода делителя 80 происходит через элемент 75 И-НЕ на вход накопителя 77. Однако если накопитель 77 не успевает заполниться, то сбоя синхронизации не происходит» и по пер10 вому сигналу с выхода накопителя 78 осуществляется сброс в нулевое состояние накопителя 77. При отсутствии синхросигнала в г. следующих подряд циклах (г1 - коэф15 фициент накопления в накоплителе 77) элемент 79 открывается и первый ложный импульс Stj, сформировавшийся на выходе селектора 14, приводит делитель 80 частоты и накопитель 78 в нулевое состояние, а накопитель 77 - в 20 состояние, соответствующее г. импульсам на его входе. Если ложный маркерный сигнал М1 формируется на одних и тех же пози25 циях цикла меньше, чем г 2 раз подряд (r-i - коэффициент накопления накопителя 78!), накопитель 77 оказывается заполненным и процесс опознавания маркерного сигнала продолжается до 30 момента формирования следующее и в н керного сигнала. Сигнал S1 с выхода селектора 14, пройдя через открытый элемент 79, устанавливает делитель 80 частоты в исходное состояние* Этот процесс длиться до тех пор, пока 35 не будет найден истинный маркерный сигнал Ml (или истинная синхрогруппа в случае кодового маркера). Если ложный маркерный сигнал М1 формируется 40 на одних и тех же позициях цикла тг или более раз подряд, накопитель 77 переходит в нулевое состояние и процесс опознавания маркерного сигнала прекращается до тех пор, пока вновь 45 не заполнится накопитель 77. Отсюда следует, что емкость накопителя 78 должна быть выбрана таким образом, чтобы практически в течение всего времени поиска состояния синхронизма накопителя 78 оставался заполненным. 50 При этом не происходит существенного замедления процесса поиска синхронизма. При обнаружении истинного синхросигнала накопитель 78 заполняется и сбрасывает накопитель 77 в нулевое 55 состояние, в результате чего обеспечивается достаточная инерционность системы цикловой синхронизации в резки ме удержания синхронизма. 6 Устройство, (фиг, 1 ) , работает следующим образом. В исходном состоянии после включения передающей стороны 1 генератор 6 тактовых импульсов осуществляет тактирование дельта-модулятора 2, компаратора 4 и делителя 7 частоты. Делитель 7 формирует сигнал S1, по которому запускается генератор 5 пилообразного напряжения и осуществляется управление формирователем 3 импульсов, на выходе которого формируется маркерный сигнал Ml (фиг. 2а, б, д ) , который в данном случае передается в виде импульсов положительной полярности и с амплитудой, большей, чем амплитуда импульСов двоичной последовательности (инкрементного кода), и амплитуды маркерного сигнала М2. Измеряемое напряжение Ux поступает на первый информационный вход компаратора 4 и на информационный вход дельта-модулятора 2, с выхода которого формируется последовательный код приращений (фиг. 2 г ) , который поступает на информационный вход формирователя 3 импульсов,. После поступления сигнала S1 на первый (запускающий) вход генератора 5 пилообразного напряжения с его выхода формируется линейно растущее напряжение, которое поступает на второй информационный вход компаратора 4. В момент сравнения напряжений входного измерительного сигнала с линейно растущим напряжением на выходе компаратора 4 формируется сигнал S2, который поступает на второй вход генератора 5, устанавливая его в исходное состояние, а также поступает на управляющий вход формирователя 3, на выходе которого формируется сигнал М2 (фиг. 2д) с амплитудой, меньшей, чем амплитуда маркерного сигнала М1, и большей, чем амплитуда двоичных символов приращений. Таким образом, на выходе формирователя 3 формируется смешанная последовательность символов приращений (0 и 1) и маркерных сигналов (М1 и М 2 ) . Данная смешанная кодовая последовательность информационных символов (0,1, М1, М2) поступает в канал 8 связи (фиг, 2д), где под воздействием ло~ мех происходят искажения информационных символов. Переданная по каналу 8 связи информация поступает на селектор 10 импульсов, где осуществляется выделение и формирование маркер 7 1431074 В ных сигналов Ml и М2 и сигналов S1 тов в реверсивном счетчике 1 1 и ї ї и S2, а также выделение тактовых счетчике 21. При этом отсчет на реимпульсов и. импульсов сложения (+) версивном счетчике 11 формируется с и вычитания (-), соответствующих имприемом каждого двоичного символа пульсам кода приращения (1 или 0 ) , приращений, а на счетчике 21 в мопоступающим из канала 8 связи. В исмент времени, соответствующий примеходном состоянии, при включении ру маркерного сигнала М2 и сформироприемной стороны 9, счетчик 21 ванному сигналу S2. На фиг. 2 а , б, установлен в нулевое состояние, а в, д, е показан процесс формирования 10 на реверсивном счетчике 11 происхополной выборки. Так в точках регенедит преобразование последовательного рации 2, 4, 6 сформированы корректиинкрементного кода в параллельный рующие выборки Nx(2) - 15 - • Ux(2) = * код, соответствующий значению полной = 0,75; Nx(4) = 13-Ux(4) = 0,65; выборки. С приемом и селекцией пер- 15 Nx(6) = 15-Ux(6) - 0,75. вого маркерного сигнала М1 и с формиТехнико-экономическая эффективрованием первого сигнала S1 происхоность изобретения, по сравнению с дит процедура вхождения в синхронизм прототипом заключается в попыгчсннч за счет блока 14 и генератора 12 быстродействия устройства. тактовых импульсов с фазовой автопод- 2Q В устройстве -прототипе форміфиі }стройкой частоты. Генератор 12 обесниє значения кода корректирующей выпечивает тактовую синхронизацию даже борки осуществляется путем определев случае выпадения отдельных синхрония момента пересечения входным нч~ импульсов, а блок 14 обеспечивает померительным сигналом выбранного Фиквышенную достоверность приема маркер25 сированного уровня опорного напряженого сигнала М1. В исходном состояния. В случае отсутствия такого перении триггер 19 установлен в нулевое сечения коррекция отсутствует п накопсостояние, сигнал с выхода запрещает ление ошибок распространяется на всю прохождение тактовых импульсов через реализацию. В предлагаемом устройстэлементно ЗАПРЕТ и сигналов S2 ве этот недостаток устранен за счет через элемент 15 ЗАПРЕТ. После форми- 30 коррекции возможных ошибок накоплерования достоверного сигнала циклония, что позволило повысить достовервой синхронизации с выхода блока 14 ность передачи информации. этот сигнагт, соответствующий моменту времени появления сигнала S1, постуФ о р м у л а и з о б р е т е н и я пает через элемент 18 ИЛИ на вход 35 установки в единицу триггера 19,и на Устройство для передачи и приема вход сброса счетчика 21, после проинформации, содержащее на передающей хождения элемента 17 задержки происстороне генератор тактовых импульсов, ходит установка триггера 19 в нулевыход которого соединен с тактовыми вое состояние, разрешающее прохождевходами компаратора и дельта-модугпние сигналов через элементы 15 и 20 тора, информационный вход дельта-моЗАПРЕТ, и после этого на счетчик 21 дулятора объединен с первым информаначинают поступать тактовые импульционным входом компаратора и являетсы до тех пор, пока с выхода селектося информационным входом устройства» ра 10 не поступит сигнал S2,по кото- 45 на приемной стороне - селектора имрому происходит открытие ключей блопульсов , вход которого подключен к ка 16, которые осуществляют запись в каналу связи, первый, второй и тререверсивный счетчик 11 содержимого тий выходы селектора импульсов соесчетчика 21. Пройдя через элемент 13 динены соответственно с тактовым, задержки, сигнал S2 через элемент 50 первым и вторым управляющими входа-' 18 ИЛИ устанавливает триггер 19 в ми реверсивного счетчика, о т л и единичное состояние, запрещающее ч а ю щ е е с я тем, что, с целью прохождение импульсов через элементы повышения быстродействия устройства, 15 и 20 ЗАПРЕТ. На выходе элемента в него на передающей стороне введе18 ИЛИ формируется сигнал, устанавли- 55 ны формирователь импульсов, генеравающий счетчик 21 в исходное состоятор пилообразного напряжения и делиние. Таким образом, на приемной стотель- частоты, выходы дельта-модулятороне 9 происходит формирование отсчера соединены соответственно с ин формационным и первым управляющим входами формирователя импульсов, выход формирователя импульсов соединен с каналом связи, вход делителя частоты подключен к выходу генератора тактовых импульсов, выход делителя частоты соединен с вторым управляющим входом формирователя импульсов и первым входом генератора пилообразного 10 напряжения» второй вход и выход которого подключены соответственно к выходу и второму инфомационному входу компараторатгенератор тактовых импульсов, элементы задержкиу элементы 15 ЗАПРЕТ, блок ключей, триггер, элемент ИЛИ, блок цикловой синхронизации и счетчик, четвертый выход селектора импульсов соединен непосредственно с первым входом первого элемен- 20 та ЗАПРЕТ и через первый элемент задержки - с первым входом элемента ИЛИ, второй вход которого является установочным входом устройства, выход элемента ИЛИ соединен с первым 25 входом триггера и входом сброс счетчика, выходы счетчика соединены с одноименными информационными входами блока ключей, выходы которого соединены с одноименными информационными входами реверсивного счетчика, пятый выход селектора импульсов соединен с первым входом блока цикловой синхронизации, выход которого соединен непосредственно с третьим входом элемента ИЛИ и через второй элемент задержки - с вторым входом триггера, выход триггера соединен с инверсным входами первого и второго элементов ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с управляющим входом блока ключей, вход генератора тактовых импульсов подключен к первому выходу селектора импульсов, выход генератора тактовых импульсов соединен с вторым входом блока цикловой синхронизации и прямым входом второго элемента ЗАПРЕТ, выход которого соединен с счетным входом счетчика. г ^JLlllllil T llJJUII,l..,.II.K..H....I.I Hi I III I I ПИ..I.ill III Є ' • #х{6!=75 Фиг. г I -II UNI / ПНИН > Me) 1431074 (рцг.з 1 1п б III 1 1 1 1 II г I I "~| 11 1 1 1 1 . 1 д 1 11 1 е п і—і ж п п 0 1 1 1 1 1 1 і—і i\i\o\i\i\o ериг А t t t 1431074 фііг.5 LFLJ +J71 e M1 ГЛ F] [Л Г О П О 1 г П мг о о сриг.6 Ml 1 П О Ml 1 П О 1431074 Зі SI 50 51 5В U 52 53 57 54 59 58 "LA 55 10 Фиг. 7 £napl_ Елор1\ a г + 1 Ml 1 FLJ71 ГП 151 e jarLTLn__rLn Ф(/г. 8 run TUTL 1431074 фиг. 9 T V д 1431074. 8)ї.і(такт) , вш. ериг.її Редактор Н.Киштулинец Составитель М.Никуленков Техред Л.Сердюкова Корректор Г.Решетник Заказ 5353/57 Тираж 929 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ДивитисяДодаткова інформація

Назва патенту англійськоюCommunication device

Автори англійськоюSevastianov Anatolii Kostiantynovych

Назва патенту російськоюУстройство для передачи и приема иформации

Автори російськоюСевастьянов Анатолий Константинович

МПК / Мітки

МПК: H03M 3/02

Мітки: пристрій, прийому, передачі, інформації

Код посилання

<a href="https://ua.patents.su/12-14067-pristrijj-dlya-peredachi-ta-prijjomu-informaci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для передачі та прийому інформації</a>

Попередній патент: Спосіб визначення електричної потужності та пристрій для його здійснення

Наступний патент: Спосіб отримання засобу, що має оцукруючу активність

Випадковий патент: Спосіб очищення води