Повнокольоровий світлодіодний дисплей

Формула / Реферат

Повнокольоровий світлодіодний дисплей, який містить екранний модуль з світлодіодами червоного, зеленого та синього кольорів, розташованих в попередньо заданому порядку, з'єднаних зі схемами керування градацією червоного, зеленого, синього кольорів, та модуль передачі даних з пам'яттю кадру для тимчасового збереження даних зображення, з'єднаних між собою схемою розподілу даних та послідовностями регістрів зсуву для переносу даних, які мають інформаційний регістр кадру, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці та нуля, другі входи вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, нульовий та одиничний входи вентилів першого тригера, з'єднані з модулем передачі даних, регістр керування кадром, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниць, нульові виходи кожного тригера, з'єднані через вентилі запису нуля з входом попереднього тригера, тригери керування просуванням одиниць в регістрі, одиничні виходи цих тригерів відповідно з'єднані з вентилями запису одиниць в тригери регістра, одиничні виходи тригерів регістра керування кадром відповідно з'єднані з входами вентилів запису нуля та одиниці тригерів, починаючи з другого інформаційного регістра кадру, входи усіх вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, інформаційний регістр рядка, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці та нуля, другі входи вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, регістр керування рядком, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці, нульові виходи кожного тригера через вентилі запису нуля, з'єднані з попереднім тригером, інші входи усіх вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, одиничні виходи кожного тригера відповідно з'єднані з входами вентилів запису одиниць та нулів тригерів свого інформаційного регістра, має тригери керування просуванням одиниць та нулів в регістрі, виходи яких відповідно з'єднані з входами вентилів запису одиниць та нулів тригерів регістра керування рядком, який відрізняється тим, що виходи першого тригера інформаційного регістра кадру та виходи усіх непарних тригерів відповідно з'єднані з входами вентилів запису одиниці та нуля перших тригерів інформаційних регістрів рядків, одиничний вихід останнього тригера регістра керування кадром з'єднано з входом вентиля запису одиниці першого тригера регістра керування останнього рядка, входи вентилів запису одиниці в перший тригер регістра керування першим та наступними рядками, крім останнього, відповідно з'єднані з одиничним виходом останнього тригера керування просуванням одиниць та нульовим виходом четвертого тригера регістра керування наступного рядка, входи вентилів запису нулів 2n-2-их та 2n-3-их тригерів регістра керування кадром з'єднані з одиничним виходом останнього тригера керування просуванням одиниць в регістрі керування n-им рядком, де n = 2,3,4,5,..., а інші входи вентилів 2n-2-го тригера з'єднані з нульовим виходом першого тригера регістра керування того ж рядка.

Текст

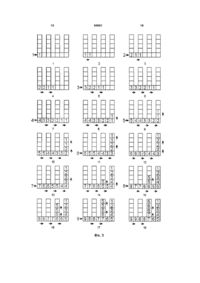

Повнокольоровий світлодіодний дисплей, який містить екранний модуль з світлодіодами червоного, зеленого та синього кольорів, розташованих в попередньо заданому порядку, з'єднаних зі схемами керування градацією червоного, зеленого, синього кольорів, та модуль передачі даних з пам'яттю кадру для тимчасового збереження даних зображення, з'єднаних між собою схемою розподілу даних та послідовностями регістрів зсуву для переносу даних, які мають інформаційний регістр кадру, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці та нуля, другі входи вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, нульовий та одиничний входи вентилів першого тригера, з'єднані з модулем передачі даних, регістр керування кадром, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниць, нульові виходи кожного тригера, з'єднані через вентилі запису нуля з входом попереднього тригера, тригери керування просуванням одиниць в регістрі, одиничні виходи цих тригерів відповідно з'єднані з вентилями запису одиниць в тригери регістра, одиничні виходи тригерів регістра керування кад 2 (19) 1 3 Винахід належить до обчислювальної техніки і може бути використаний для відображення відеоінформації шляхом передачі цифрових даних зображення на регістри зсуву. Використання способу широтно-імпульсного збудження світлодіодів трьох головних кольорів R, G, В (червоного, зеленого та синього) забезпечує отримання багатокольорових, багатотонових зображень з високою надійністю та якістю. Головним елементом зображення є піксель елементарна кольорова точка. Піксель може складатися з одного світлодіода або з декількох світлодіодів головних кольорів R, G, В. Сукупність пікселів формує зображення. Висока надійність світлодіодів (100000 годин безперервної роботи) [1], а також велика різноманітність у розмірах, сприяли їх використанню як в області великих екранів, так і в невеликих дисплеях. Сила свічення світлодіодів залежить від довжини та частоти поданих імпульсів. Чутливість до малої довжини сигналу (від 1 мксек) дозволяє формувати силу свічення у великому діапазоні. При кодуванні байтами сигнал має 256 градацій свічення. Для трьох кольорів R, G, В маємо 16777216 повнокольорових представлень (256х256х256). В основу керування градацією тонів зображення покладено спосіб широтно-імпульсного збудження, який реалізується з використанням лічильника імпульсів. В лічильник заздалегідь записується код градації або нулі. В першому варіанті лічильник працює на віднімання [2], а в другому - на додавання, до моменту зрівняння кодів лічильника з кодом заздалегідь встановленому на регістрі довжини [3]. Параметри імпульсів рахування можуть змінюватися з метою отримання необхідної якості зображення [3]. Відеоінформація може відображатися в матричних пристроях з використанням дисплейних елементів, які організовані в матрицю, яка складається з рядків та колонок. Сигнали відеоданих подаються на провідники колонок одночасно з поданням сигналів вибирання рядків. Кількість проводів зростає зі збільшенням дозвільної спроможності дисплея. Існує багато схемних рішень, спрямованих на зменшення цих сполучень [4]. Існує винахід [З], який вибрано за аналог, в якому аналогові сигнали зображення перетворюються в код та записуються в пам'ять кадру модуля передачі даних. Відеосигнал складається з 24-х бітів, по 8 бітів для кожного з кольорів R, G, В. Ці дані передаються за допомогою регістрів зсуву для переносу даних на схеми керування градацією червоного, зеленого та синього кольорів. Керування градацією тонів зображення провадиться з використанням способу широтно-імпульсного збудження (модуляції). Структурна схема цього приладу приведена на Фіг.1. Схема керування градацією включає в себе 8-розрядний лічильник імпульсів, цифрову схему зрівняння (компаратор) та 8-розрядний регістр. Лічильник відраховує імпульси зі сталим періодом до моменту зрівняння його вмісту з кодом на регістрі. Тактові імпульси лічби генеруються з високою частотою. Період лічильника визначається з моменту заповнення його вмісту нулями до моменту заповнення його 94661 4 одиницями. Таким чином, імпульси збудження шириною імпульсу, відповідною 8-бітним даним градації тонів зображення та відповідним періодом лічильника, висуваються з виходу компаратора. Схема збудження індикаторів пікселя подає сталий струм на світлодіоди та включає їх на період часу, який дорівнює ширині імпульсу збудження. Недоліком патенту, який вибрано за аналог, є відсутність реалізації схеми переносу кодів зображення від модуля передачі даних до екранного модуля. Уточнюючи, не показана реалізація схеми розподілу даних та послідовності регістрів зсуву для переносу даних. В основу запропонованого винаходу поставлена задача створення дисплея, за допомогою регістрів зсуву, з мінімальними інформаційними зв'язками, максимальною швидкодією, невеликими витратами устаткування за рахунок приведеного алгоритму зсуву та встановлення нових зв'язків поміж регістрів зсуву. Поставлена задача вирішується тим, що в повнокольоровому світлодіодному дисплеї, який містить екранний модуль зі світлодіодами червоного, зеленого та синього кольорів, розташованих в певному порядку, з'єднаних з схемами керування градацією червоного, зеленого, синього кольорів, та модуль передачі даних з пам'яттю кадру для тимчасового збереження даних зображення, з'єднаних поміж собою схемою розподілу даних та послідовностями регістрів зсуву для переносу даних, які мають інформаційний регістр кадру, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці та нуля, другі входи вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, нульовий та одиничний входи вентилів першого тригера з'єднані з модулем передачі даних, регістр керування кадром, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниць, нульові виходи кожного тригера з'єднані через вентилі запису нуля з входом попереднього тригера, тригери керування просуванням одиниць в регістрі, одиничні виходи цих тригерів відповідно з'єднані з вентилями запису одиниць в тригери регістра, одиничні виходи тригерів регістра керування кадром відповідно з'єднані з входами вентилів запису нуля та одиниці тригерів, починаючи з другого, інформаційного регістра кадру, входи усіх вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, інформаційний регістр рядка, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці та нуля, другі входи вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, регістр керування рядком, виконаний на тригерах, з'єднаних послідовно через вентилі запису одиниці, нульові виходи кожного тригера через вентилі запису нуля з'єднані з попереднім тригером, інші входи усіх вентилів відповідно з'єднані з однією з шин системи тактових імпульсів, одиничні виходи кожного тригера відповідно з'єднані з входами вентилів запису одиниць та нулів тригерів свого інформаційного регістра, має тригери керування просуванням одиниць та нулів в регістрі, виходи яких відповідно з'єднані з входами вентилів запису одиниць та нулів тригерів регістра керування рядком, виходи першого триге 5 ра інформаційного регістра кадру та виходи усіх непарних тригерів відповідно з'єднані з входами вентилів запису одиниці та нуля перших тригерів інформаційних регістрів рядків, одиничний вихід останнього тригера регістра керування кадром з'єднано з входом вентиля запису одиниці першого тригера регістра керування останнього рядка, входи вентилів запису одиниці в перший тригер регістра керування першим та наступними рядками, крім останнього, відповідно з'єднані з одиничним виходом останнього тригера керування просуванням одиниць та нульовим виходом четвертого тригера регістра керування наступного рядка, входи вентилів запису нулів 2n-2-х та 2n-3-х тригерів регістра керування кадром з'єднані з одиничним виходом останнього тригера керування просуванням одиниць в регістрі керування n-им рядком (де n = 2,3,4,5,…), а інші входи вентилів 2n-2-го тригера з'єднані з нульовим виходом першого тригера регістра керування того ж рядка. Суть винаходу пояснюється кресленнями, де зображені: на Фіг. 1 - структурна схема аналога пристрою; на Фіг. 2 - структурна схема пристрою; на Фіг. 3, 4 - алгоритм роботи пристрою; на Фіг.5, 6, 7- функціональна схема пристрою; на Фіг. 8, 9 - часові діаграми роботи пристрою; на Фіг. 10 - часові діаграми роботи 8розрядного регістра рядка. Реалізація запропонованого пристрою - Фіг. 2, 5, 6, 7, як приклад, показана у випадку приймання кодів зображення 4-ма 4-х розрядними інформаційними рядками. Прилад у загальному випадку, Фіг. 2, містить: Регістр керування кадром 1, інформаційний регістр кадру 2, інформаційний регістр рядків 3, регістри керування рядками 4. Функціональна схема пристрою - Фіг. 5, 6, 7, містить: Інформаційний регістр кадру для 4-х рядків 5, регістр керування кадром для 4-х рядків 6, 4-х розрядний інформаційний регістр 4-го рядка 7, регістр керування 4-им інформаційним рядком 8, 4-х розрядний інформаційний регістр 3-го рядка 9, регістр керування 3-ім інформаційним рядком 10, 4-х розрядний інформаційний регістр 2-го рядка 11, регістр керування 2-им інформаційним рядком 12, 4-х розрядний інформаційний регістр 1-го рядка 13, регістр керування 1-им інформаційним рядком 14, регістри виконані на тригерах 15 з вентилями запису одиниці 16 та вентилями запису нуля 17, входи вентилів з'єднані з однією з шин системи тактових імпульсів Т1 18 або Т2 19, елементи схеми пристрою, з'єднані між собою за допомогою ланцюгів 20-38, ланцюги прийому інформації від модуля передачі даних 39, 40, ланцюги керування пристроєм від модуля передачі даних 41, 42, 43. Виходи тригерів інформаційних регістрів рядків для зв'язку зі схемами керування градацією кольорів не показані. У пристрої використані, як приклад, потенційні елементи позитивної логіки. Вважаємо, що тригер 15 знаходиться в стані одиниці, коли на його одиничному виході - високий потенціал. Розряди усіх регістрів позначені як Р1, Р2, РЗ, та їх позначення зрівнюються з номерами тригерів 94661 6 регістра: Р1 - відповідає 1-му номеру тригера, Р22-му номеру тригера і так далі. Позначення К1, К2 відповідають тригерам керування в регістрах: К11-ий тригер керування, К2-2-ий тригер керування. На Фіг. 8, 9 приведені часові діаграми роботи повнокольорового світлодіодного дисплея для випадку, коли чисельність рядків дорівнює 4, а чисельність відліків в рядку (розрядів) також дорівнює 4. Цифрами 1, 2, 3, 4,...34 позначені номера напівтактів серії імпульсів зсуву Т1 та Т2. Всі позитивні сигнали належать до одиничного виходу тригерів: а - вхідний послідовний код, який видає модуль передачі даних; б, г, е, й, л, н, р - коди, які прийняті з першого по сьомий тригер інформаційного регістра кадру відповідно; в, д, ж, к, м, п - вихідні сигнали з першого по шостий тригер регістра керування кадром відповідно; т, ф, ч, щ - коди, які прийняті з першого по четвертий тригер четвертого інформаційного регістра рядка відповідно; с, у, х, щ - вихідні сигнали з першого по четвертий тригер регістра керування четвертим рядком відповідно; ю, я - вихідні сигнали К1, К2 тригерів керування просуванням одиниць в регістрі керування кадром відповідно; а1, 61 - вихідні сигнали К1, К2 тригерів керування просуванням одиниць та нулів в регістрі керування четвертим рядком відповідно; г1, е1, и1, л1 - коди, прийняті першим, другим, третім та четвертим тригерами третього інформаційного регістра рядка відповідно; в1, д1, ж1, к1 - вихідні сигнали першого, другого, третього та четвертого тригерів регістра керування третім рядком відповідно; м1, н1 - вихідні сигнали К1 та К2 тригерів керування просуванням одиниць та нулів в регістрі керування третім рядком відповідно; р1, т1, ф1, ч1 ~ коди, які прийняті з першого по четвертий тригер другого інформаційного регістра рядка відповідно; п1, с1, у1, х1 - вихідні сигнали з першого по четвертий тригер регістра керування другим рядком відповідно; а2, 62, - вихідні сигнали К1 та К2 тригерів керування просуванням одиниць та нулів в регістрі керування другим рядком відповідно; г2, е2, и2, л2 - коди, які прийняті з першого по четвертий тригер першого інформаційного регістра рядка відповідно; в2, д2, ж2, к2 - вихідні сигнали з першого по четвертий тригер регістра керування другим рядком відповідно; м2, н2 - вихідні сигнали К1 та К2 тригерів керування просуванням одиниць та нулів в регістрі керування першим рядком відповідно. На Фіг, 10 приведені часові діаграми роботи дисплея у випадку, коли чисельність рядків дорівнює 4, а чисельність відліків в рядку (розрядів) дорівнює 8: а - вхідний послідовний код, який видає модуль передачі даних; 7 б, г, е, й, л, н, р - коди, прийняті з першого по сьомий тригер інформаційного регістра кадру відповідно; в, д, ж, к, м, п - вихідні сигнали з першого по шостий тригер регістра керування кадром відповідно; т, ф, ч, щ, я, 61, г1, е1 - коди, прийняті з першого по восьмий тригер четвертого інформаційного регістра рядка відповідно; с, у, х, ш, ю, а1, в1, д1 - вихідні сигнали з першого по восьмий тригер регістра керування четвертим рядком відповідно; ж1, и1, - вихідні сигнали тригерів керування просуванням одиниць в регістрі керування кадром; к1, л1 - вихідні сигнали тригерів керування просуванням одиниць в регістрі керування четвертим рядком відповідно; м1, н1 - вихідні сигнали тригерів керування просуванням нулів в регістрі керування четвертим рядком відповідно; р1, т1, ф1, ч1 - коди, прийняті з першого по четвертий тригер третім інформаційним регістром рядка відповідно; п1, с1, у1, х1, ш1 - вихідні сигнали з першого по п'ятий тригер регістра керування третім рядком відповідно. Пристрій працює таким чином. В основу роботи пристрою покладено алгоритм, показаний на Фіг. 3, Фіг. 4, де квадратами визначені тригери регістрів. Нижній горизонтальний ряд квадратів визначено тригерами інформаційного регістра кадру, нумерація зліва направо. Вертикальні ряди квадратів визначені тригерами інформаційних регістрів рядків, перерахування рядків зліва направо, а перерахування тригерів в рядку - знизу доверху. Перерахування рисунків знизу відповідає номеру напівтакту в часових діаграмах, Фіг.8, 9, 10. Стрілками визначені передачі інформації між тригерами в кожний часовий напівтакт. Перші тригери інформаційних регістрів рядків з'єднані з непарними номерами тригерів інформаційного регістра кадру: перший тригер інформаційного регістра першого рядка з'єднані з першим тригером інформаційного регістра кадру, перший тригер інформаційного регістра другого рядка з'єднані з третім тригером інформаційного регістра кадру, перший тригер інформаційного регістра третього рядка - з п'ятим тригером інформаційного регістра кадру, а перший тригер інформаційного регістра четвертого рядка - з сьомим тригером інформаційного регістра кадру. Подивимось докладно роботу алгоритму у випадку прийняття інформації четвертим інформаційним регістром рядка. Цей алгоритм вперше був розкритий у винаході СРСР [5], пізніше заявлено в патенті Великобританії [6], а також докладно розписані переваги його використання в мікроелектроніці [7], [8]. Спочатку розглянемо алгоритм прийому інформації одним рядком - четвертим, Фіг. 3. У напівтакті 8 інформація 1 з 7-го тригера інформаційного регістра кадру переписується в 1-ий тригер інформаційного регістра 4-го рядка, у напівтакті 9 інформація 1 з першого тригера переписується у другий, у напівтакті 10 інформація 2 переписується з 7-го тригера в перший тригер 4-го інформаційного регістра рядка, а інформація 1 з 2-го тригера - в 3-ій тригер, у 11 94661 8 му напівтакті інформація 2 з першого тригера переписується у 2-ий тригер, а інформація 1 третього тригера - в четвертий тригер, у 12-му напівтакті інформація 3 переписується з 7-го тригера інформаційного регістра кадру в 1-ий тригер інформаційного регістра четвертого рядка, інформація 2 - з 2-го тригера в 3-ій тригер, закінчився запис у четвертий тригер, в якому залишається раніше записана 1, у 13-му напівтакті інформація 3 з першого тригера переписується у 2-ий тригер, інформація 2 залишається у 3-му тригері, у 14 напівтакті інформація 4 переписується з 7-го тригера інформаційного регістра кадру в 1-ий тригер 4-го інформаційного регістра рядка. Таким чином, за 7 напівтактів уся подана інформація з 7-го тригера інформаційного регістра кадру прийнята 4-им інформаційним регістром рядка. Аналогічно, інформація 5, 6, 7, 8 приймається третім інформаційним регістром рядка, за напівтакти 14,1 5, 16, 17, 18, 19, 20; інформація 9, 10, 11, 12 приймається другим інформаційним регістром рядка за напівтакти 20-26; інформація 13, 14, 15, 16 приймається першим інформаційним регістром рядка за напівтакти 2632. Інформація в інформаційному регістрі кадру спочатку просувається аналогічно її просуванню в інформаційних регістрах рядків, з тією різницею, що після прийому останньої інформації першим тригером інформаційного регістра рядка записується, а потім забороняється запис у з'єднаний з ним непарний тригер та попередній йому парний тригер інформаційного регістра кадру. На часовій діаграмі Фіг. 3, Фіг. 4: запис та заборона інформації 5, 6 - напівтакти 14-17; запис та заборона інформації 9, 10 - напівтакти 20-23; запис та заборона інформації 12, 13 - напівтакти 26-29; запис та заборона інформації 16 у напівтактах 31-32, так як для першого тригера немає попереднього. Заповнення інформаційних регістрів рядків починається з четвертого, а закінчується першим інформаційним регістром рядка. З моменту подачі інформації в перший тригер інформаційного регістра кадру та до появлення її в 1-му тригері четвертого інформаційного регістра рядка інформація затримується. Особливістю запропонованого алгоритму є те, що для компенсації вказаної затримки алгоритмом пропонується одночасний запис останньої інформації в перший тригер даного інформаційного регістра рядка та знову поданої інформації в перший тригер попереднього інформаційного регістра рядка: напівтакт 14 - запис інформації 4, 5; напівтакт 20 - запис інформації 8, 9; напівтакт 26 - запис інформації 12, 13. Структурна схема пристрою показана на Фіг. 2, а функціональна схема реалізації запропонованого алгоритму на Фіг. 5, 6, 7. Інформація від модуля передачі даних, Фіг.2, подається в інформаційний регістр кадру 2 та розподіляється поміж інформаційними регістрами рядків 3, заповнюючи спочатку останній рядок, а закінчуючи першим, за допомогою регістра керування кадром 1 та регістрів керування рядком 4. Вхідна інформація 1-16 від модуля передачі даних, Фіг. 5, по ланцюгах 39, 40 подається на входи вентилів 16, 17 першого тригера Р1 інформаційного регістра кадру 5 та послідовно пересувається поміж тригерами 15 до її подачі в тригер Р7, часові діаграми а, б, г, е, 9 й, л, н, р, Фіг. 8, напівтакти 1-7. Дозвіл на пересування інформації послідовно в часі, такти Т1 та Т2, видається одиничними виходами тригерів Р1-Р6 регістра керування кадром 6 в результаті послідовного заповнення регістра одиницями, Фіг. 8, часові діаграми - в, д, ж, к, м, п. Дозвіл на заповнення регістра керування кадром одиницями видається тригерами К1 та К2, часові діаграми - ю, я. Після вступу інформації в 7-ий тригер інформаційного регістра кадру, напівтакт 7, часові діаграми сигналу р, Фіг.8, інформація по ланцюгах 26, 27 подається в перший тригер інформаційного регістра рядка 7, Фіг. 6. Дозвіл на вступ інформації дається одиничним виходом 6-го тригера регістра керування кадром 6 по ланцюгу 37. Заповнення одиницями тригерів 1, 2, 3, 4-го регістра керування рядком 8, сигнали с, у, х, ш, напівтакти 7-10, дозволяє послідовне приймання інформації тригерами 1-4 інформаційного регістра рядка 7, сигнали т, ф, ч, щ, відповідно. Після вступу інформації 1 в 4ий тригер інформаційного регістра рядка 7, напівтакт 11, відбувається послідовне приймання та заборона інформації 2, 3, 4 тригерами регістра 7. Після прийняття інформації, заборона відбувається послідовною установкою тригерів 4, 3, 2, 1 регістра 8 в нуль, напівтакти 12-15. Тригер керування просуванням нулів та одиниць К1 керує установкою в нуль тригерів 4, 3, 2 послідовно, а тригер К2 - установкою в нуль 1-го тригера регістра керування рядком 8, часові діаграми сигналів а1, 61. Крім того, тригер К2, керує установкою в нуль тригерів 5 та 6 регістра керування кадром 6, ланцюг 34. Після установки в нуль першого тригера регістра керування рядком 8, напівтакт 15, установлюється в нуль тригер 6 регістра керування кадром 6, по ланцюгу 28, напівтакт 16, а потім установлюється в нуль тригер 5 регістра керування кадром 6, напівтакт 17. Установка 5-го тригера в нуль дозволяє по ланцюгу 35 встановити в нуль тригер К2 регістра керування рядком 8, напівтакт 18. Таким чином, з 8-го по 16-ий напівтакт інформаційний регістр рядка 7 прийняв послідовно подану інформацію 1, 2, 3, 4, а інформація 5, 6 залишилася в 7-му та 6-му тригерах інформаційного регістра кадру відповідно. До моменту появи інформації 5 в п'ятому тригері інформаційного регістра кадру 5, напівтакт 13, установлюється в одиницю перший тригер регістра керування рядком 10 (ланцюги дозволу установки - одиничний вихід тригера керування К2 та нульовий вихід четвертого тригера регістра керування рядком 8), сигнали ш, 61 часової діаграми Фіг.8. Послідовна установка тригерів 1, 2, 3, 4 в одиницю, сигнали в1, д1, ж1, к1 часової діаграми, дозволяє просуванню інформації 5, 6, 7, 8 по ланцюгах 24, 25 з виходів 5-го тригера інформаційного регістра кадру 5 в інформаційний регістр рядка 9, сигнали г1, е1, и1, л1. Послідовною установкою тригерів 4, 3, 2, 1 в нуль керують тригери К1 та К2 регістра керування рядком 10, сигнали м1, н1 часової діаграми, а також вони керують послідовною установкою в нуль тригерів Р4 та Р3 регістра керування кадром 6. Зв'язок між регістрами керування відбувається по ланцюгах 29, 32, 38. З 14-го по 22ий напівтакт вхідна інформація 5, 6, 7, 8 приймається інформаційним регістром рядка 9, інформа 94661 10 ція 9, 10 залишається відповідно в тригерах Р5, Р4 інформаційного регістра кадру 5. До моменту появи інформації 9 в тригері РЗ інформаційного регістра кадру 5, напівтакт 19, установлюється в одиницю перший тригер регістра керування рядком 12 (ланцюги дозволу установки - одиничний вихід тригера керування К2 та нульовий вихід четвертого тригера регістра керування рядком 10), ланцюги 33, 38, Послідовна установка тригерів 1, 2, 3, 4 в одиницю, сигнали п1, с1, у1, х1 часової діаграми, дозволяє просування інформації 9, 10, 11, 12 по ланцюгах 22, 23, з виходів третього тригера інформаційного регістра кадру 5 в інформаційний регістр рядка 11, сигнали р1, т1, ф1, ч1. Послідовною установкою тригерів 4, 3, 2, 1 в нуль відповідно керують тригери керування К1 та К2 регістра керування рядком 12, сигнали а2, 62 часової діаграми Фіг. 9, а також вони керують послідовною установкою в нуль тригерів Р2, Р1 регістра керування кадром 6. Зв'язок поміж регістрами керування відбувається по ланцюгах 30, 31, 36. В напівтактах з 20го по 28-ий вхідна інформація 9, 10, 11, 12 приймається інформаційним регістром рядка 7, інформація 13, 14 залишається в тригерах Р3, Р2 інформаційного регістра кадру 5, відповідно. В напівтакті 25 з'являється інформація 13 в першому тригері інформаційного регістра кадру 5, Фіг. 8; установлюється в одиницю перший тригер регістра керування рядком 14, Фіг. 9, ланцюги дозволу установки - одиничний вихід тригера К2 та нульовий вихід четвертого тригера регістра керування рядком 14, сигнали х1, 62 часової діаграми, Фіг.8, 9. Послідовна установка тригерів 1, 2, 3, 4 в одиницю, сигнали в2, д2, ж2, к2 часової діаграми дозволяє просування інформації 13, 14, 15, 16 по ланцюгах 20, 21 з виходів першого тригера інформаційного регістра кадру 5 в інформаційний регістр рядка 13, сигнали г2, е2, и2, л2. Послідовним перемиканням тригерів 4, 3, 2, 1 керують тригери К2 та К1 регістра керування рядком 14, відповідно, сигнали м2, н2 часової діаграми Фіг. 9. 3 26-го по 32-ий напівтакт вхідна інформація 13, 14, 15, 16 приймається інформаційним регістром рядка 13. В першому тригері інформаційного регістра кадру 5 залишається інформація 16. Після установки в нуль тригера К1 регістра керування рядком 14, установлюється в нуль тригер К2, напівтакт 34, і пристрій готовий до прийому інформації наступного кадру. Цей сигнал готовності подається в модуль кадру по ланцюгу 43. Такий же сигнал по довжині, в такті Т2, може подаватися для запуску пристрою по ланцюгу 42 синхронно з початком введення вхідної інформації по ланцюгах 39, 40. Тригер К1, наприклад, може установлюватися в одиницю по ланцюгу 41 від модуля кадру 3 приведеного розпису роботи пристрою видно, що запуском першого тригера регістра керування n-им рядком використовуються сигнали від регістра керування (n+1)-им рядком, тому що заповнення рядків відеоінформацією починається з останнього інформаційного рядка, а закінчується першим. Для запуску регістра керування n-им рядком використовується нульовий вихід четвертого тригера регістра керування (n+1)-им рядком та одиничний вихід останнього тригера керування просуванням 11 нулів в регістрі керування рядком. Ці зв'язки використовуються завжди незалежно від розрядності інформаційного регістра кадру (числа рядків) та розрядності інформаційного регістра рядків (кількості відліків в рядку). Покажемо це на прикладі, коли кількість рядків дорівнює 4, а кількість відліків в рядку - 8, Фіг. 10. Сигнали а, б, в, г, д, е, ж, й, к, л, м, н, п, р на Фіг. 10 аналогічні таким же сигналам на Фіг.8, а сигнали ю, я, Фіг.8, аналогічні сигналам ж1, и1 на Фіг. 10. У напівтакті 7, сигнал с, записується 1 в перший тригер регістра керування рядком. Просуванням одиниць в регістрі керування кадром керують по аналогії зі схемою Фіг. 3, 4, 5, тригери К1 та К2, сигнали ж1, и1. Інформація 1, 2, 3, 4, 5, 6, 7, 8 просувається в інформаційному регістрі рядка, сигнали т, ф, ч, щ, я, 61, г1, е1, до напівтакту 15 за допомогою тригерів регістра керування рядком, сигнали с, у, х, ш, ю, а1, в1, д1. Просування одиниць в регістрі керування рядком здійснюють окремі тригери керування просуванням одиниць, сигнали к1, л1, а з напівтакту 15 просування нулів здійснюють окремі тригери керування просуванням нулів, сигнали м1, н1. Для запуску першого тригера наступного регістра керування рядком, сигнал п1, використовується, що необхідно було показати, нульовий вихід четвертого тригера, сигнал ш, та одиничний вихід останнього тригера керування просуванням нулів в регістрі керування четвертим рядком, сигнал н1. З запуском першого тригера регістра керування наступного рядка відбувається послідовна установка тригерів регістра керування третім рядком, сигнали с1, у1, х1, ш1, та просування інформації 9, 10, 11, 12, 13, сигнали р1, т1, ф1, ч1. При незначній розрядності інформаційних регістрів рядків перемикання направлення руху одиниць та нулів в регістрі керування досить використовувати нульовий та одиничний виходи одного тригера керування. При більшій розрядності кількість тригерів керування просуванням нулів та одиниць потрібно було б збільшити з урахуванням навантаження. Але виникає проблема довгих зв'язків при запуску першого тригера регістра керування рядком, коли останній тригер керування просуванням нулів конструктивно віддаляється від четвертого тригера регістра керування рядком. Тому бажано будувати ланцюг тригерів, які керують просуванням нулів та такий же ланцюг тригерів для просування одиниць, але ланцюг тригерів для просування ну 94661 12 лів необхідно розмістити в напрямку ближче до четвертого тригера регістра керування рядком. Як вже відзначалося, їх кількість та зв'язки поміж ними визначаються відповідно з навантаженням. Необхідно також відмітити, що регістр керування як кадром, так і рядками є швидкодіючим у порівнянні з класичним лічильником, бо схема його будови не залежить від часу відліку (від його розрядності). Таким чином, регістри керування можна будувати практично необмеженими по розрядності, швидкодії, розв'язаними по навантаженню, з мінімальною довжиною зв'язків між тригерами. Якщо взяти відеоекран з 1024Х768 точок дискретності, використовуючи 8 розрядів для одного кольору пікселя, при частоті кадрів 60 Гц, частота проходження інформаційного коду буде: 1024х768х8х60 = 377,4873 мГц. Світлодіоди можуть виготовлятися методом інтегральної технології з випромінюючою часткою діаметром 0,1 мм при струмі споживання 10-20 мкА [9]. Тому дисплеї можуть мати невеликі розміри. При використанні трьох каналів для кольорів R, G, В можливо одержати значну економію в логічних елементах, використовуючи регістри керування кадром та рядками одного каналу для керування інформаційними каналами двох других кольорів. Запропонований пристрій може бути використано для передачі текстів шляхом розподілення світлодіодів у вигляді знакомісць 5х7 в кожному рядку. Так як в регістрах керування можна виявити будь-який часовий момент при передачі інформації, то можливо при передачі тексту засвічувати послідовно кожен символ або рядок. Джерела інформації. 1. Журнал "Screens, ru", 20.04.2004, http://www.screens.ru/. 2. RU 2316139 C1, 27.01.2008, МПК H04N9/12. 3. RU 2249858 C2, 10.04.2005, МПК G09G3/32, G09F9/33. 4. RU 2160933 C2, 20.12.2000, МПК G09 3/36. 5. SU 337825 A1, 01.01.1972, МПК G11C19/00. 6. GB 1475820, 10. 06. 1977, МПКС11С7/00, 19/00. 7. Журнал СССР "Электронная промышленность" №2, 1989, стр. 46 "Последовательная матрица памяти", Тесленко-Пономаренко В. П. 8. SU 1339652 A1, 23.09.1987, МПК G11 С7/00. 9. RU 2334279 C1, 20.09.2008, МПК G09 G3/32. 13 94661 14 15 94661 16 17 94661 18 19 94661 20 21 94661 22 23 94661 24 25 94661 26 27 Комп’ютерна верстка А. Крижанівський 94661 Підписне 28 Тираж 24 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюFull-color light-emitting diode display

Автори англійськоюTeslenko-Ponomarenko Valentyn Pavlovych

Назва патенту російськоюПолноцветный светодиодный дисплей

Автори російськоюТесленко-Пономаренко Валентин Павлович

МПК / Мітки

МПК: G09G 3/32

Мітки: повнокольоровий, дисплей, світлодіодний

Код посилання

<a href="https://ua.patents.su/14-94661-povnokolorovijj-svitlodiodnijj-displejj.html" target="_blank" rel="follow" title="База патентів України">Повнокольоровий світлодіодний дисплей</a>

Попередній патент: Аміно-гетероциклічні сполуки

Наступний патент: Спосіб експлуатації паротурбінної установки, а також пристрій для виробництва пари

Випадковий патент: Спосіб багаторівневого багатошарового оптичного запису і зчитування інформації