Регістрова пам’ять

Номер патенту: 5547

Опубліковано: 15.03.2005

Автори: Куценко Геннадій Вікторович, Тесленко-Пономаренко Валентин Павлович

Формула / Реферат

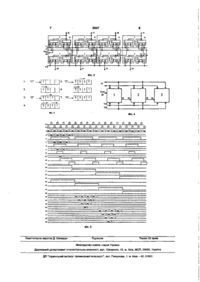

Регістрова пам'ять, що містить інформаційні регістри, виконані на тригерах, з'єднаних послідовно через вентилі запису нуля й одиниці, інші входи цих вентилів відповідно з'єднані із шиною першої й другої системи тактових імпульсів, а також регістр керування, одиничні виходи тригерів якого відповідно з'єднані з вентилями запису нуля й одиниці тригерів інформаційних регістрів, крім перших тригерів прийому вхідної інформації, і з вентилями запису одиниці тригерів регістра керування; тригер керування регістром керування, нульовий вихід якого з'єднаний із входами вентилів запису одиниці тригерів регістра керування, а одиничний вихід його з'єднаний із входами вентилів запису нуля тих же тригерів, входи вентилів запису нуля й одиниці цих тригерів також з'єднані із системою тактових імпульсів, нульові виходи наступного тригера регістра керування з'єднані з входами вентилів запису нуля попереднього тригера, нульовий вихід першого тригера регістра керування з'єднаний із входом вентиля запису нуля тригера керування регістром керування; додатковий тригер регістра керування з'єднаний з вентилями запису нуля й одиниці, причому входи вентиля запису одиниці з'єднані з одиничним виходом тригера керування регістром керування, нульовим виходом другого тригера регістра керування, входи вентиля запису нуля з'єднані з нульовим виходом тригера керування регістром керування, нульовим виходом другого тригера регістра керування, інші входи вентилів з'єднані з однією із шин системи тактових імпульсів, розподільник імпульсів з основними і допоміжними тригерами, одиничні виходи основних тригерів з'єднані з вентилями запису нуля й одиниці перших тригерів інформаційних регістрів, інші входи цих вентилів з'єднані з інформаційними шинами вхідного парафазного коду, а одиничні виходи допоміжних тригерів розподільника імпульсів з'єднані з входами вентилів запису нуля й одиниці інших тригерів відповідного інформаційного регістра, одиничні виходи основних тригерів розподільника імпульсів з'єднані з входами вентилів запису одиниці допоміжних тригерів тих же розрядів, нульові виходи основних тригерів розподільника імпульсів з'єднані з входами вентилів запису нулів допоміжних тригерів тих же розрядів, одиничні виходи допоміжних тригерів кожного розряду з'єднані з входами вентилів запису нуля основних тригерів свого розряду і з входами вентилів запису одиниці наступного розряду основних тригерів, другі входи вентилів запису нулів і одиниць допоміжних тригерів з'єднані з однією із шин системи тактових імпульсів, яка відрізняється тим, що одиничний вихід додаткового тригера регістра керування з'єднаний із входами вентилів запису одиниці і нуля основних тригерів розподільника імпульсів.

Текст

Регістрова пам'ять, що містить інформаційні регістри, виконані на тригерах, з'єднаних послідовно через вентилі запису нуля й одиниці, інші входи цих вентилів відповідно з'єднані із шиною першої й другої системи тактових імпульсів, а також регістр керування, одиничні виходи тригерів якого відповідно з'єднані з вентилями запису нуля й одиниці тригерів інформаційних регістрів, крім перших тригерів прийому вхідної інформації, і з вентилями запису одиниці тригерів регістра керування; тригер керування регістром керування, нульовий вихід якого з'єднаний із входами вентилів запису одиниці тригерів регістра керування, а одиничний вихід його з'єднаний із входами вентилів запису нуля тих же тригерів, входи вентилів запису нуля й одиниці цих тригерів також з'єднані із системою тактових імпульсів, нульові виходи наступного тригера регістра керування з'єднані з входами вентилів запису нуля попереднього тригера, нульовий вихід першого тригера регістра керування з'єднаний із входом вентиля запису нуля тригера керування регістром керування; додатковий тригер регістра керування з'єднаний з вентилями запису нуля й одиниці, причому входи вентиля запису одиниці з'єднані з одиничним ви Корисна модель відноситься до обчислювальної техніки і може бути використана при побудові перетворювачів кодів, контролерів синхронного прийому послідовного коду. Відомі перетворювачі кодів при побудові контролерів синхроної послідовної передачі кодів [1]. Невід'ємною частиною таких контролерів є здвиговий регістр і лічильник тактів. Існують пристрої, що дозволяють при збереженні швидкодії, сполучити операцію здвигу і рахунку тактів в одному пристрої [2]. ходом тригера керування регістром керування, нульовим виходом другого тригера регістра керування, входи вентиля запису нуля з'єднані з нульовим виходом тригера керування регістром керування, нульовим виходом другого тригера регістра керування, інші входи вентилів з'єднані з однією із шин системи тактових імпульсів, розподільник імпульсів з основними і допоміжними тригерами, одиничні виходи основних тригерів з'єднані з вентилями запису нуля й одиниці перших тригерів інформаційних регістрів, інші входи цих вентилів з'єднані з інформаційними шинами вхідного парафазного коду, а одиничні виходи допоміжних тригерів розподільника імпульсів з'єднані з входами вентилів запису нуля й одиниці інших тригерів відповідного інформаційного регістра, одиничні виходи основних тригерів розподільника імпульсів з'єднані з входами вентилів запису одиниці допоміжних тригерів тих же розрядів, нульові виходи основних тригерів розподільника імпульсів з'єднані з входами вентилів запису нулів допоміжних тригерів тих же розрядів, одиничні виходи допоміжних тригерів кожного розряду з'єднані з входами вентилів запису нуля основних тригерів свого розряду і з входами вентилів запису одиниці наступного розряду основних тригерів, другі входи вентилів запису нулів і одиниць допоміжних тригерів з'єднані з однією із шин системи тактових імпульсів, яка відрізняється тим, що одиничний вихід додаткового тригера регістра керування з'єднаний із входами вентилів запису одиниці і нуля основних тригерів розподільника імпульсів. Аналогічна задача вирішена в пристрої [3], що обраний як прототип. Регістр керування в цьому пристрої розподіляє вхідну інформацію між інформаційними регістрами з одночасним відліком часу. Існуючий пристрій не дозволяє визначити момент прийому останнього розряду прийнятого коду, що не дозволяє здійснити каскадне з'єднання пристроїв. В основу корисної моделі поставлена задача реалізації каскадного з'єднання, що дозволить здійснити подальшу економію устаткування. со Ю Ю О) Фіг. 2 і. т J і 5. у г "Ги гт і "З З [З 6. 3. "Г .. J 2 І 1 І 1 І 2 ї Р] J t 1 І 7. -4 і 2 25 T18 T29 t Ф г 3 25 26 26 t Фіг. З t Фіг. 4 П П П П П П П П П П П П П П П П П П П П П П П П П П П П П П П П "T-X""' F'X r>C7">rT">ri'JX>

ДивитисяДодаткова інформація

Назва патенту англійськоюRegister memory unit

Автори англійськоюTeslenko-Ponomarenko Valentyn Pavlovych

Назва патенту російськоюРегистровое запоминающее устройство

Автори російськоюТесленко-Пономаренко Валентин Павлович

МПК / Мітки

МПК: G11C 19/00, G11C 7/00

Мітки: пам'ять, регістрова

Код посилання

<a href="https://ua.patents.su/2-5547-registrova-pamyat.html" target="_blank" rel="follow" title="База патентів України">Регістрова пам’ять</a>

Попередній патент: Зонд для інтубації тонкої кишки

Наступний патент: Трансформований тенісний стіл з контрольним пристроєм

Випадковий патент: Головний блок ракети