Система ідентифікації та відповідач для системи ідентифікації

Номер патенту: 37182

Опубліковано: 15.05.2001

Формула / Реферат

1. Система идентификации, содержащая запросчик, включающий устройство передачи сигнала запроса к ответчику, устройство приема сигнала ответа от ответчика и процессор для идентификации ответчика по данным, содержащимся в сигнале ответа, и множество ответчиков, каждый из которых содержит устройство для приема сигнала запроса, генератор синхронизирующих импульсов ответчика, генератор кода, передатчик и модулятор, подсоединенный к генератору кода с возможностью передачи ответчиком сигнала ответа, содержащего данные, идентифицирующие ответчик при приеме сигнала запроса, причем запросчик выполен с возможностью обнаружения успешного приема сигнала ответа от любого ответчика, отличающаяся тем, что она содержит устройство выделения синхросигнала ответчика из его сигнала ответа и модификации сигнала запроса синхронно с сигналом ответа с указанием на успешный прием сигнала ответа, причем каждый ответчик содержит устройство выявления модификации сигнала запроса с прекращением передачи своего сигнала ответа.

2. Система идентификации по п. 1, отличающаяся тем, что устройство выделения синхросигнала ответчика из сигнала ответа осуществляет синхронизацию модификации сигнала запроса с сигналом ответа от ответчика.

3. Система идентификации по п. 2, отличающаяся тем, что устройство выделения синхросигнала выполнено с возможностью формирования сигнала псевдосинхронизации ответчика, частота которого задана частотой выделенного сигнала синхронизации ответчика.

4. Система идентификации по п. 3, отличающаяся тем, что устройство выделения синхросигнала содержит управляемый напряжением генератор генерирования сигнала псевдосинхронизации ответчика и устройство текущего контроля выделенного сигнала синхронизации, соединенное с генератором, управляемым напряжением, с поддержанием постоянной частоты сигнала псевдосинхронизации ответчика при отсутствии выделенного сигнала синхронизации ответчика.

5. Система идентификации по п. 4, отличающаяся тем, что запросчик содержит устройство формирования опорного напряжения, соединенное с генератором, управляемым напряжением, и выполненное с возможностью формирования начального значения опорного напряжения в зависимости от кода синхронизации в сигнале ответа ответчика при его приеме.

6. Система идентификации по п. 5, отличающаяся тем, что устройство формирования опорного напряжения генерирует пилообразное напряжение, максимальное значение которого связано с длительностью бита синхронизации в сигнале ответа ответчика.

7. Система идентификации по любому из п п. 2 - 6, отличающаяся тем, что запросчик модифицирует сигнал запроса для первого заранее установленного числа периодов синхросигнала ответчика и для второго заранее установленного числа периодов синхросигнала ответчика после успешного приема запросчиком сигнала ответа от ответчика.

8. Система идентификации по п. 7, отличающаяся тем, что сигнал запроса модифицирован прерыванием.

9. Система идентификации по п. 7 или 8, отличающаяся тем, что ответчик содержит логические схемы текущего контроля модификации сигнала запроса, вызывающие прекращение передачи ответчиком своего сигнала ответа только в том случае, если продолжительность модификации сигнала запроса связана с продолжительностью заранее заданного числа периодов синхросигнала ответчика.

10. Система идентификации по п. 9, отличающаяся тем, что логические схемы ответчика осуществляют текущий контроль модификации сигнала запроса в пределах интервала времени, соответствующего одному периоду синхросигнала запросчика.

11. Система идентификации по любому из п п. 7 - 10, отличающаяся тем, что запросчик осуществляет по меньшей мере вторую модификацию сигнала запроса для третьего заранее установленного числа периодов синхросигнала ответчика и для четвертого заранее установленного числа периодов синхросигнала ответчика после успешного приема запросчиком сигнала ответа от ответчика.

12. Система идентификации по п. 11, отличающаяся тем, что ответчик содержит управляющее устройство, осуществляющее выявление второй модификации сигнала запроса и блокировку ответчика на заранее установленное время после прекращения приема им сигнала запроса.

13. Система идентификации по п. 12, отличающаяся тем, что она содержит определяющую заранее установленное время схему синхронизации, содержащую устройство накопления зарядов, получающее заряд энергии от сигнала запроса и разряжающееся с регулируемой скоростью после прекращения приема сигнала запроса.

14. Система идентификации по любому из пп. 1 - 13, отличающаяся тем, что модификация сигнала запроса состоит в переходе, происходящем с регулируемой скоростью.

15. Система идентификации по п. 1, отличающаяся тем, что устройство выявления модификации сигнала запроса блокирует ответчик на заранее установленный интервал времени.

16. Ответчик для системы идентификации, содержащий устройство приема сигнала запроса, генератор синхронизирующих импульсов ответчика, генератор кода, передатчик и модулятор, подсоединенный к генератору кода с возможностью передачи ответчиком сигнала ответа, содержащего данные, идентифицирующие ответчик при приеме сигнала запроса, отличающийся тем, что он также содержит устройство выявления модификации сигнала запроса, принимаемого от запросчика, прерывающее передачу сигнала ответа, причем модифицированный сигнал синхронизирован сигналом ответа и указывает на успешную идентификацию запросчиком ответчика по его сигналу ответа.

17. Ответчик по п. 16, отличающийся тем, что он содержит логическую схему текущего контроля модификации сигнала запроса, вызывающую прекращение передачи ответчиком сигнала ответа только в том случае, если продолжительность модификации

сигнала запроса связана с продолжительностью заранее заданного числа периодов синхросигнала ответчика.

18. Ответчик по п. 17, отличающийся тем, что логическая схема ответчика осуществляет текущий контроль модификации сигнала запроса в пределах интервала времени, соответствующего одному периоду синхросигнала запросчика.

19. Ответчик по любому из п п. 16 - 18, отличающийся тем, что устройство выявления модификации сигнала запроса блокирует ответчик на заранее установленный интервал времени.

20. Ответчик по любому из п п. 16 - 19, отличающийся тем, что он содержит управляющее устройство, осуществляющее выявление второй модификации сигнала запроса и блокировку ответчика на заранее установленное время после прекращения приема им сигнала запроса.

21. Ответчик по п. 19 или 20, отличающийся тем, что он содержит определяющую заранее установленное время схему синхронизации, содержащую устройство накопления зарядов, получающее заряд энергии от сигнала запроса и разряжающееся с регулируемой скоростью после прекращения приема сигнала запроса.

Текст

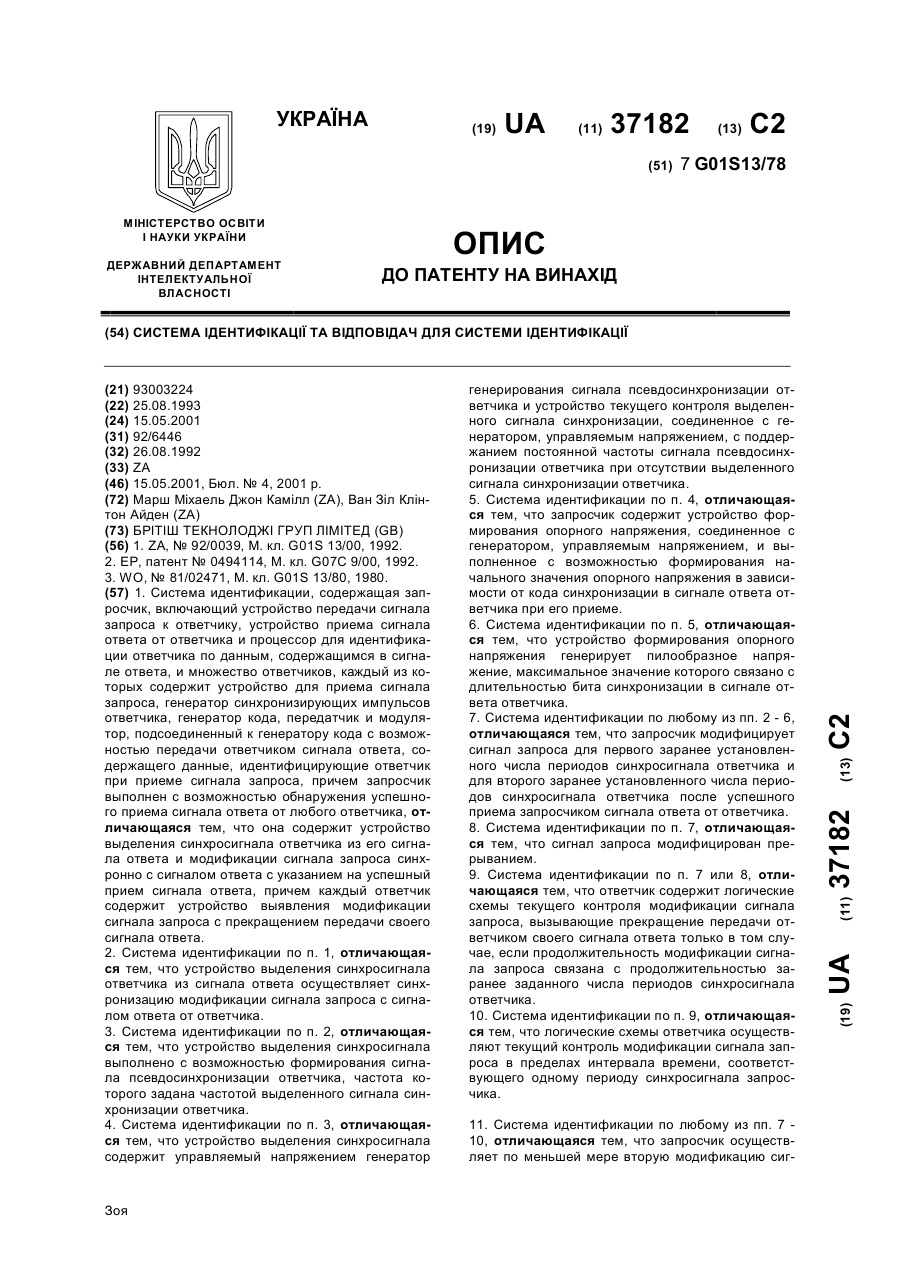

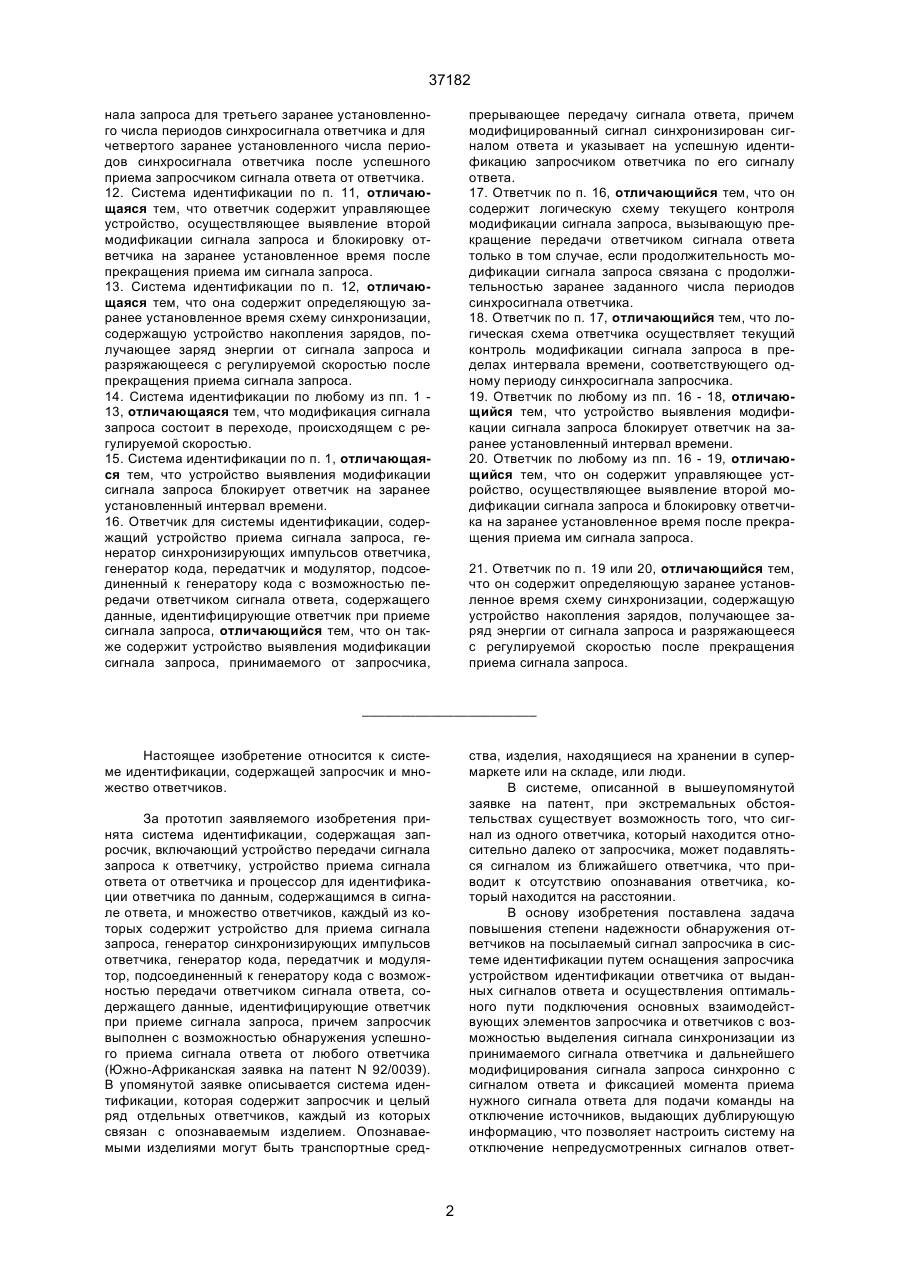

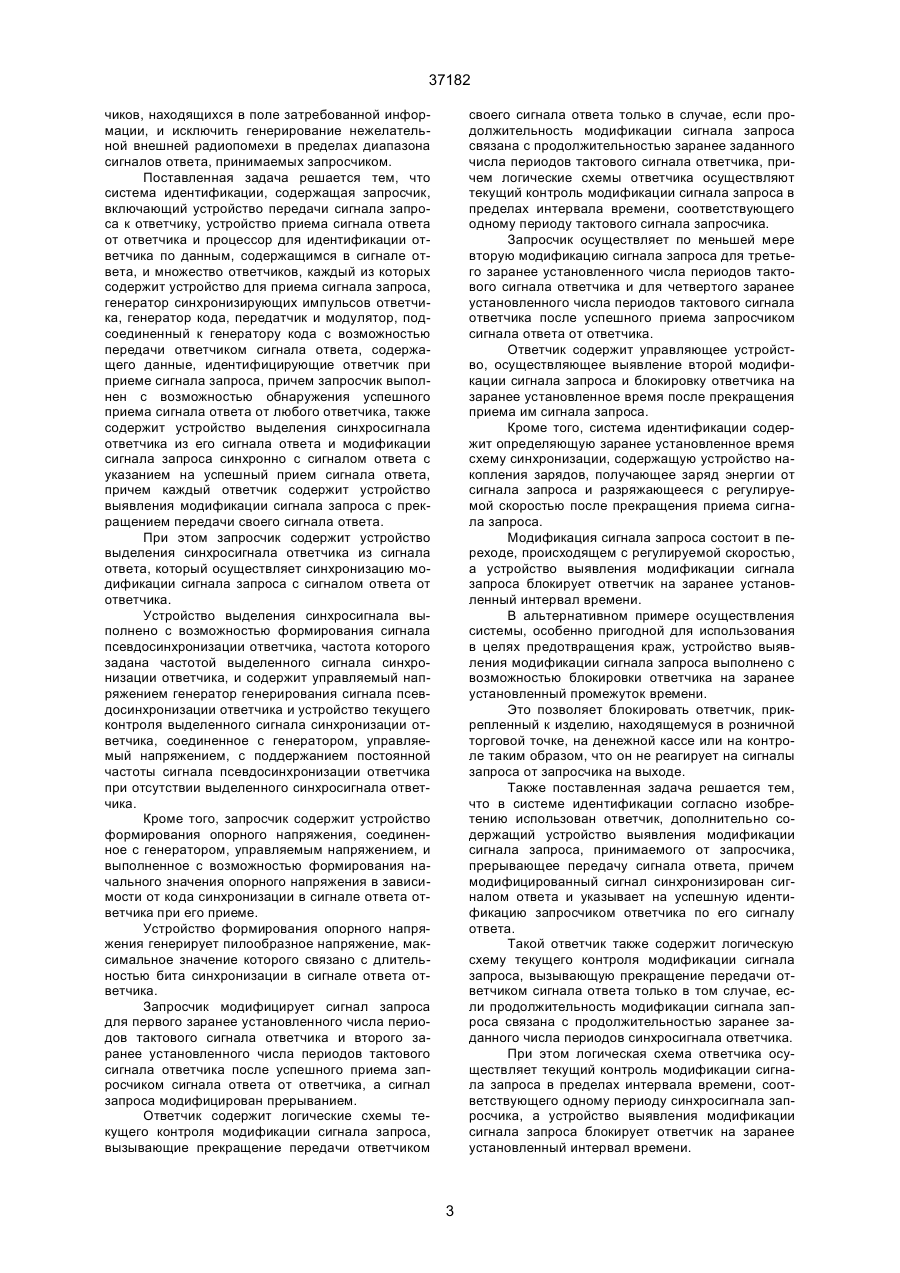

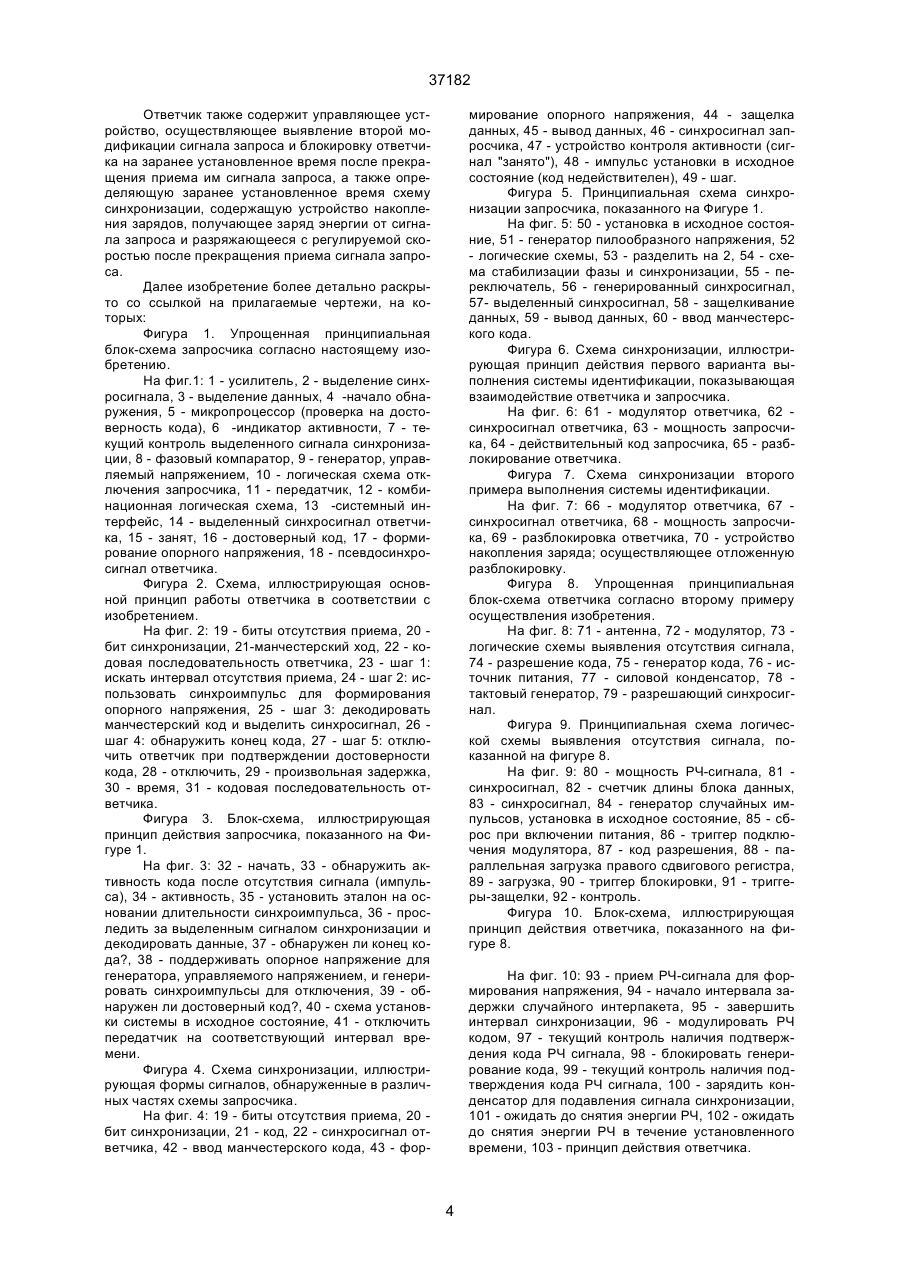

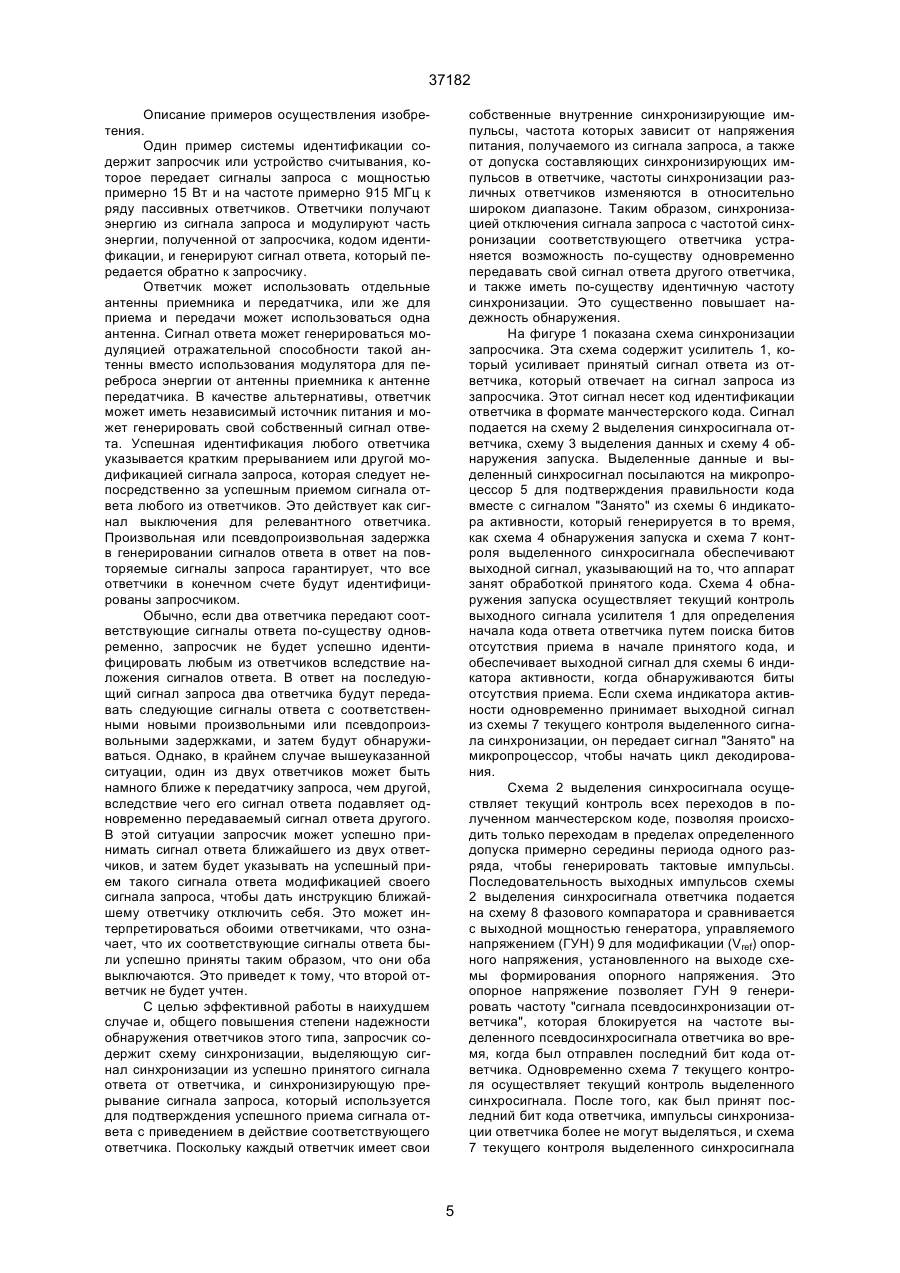

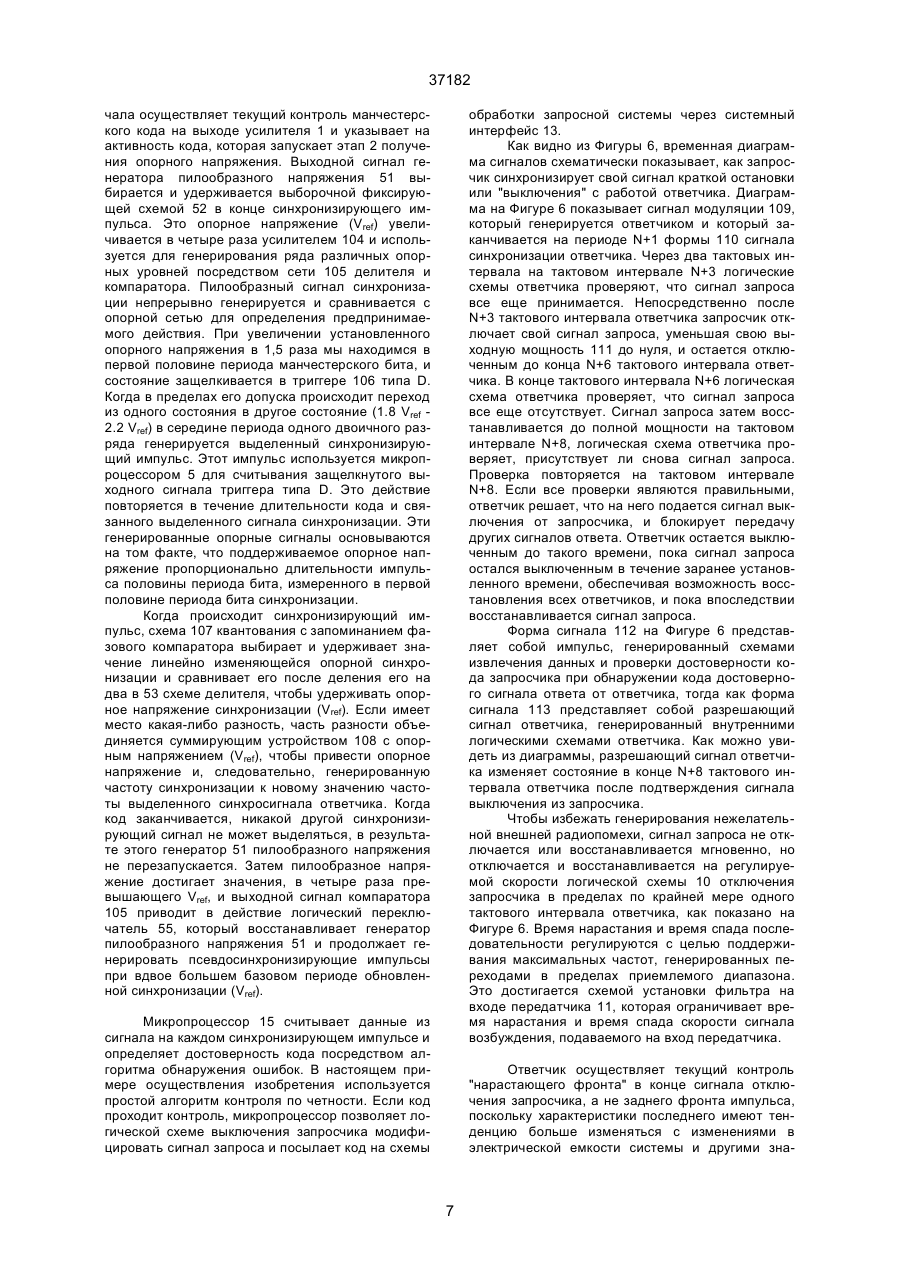

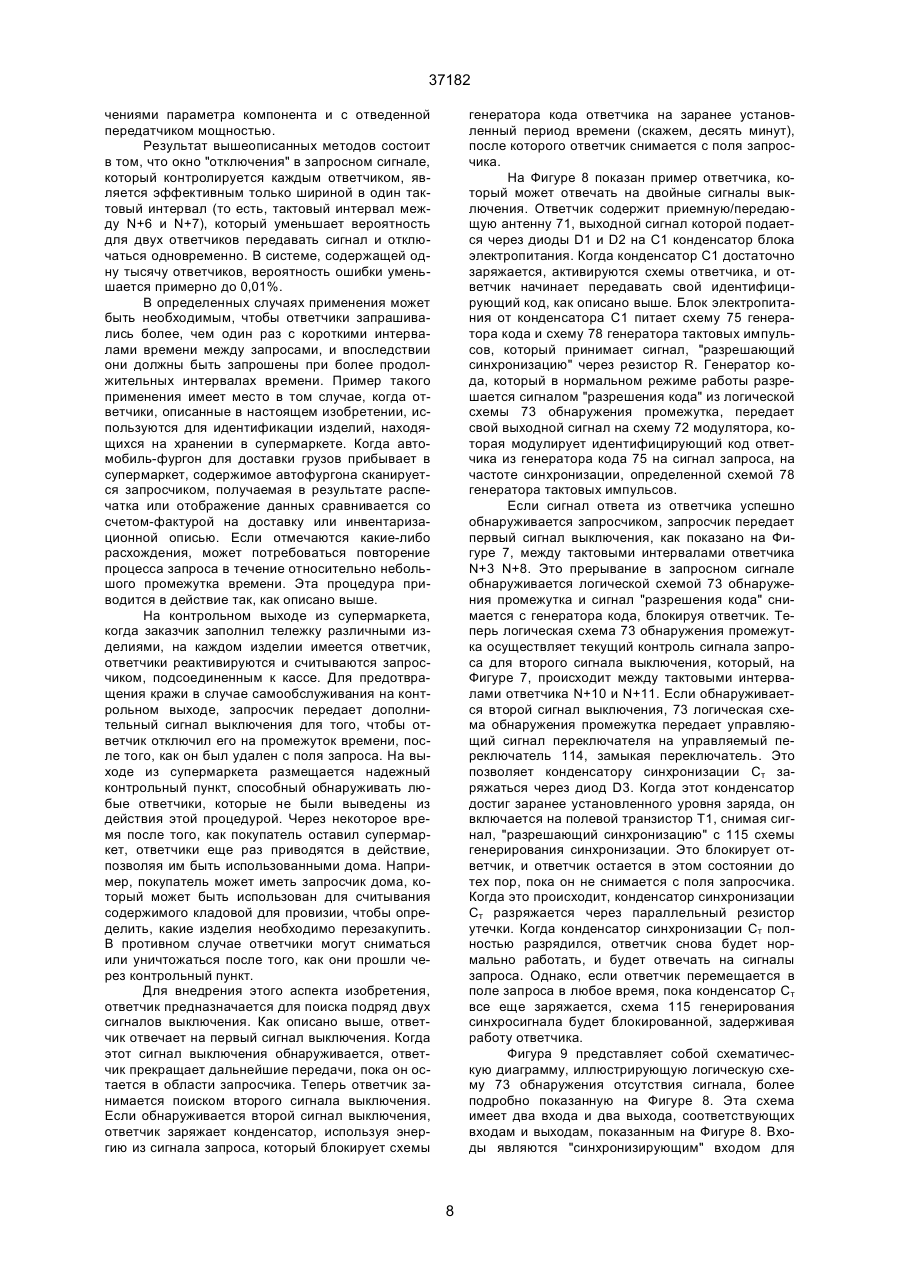

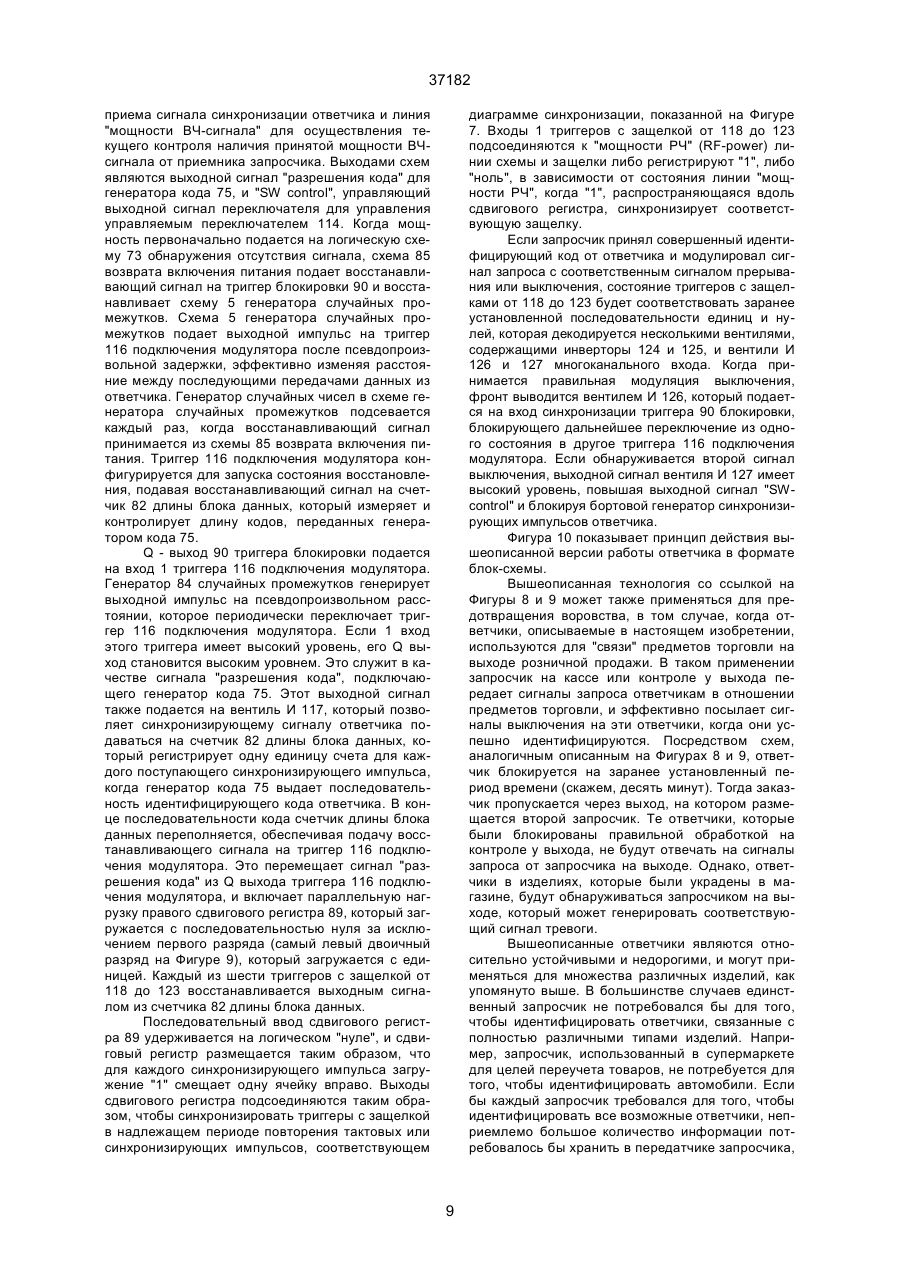

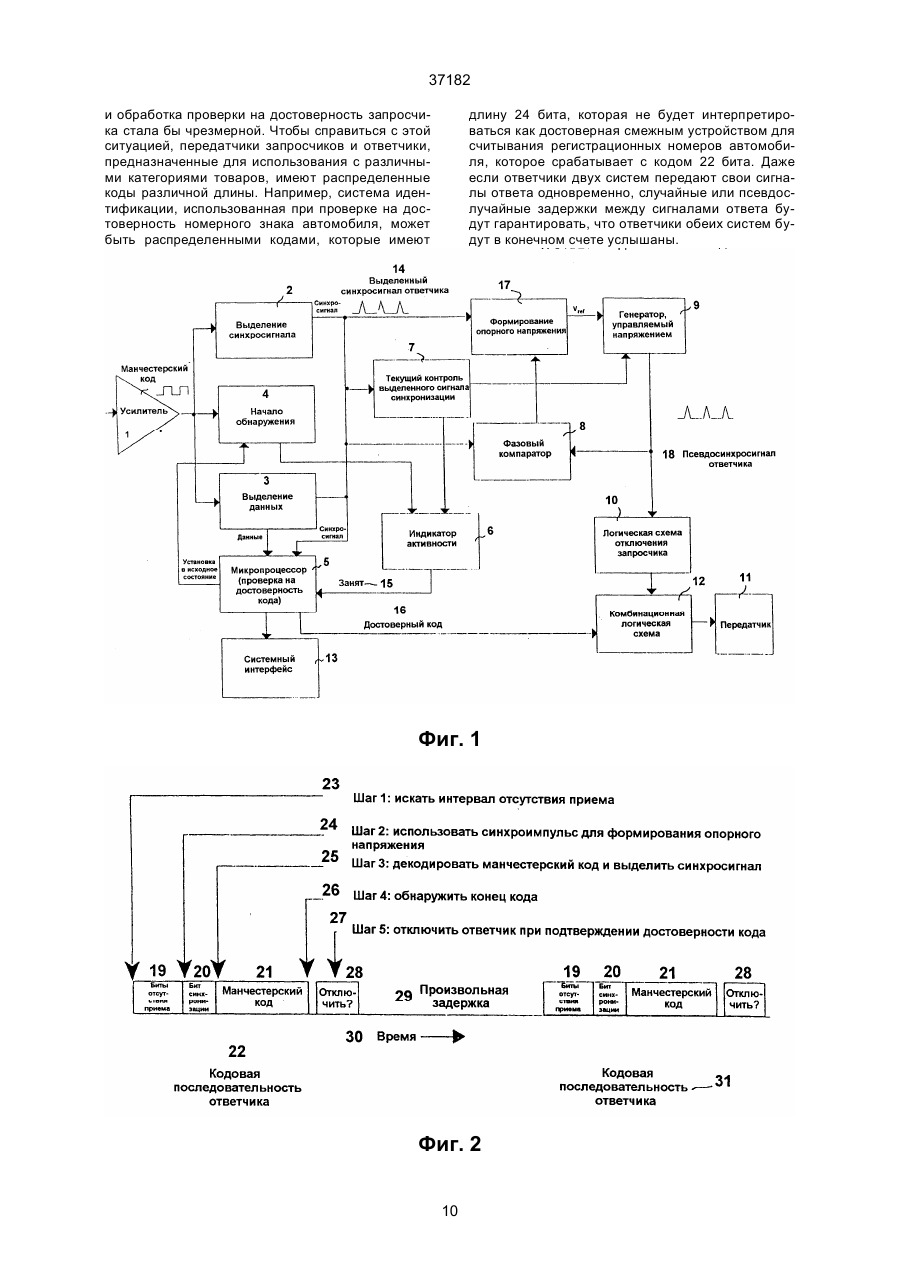

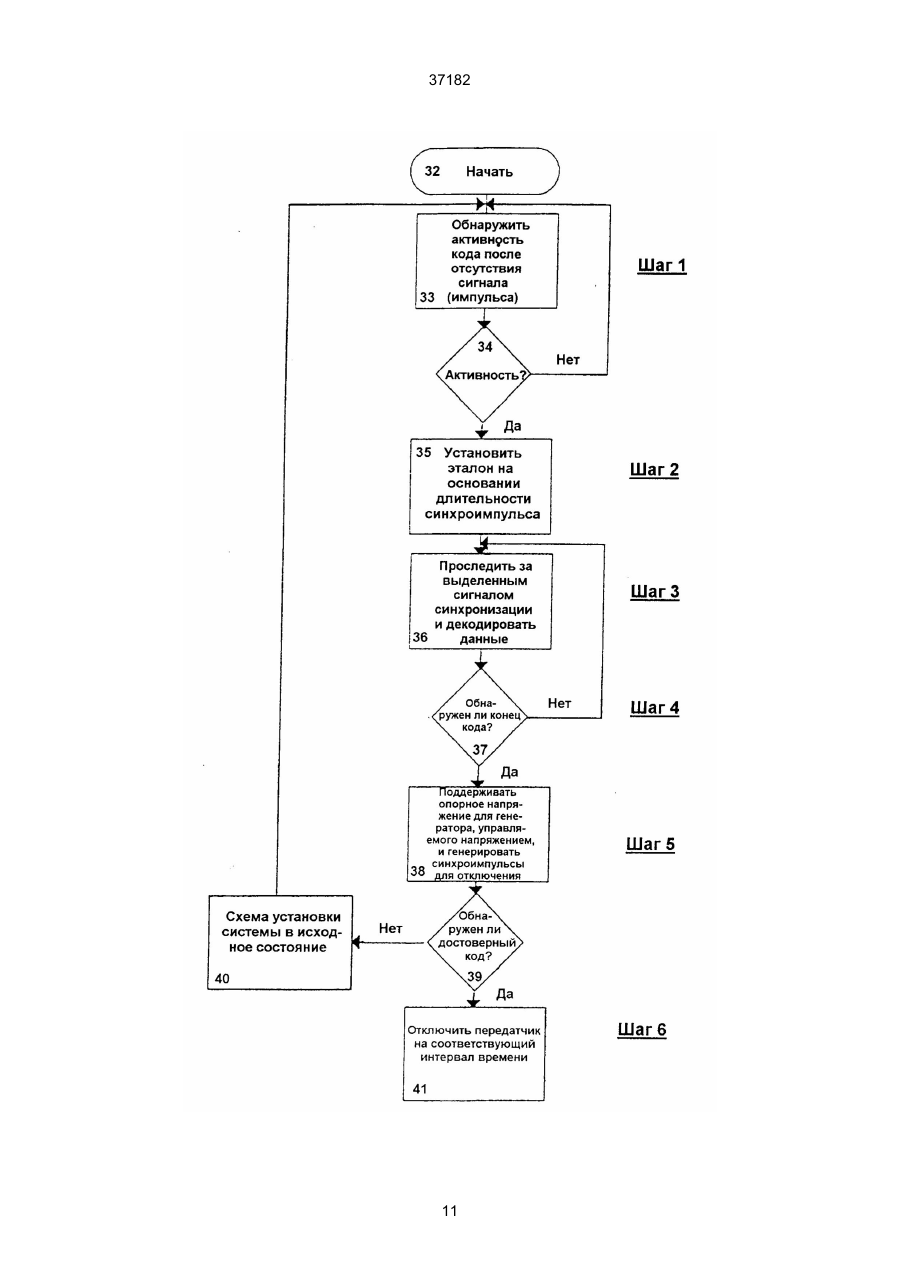

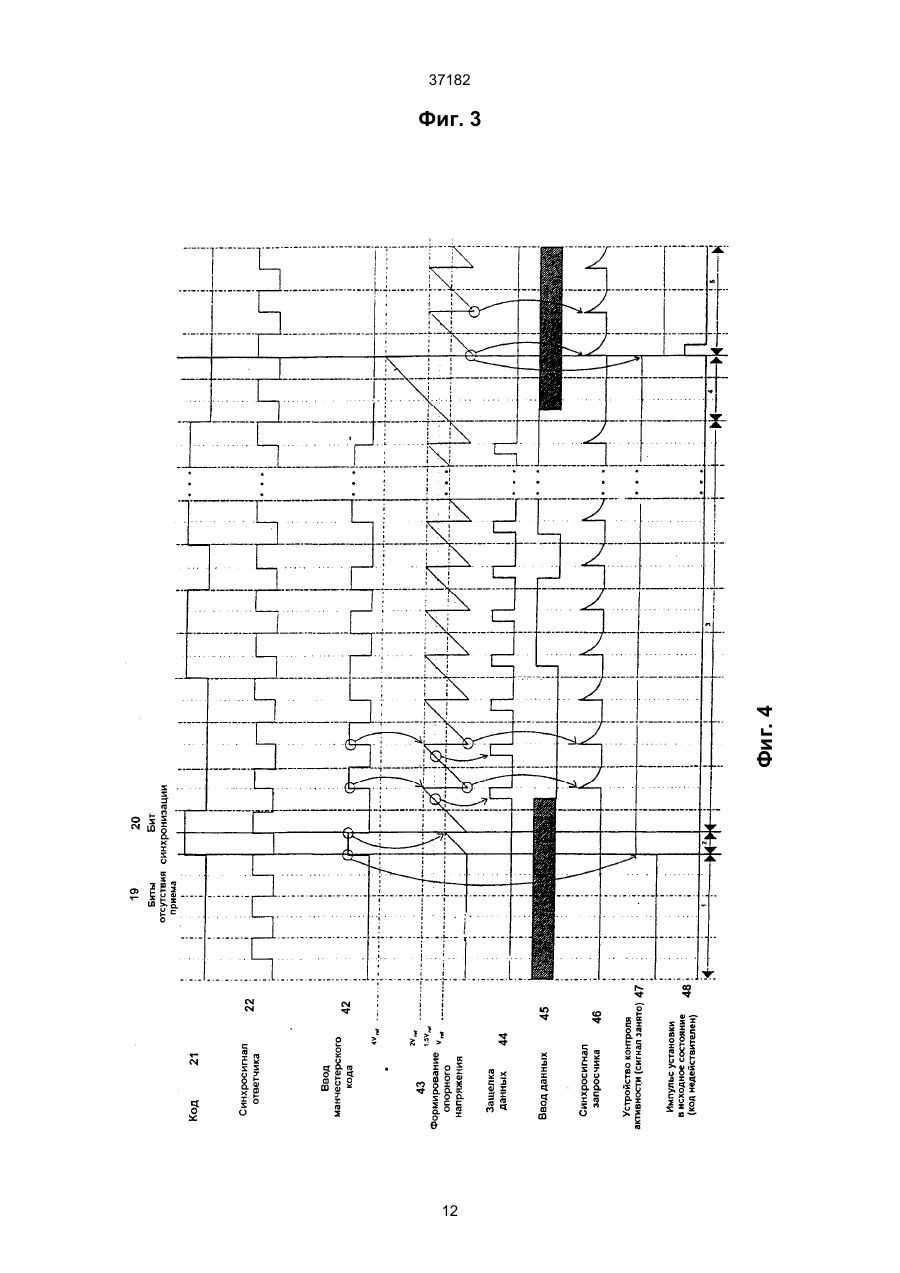

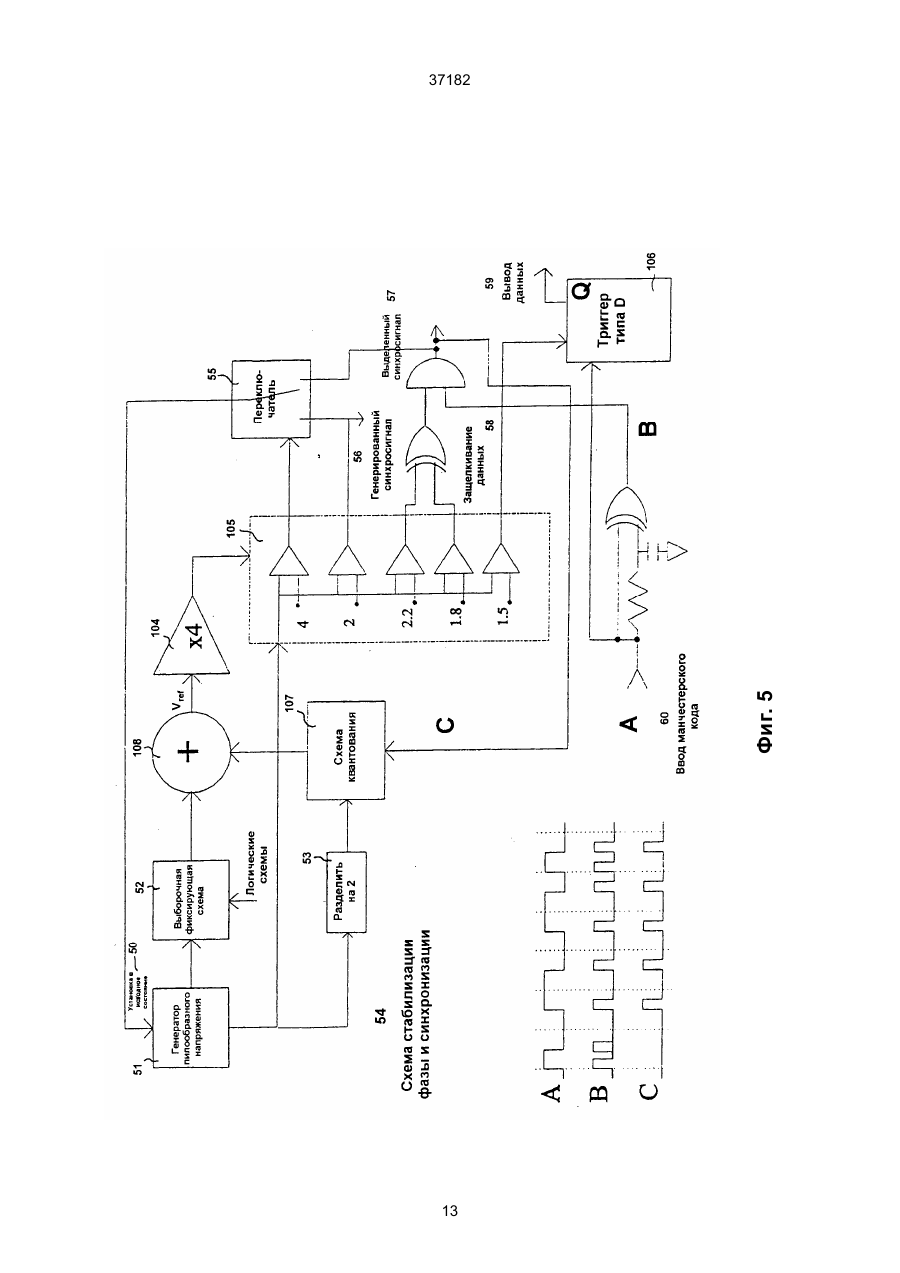

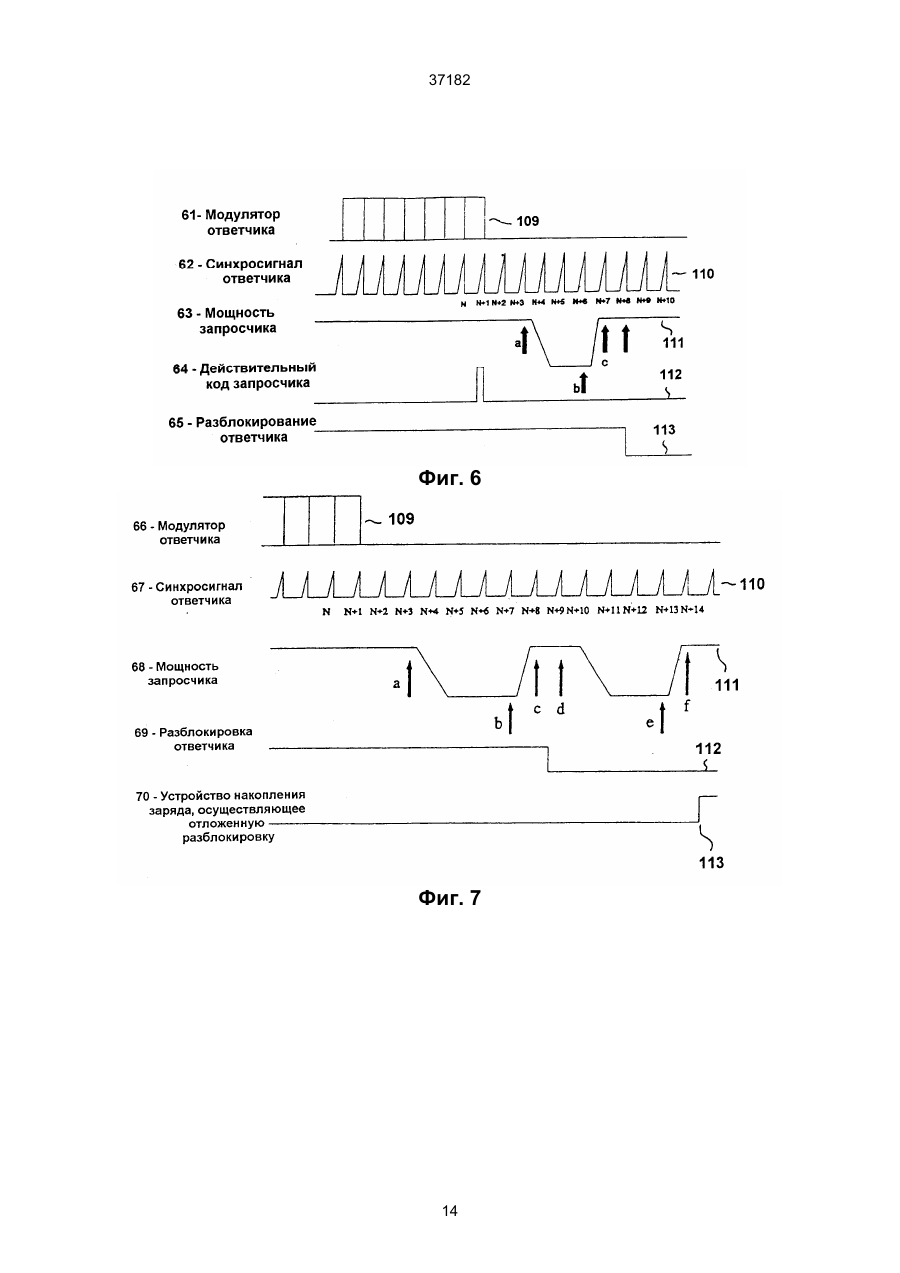

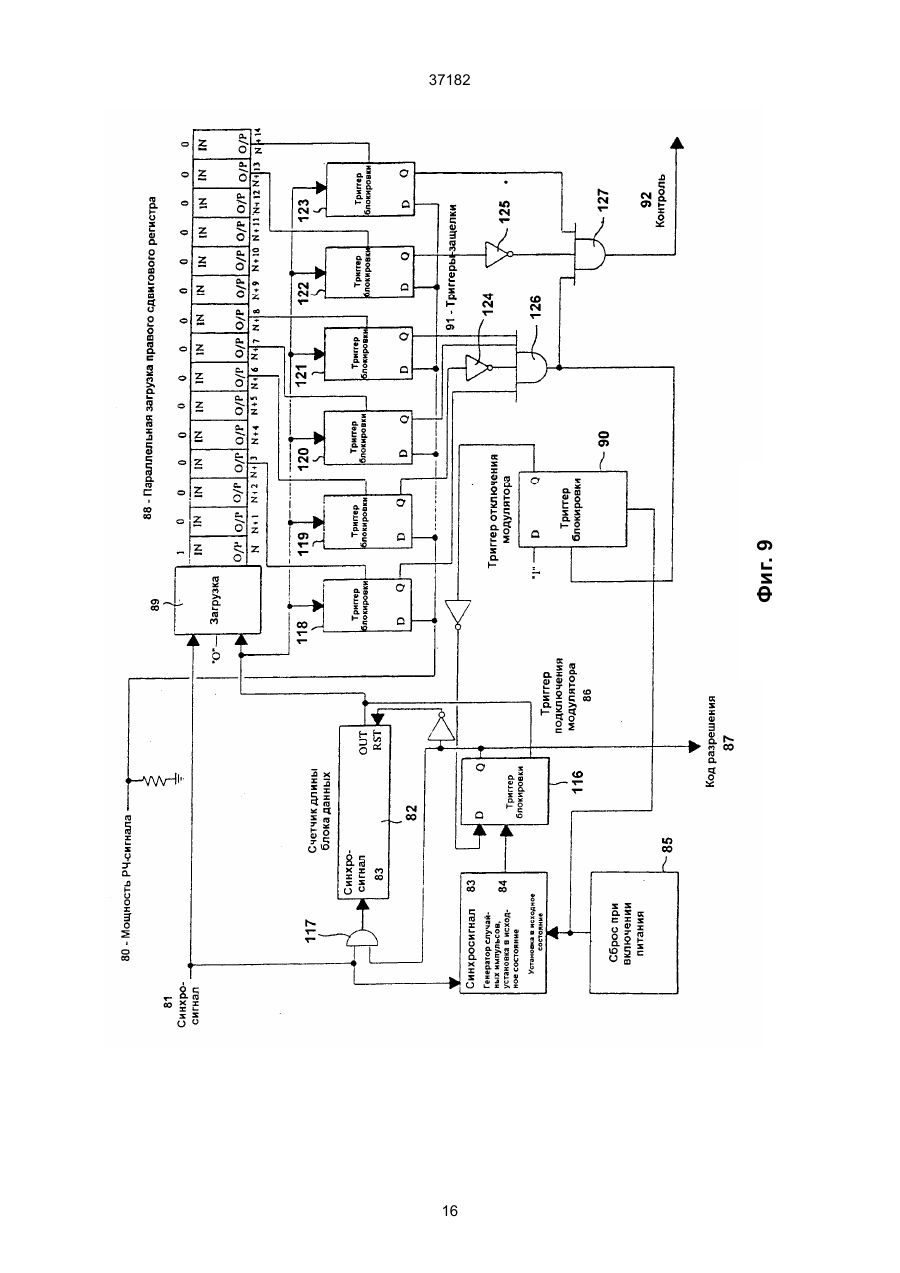

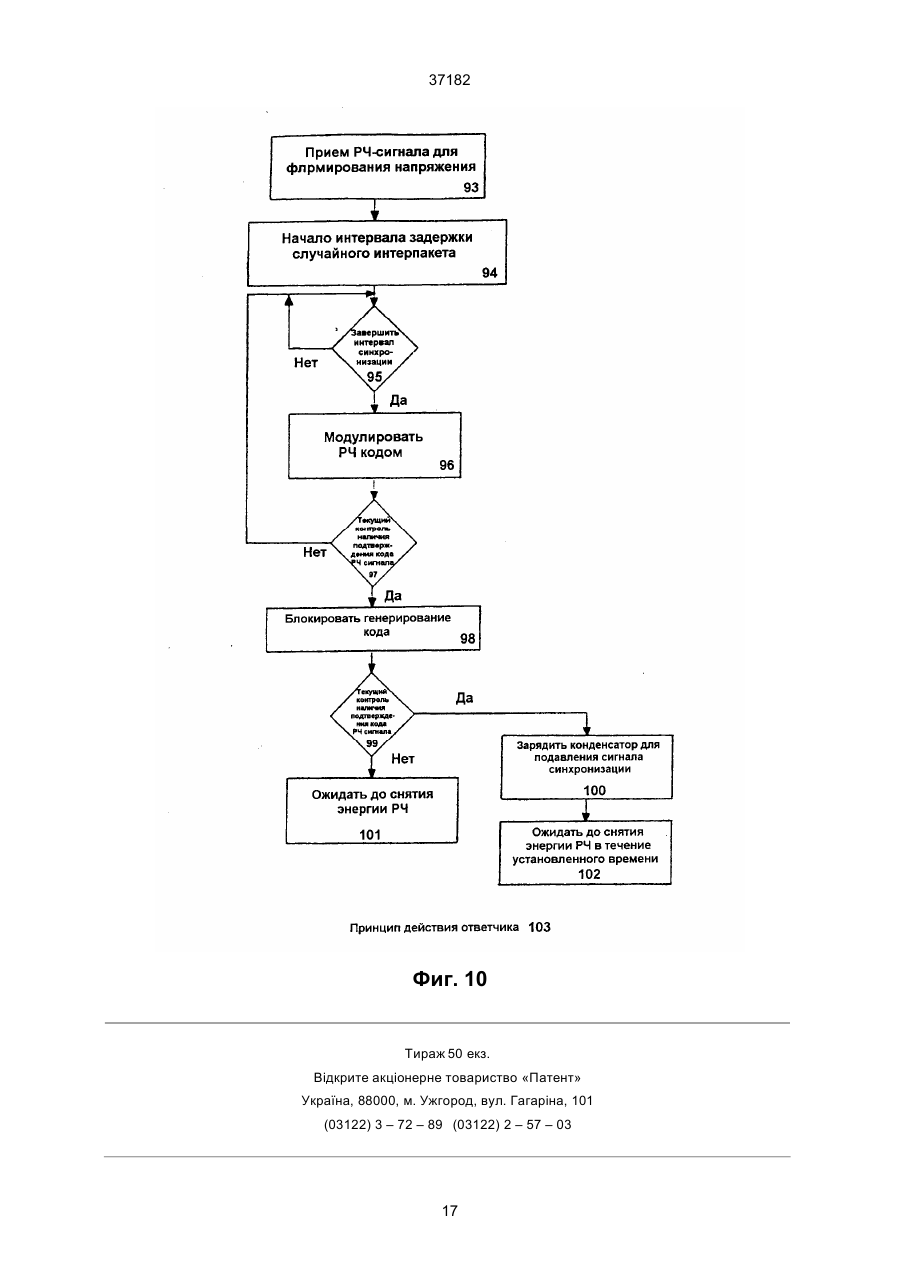

1. Система идентификации, содержащая запросчик, включающий устройство передачи сигнала запроса к ответчику, устройство приема сигнала ответа от ответчика и процессор для идентификации ответчика по данным, содержащимся в сигнале ответа, и множество ответчиков, каждый из которых содержит устройство для приема сигнала запроса, генератор синхронизирующих импульсов ответчика, генератор кода, передатчик и модулятор, подсоединенный к генератору кода с возможностью передачи ответчиком сигнала ответа, содержащего данные, идентифицирующие ответчик при приеме сигнала запроса, причем запросчик выполнен с возможностью обнаружения успешного приема сигнала ответа от любого ответчика, отличающаяся тем, что она содержит устройство выделения синхросигнала ответчика из его сигнала ответа и модификации сигнала запроса синхронно с сигналом ответа с указанием на успешный прием сигнала ответа, причем каждый ответчик содержит устройство выявления модификации сигнала запроса с прекращением передачи своего сигнала ответа. 2. Система идентификации по п. 1, отличающаяся тем, что устройство выделения синхросигнала ответчика из сигнала ответа осуществляет синхронизацию модификации сигнала запроса с сигналом ответа от ответчика. 3. Система идентификации по п. 2, отличающаяся тем, что устройство выделения синхросигнала выполнено с возможностью формирования сигнала псевдосинхронизации ответчика, частота которого задана частотой выделенного сигнала синхронизации ответчика. 4. Система идентификации по п. 3, отличающаяся тем, что устройство выделения синхросигнала содержит управляемый напряжением генератор C2 (54) СИСТЕМА IДЕНТИФIКАЦIЇ ТА ВIДПОВIДАЧ ДЛЯ СИСТЕМИ IДЕНТИФIКАЦIЇ 37182 нала запроса для третьего заранее установленного числа периодов синхросигнала ответчика и для четвертого заранее установленного числа периодов синхросигнала ответчика после успешного приема запросчиком сигнала ответа от ответчика. 12. Система идентификации по п. 11, отличающаяся тем, что ответчик содержит управляющее устройство, осуществляющее выявление второй модификации сигнала запроса и блокировку ответчика на заранее установленное время после прекращения приема им сигнала запроса. 13. Система идентификации по п. 12, отличающаяся тем, что она содержит определяющую заранее установленное время схему синхронизации, содержащую устройство накопления зарядов, получающее заряд энергии от сигнала запроса и разряжающееся с регулируемой скоростью после прекращения приема сигнала запроса. 14. Система идентификации по любому из пп. 1 13, отличающаяся тем, что модификация сигнала запроса состоит в переходе, происходящем с регулируемой скоростью. 15. Система идентификации по п. 1, отличающаяся тем, что устройство выявления модификации сигнала запроса блокирует ответчик на заранее установленный интервал времени. 16. Ответчик для системы идентификации, содержащий устройство приема сигнала запроса, генератор синхронизирующих импульсов ответчика, генератор кода, передатчик и модулятор, подсоединенный к генератору кода с возможностью передачи ответчиком сигнала ответа, содержащего данные, идентифицирующие ответчик при приеме сигнала запроса, отличающийся тем, что он также содержит устройство выявления модификации сигнала запроса, принимаемого от запросчика, прерывающее передачу сигнала ответа, причем модифицированный сигнал синхронизирован сигналом ответа и указывает на успешную идентификацию запросчиком ответчика по его сигналу ответа. 17. Ответчик по п. 16, отличающийся тем, что он содержит логическую схему текущего контроля модификации сигнала запроса, вызывающую прекращение передачи ответчиком сигнала ответа только в том случае, если продолжительность модификации сигнала запроса связана с продолжительностью заранее заданного числа периодов синхросигнала ответчика. 18. Ответчик по п. 17, отличающийся тем, что логическая схема ответчика осуществляет текущий контроль модификации сигнала запроса в пределах интервала времени, соответствующего одному периоду синхросигнала запросчика. 19. Ответчик по любому из пп. 16 - 18, отличающийся тем, что устройство выявления модификации сигнала запроса блокирует ответчик на заранее установленный интервал времени. 20. Ответчик по любому из пп. 16 - 19, отличающийся тем, что он содержит управляющее устройство, осуществляющее выявление второй модификации сигнала запроса и блокировку ответчика на заранее установленное время после прекращения приема им сигнала запроса. 21. Ответчик по п. 19 или 20, отличающийся тем, что он содержит определяющую заранее установленное время схему синхронизации, содержащую устройство накопления зарядов, получающее заряд энергии от сигнала запроса и разряжающееся с регулируемой скоростью после прекращения приема сигнала запроса. _______________________ ства, изделия, находящиеся на хранении в супермаркете или на складе, или люди. В системе, описанной в вышеупомянутой заявке на патент, при экстремальных обстоятельствах существует возможность того, что сигнал из одного ответчика, который находится относительно далеко от запросчика, может подавляться сигналом из ближайшего ответчика, что приводит к отсутствию опознавания ответчика, который находится на расстоянии. В основу изобретения поставлена задача повышения степени надежности обнаружения ответчиков на посылаемый сигнал запросчика в системе идентификации путем оснащения запросчика устройством идентификации ответчика от выданных сигналов ответа и осуществления оптимального пути подключения основных взаимодействующих элементов запросчика и ответчиков с возможностью выделения сигнала синхронизации из принимаемого сигнала ответчика и дальнейшего модифицирования сигнала запроса синхронно с сигналом ответа и фиксацией момента приема нужного сигнала ответа для подачи команды на отключение источников, выдающих дублирующую информацию, что позволяет настроить систему на отключение непредусмотренных сигналов ответ Настоящее изобретение относится к системе идентификации, содержащей запросчик и множество ответчиков. За прототип заявляемого изобретения принята система идентификации, содержащая запросчик, включающий устройство передачи сигнала запроса к ответчику, устройство приема сигнала ответа от ответчика и процессор для идентификации ответчика по данным, содержащимся в сигнале ответа, и множество ответчиков, каждый из которых содержит устройство для приема сигнала запроса, генератор синхронизирующих импульсов ответчика, генератор кода, передатчик и модулятор, подсоединенный к генератору кода с возможностью передачи ответчиком сигнала ответа, содержащего данные, идентифицирующие ответчик при приеме сигнала запроса, причем запросчик выполнен с возможностью обнаружения успешного приема сигнала ответа от любого ответчика (Южно-Африканская заявка на патент N 92/0039). В упомянутой заявке описывается система идентификации, которая содержит запросчик и целый ряд отдельных ответчиков, каждый из которых связан с опознаваемым изделием. Опознаваемыми изделиями могут быть транспортные сред 2 37182 чиков, находящихся в поле затребованной информации, и исключить генерирование нежелательной внешней радиопомехи в пределах диапазона сигналов ответа, принимаемых запросчиком. Поставленная задача решается тем, что система идентификации, содержащая запросчик, включающий устройство передачи сигнала запроса к ответчику, устройство приема сигнала ответа от ответчика и процессор для идентификации ответчика по данным, содержащимся в сигнале ответа, и множество ответчиков, каждый из которых содержит устройство для приема сигнала запроса, генератор синхронизирующих импульсов ответчика, генератор кода, передатчик и модулятор, подсоединенный к генератору кода с возможностью передачи ответчиком сигнала ответа, содержащего данные, идентифицирующие ответчик при приеме сигнала запроса, причем запросчик выполнен с возможностью обнаружения успешного приема сигнала ответа от любого ответчика, также содержит устройство выделения синхросигнала ответчика из его сигнала ответа и модификации сигнала запроса синхронно с сигналом ответа с указанием на успешный прием сигнала ответа, причем каждый ответчик содержит устройство выявления модификации сигнала запроса с прекращением передачи своего сигнала ответа. При этом запросчик содержит устройство выделения синхросигнала ответчика из сигнала ответа, который осуществляет синхронизацию модификации сигнала запроса с сигналом ответа от ответчика. Устройство выделения синхросигнала выполнено с возможностью формирования сигнала псевдосинхронизации ответчика, частота которого задана частотой выделенного сигнала синхронизации ответчика, и содержит управляемый напряжением генератор генерирования сигнала псевдосинхронизации ответчика и устройство текущего контроля выделенного сигнала синхронизации ответчика, соединенное с генератором, управляемый напряжением, с поддержанием постоянной частоты сигнала псевдосинхронизации ответчика при отсутствии выделенного синхросигнала ответчика. Кроме того, запросчик содержит устройство формирования опорного напряжения, соединенное с генератором, управляемым напряжением, и выполненное с возможностью формирования начального значения опорного напряжения в зависимости от кода синхронизации в сигнале ответа ответчика при его приеме. Устройство формирования опорного напряжения генерирует пилообразное напряжение, максимальное значение которого связано с длительностью бита синхронизации в сигнале ответа ответчика. Запросчик модифицирует сигнал запроса для первого заранее установленного числа периодов тактового сигнала ответчика и второго заранее установленного числа периодов тактового сигнала ответчика после успешного приема запросчиком сигнала ответа от ответчика, а сигнал запроса модифицирован прерыванием. Ответчик содержит логические схемы текущего контроля модификации сигнала запроса, вызывающие прекращение передачи ответчиком своего сигнала ответа только в случае, если продолжительность модификации сигнала запроса связана с продолжительностью заранее заданного числа периодов тактового сигнала ответчика, причем логические схемы ответчика осуществляют текущий контроль модификации сигнала запроса в пределах интервала времени, соответствующего одному периоду тактового сигнала запросчика. Запросчик осуществляет по меньшей мере вторую модификацию сигнала запроса для третьего заранее установленного числа периодов тактового сигнала ответчика и для четвертого заранее установленного числа периодов тактового сигнала ответчика после успешного приема запросчиком сигнала ответа от ответчика. Ответчик содержит управляющее устройство, осуществляющее выявление второй модификации сигнала запроса и блокировку ответчика на заранее установленное время после прекращения приема им сигнала запроса. Кроме того, система идентификации содержит определяющую заранее установленное время схему синхронизации, содержащую устройство накопления зарядов, получающее заряд энергии от сигнала запроса и разряжающееся с регулируемой скоростью после прекращения приема сигнала запроса. Модификация сигнала запроса состоит в переходе, происходящем с регулируемой скоростью, а устройство выявления модификации сигнала запроса блокирует ответчик на заранее установленный интервал времени. В альтернативном примере осуществления системы, особенно пригодной для использования в целях предотвращения краж, устройство выявления модификации сигнала запроса выполнено с возможностью блокировки ответчика на заранее установленный промежуток времени. Это позволяет блокировать ответчик, прикрепленный к изделию, находящемуся в розничной торговой точке, на денежной кассе или на контроле таким образом, что он не реагирует на сигналы запроса от запросчика на выходе. Также поставленная задача решается тем, что в системе идентификации согласно изобретению использован ответчик, дополнительно содержащий устройство выявления модификации сигнала запроса, принимаемого от запросчика, прерывающее передачу сигнала ответа, причем модифицированный сигнал синхронизирован сигналом ответа и указывает на успешную идентификацию запросчиком ответчика по его сигналу ответа. Такой ответчик также содержит логическую схему текущего контроля модификации сигнала запроса, вызывающую прекращение передачи ответчиком сигнала ответа только в том случае, если продолжительность модификации сигнала запроса связана с продолжительностью заранее заданного числа периодов синхросигнала ответчика. При этом логическая схема ответчика осуществляет текущий контроль модификации сигнала запроса в пределах интервала времени, соответствующего одному периоду синхросигнала запросчика, а устройство выявления модификации сигнала запроса блокирует ответчик на заранее установленный интервал времени. 3 37182 Ответчик также содержит управляющее устройство, осуществляющее выявление второй модификации сигнала запроса и блокировку ответчика на заранее установленное время после прекращения приема им сигнала запроса, а также определяющую заранее установленное время схему синхронизации, содержащую устройство накопления зарядов, получающее заряд энергии от сигнала запроса и разряжающееся с регулируемой скоростью после прекращения приема сигнала запроса. Далее изобретение более детально раскрыто со ссылкой на прилагаемые чертежи, на которых: Фигура 1. Упрощенная принципиальная блок-схема запросчика согласно настоящему изобретению. На фиг.1: 1 - усилитель, 2 - выделение синхросигнала, 3 - выделение данных, 4 -начало обнаружения, 5 - микропроцессор (проверка на достоверность кода), 6 -индикатор активности, 7 - текущий контроль выделенного сигнала синхронизации, 8 - фазовый компаратор, 9 - генератор, управляемый напряжением, 10 - логическая схема отключения запросчика, 11 - передатчик, 12 - комбинационная логическая схема, 13 -системный интерфейс, 14 - выделенный синхросигнал ответчика, 15 - занят, 16 - достоверный код, 17 - формирование опорного напряжения, 18 - псевдосинхросигнал ответчика. Фигура 2. Схема, иллюстрирующая основной принцип работы ответчика в соответствии с изобретением. На фиг. 2: 19 - биты отсутствия приема, 20 бит синхронизации, 21-манчестерский ход, 22 - кодовая последовательность ответчика, 23 - шаг 1: искать интервал отсутствия приема, 24 - шаг 2: использовать синхроимпульс для формирования опорного напряжения, 25 - шаг 3: декодировать манчестерский код и выделить синхросигнал, 26 шаг 4: обнаружить конец кода, 27 - шаг 5: отключить ответчик при подтверждении достоверности кода, 28 - отключить, 29 - произвольная задержка, 30 - время, 31 - кодовая последовательность ответчика. Фигура 3. Блок-схема, иллюстрирующая принцип действия запросчика, показанного на Фигуре 1. На фиг. 3: 32 - начать, 33 - обнаружить активность кода после отсутствия сигнала (импульса), 34 - активность, 35 - установить эталон на основании длительности синхроимпульса, 36 - проследить за выделенным сигналом синхронизации и декодировать данные, 37 - обнаружен ли конец кода?, 38 - поддерживать опорное напряжение для генератора, управляемого напряжением, и генерировать синхроимпульсы для отключения, 39 - обнаружен ли достоверный код?, 40 - схема установки системы в исходное состояние, 41 - отключить передатчик на соответствующий интервал времени. Фигура 4. Схема синхронизации, иллюстрирующая формы сигналов, обнаруженные в различных частях схемы запросчика. На фиг. 4: 19 - биты отсутствия приема, 20 бит синхронизации, 21 - код, 22 - синхросигнал ответчика, 42 - ввод манчестерского кода, 43 - фор мирование опорного напряжения, 44 - защелка данных, 45 - вывод данных, 46 - синхросигнал запросчика, 47 - устройство контроля активности (сигнал "занято"), 48 - импульс установки в исходное состояние (код недействителен), 49 - шаг. Фигура 5. Принципиальная схема синхронизации запросчика, показанного на Фигуре 1. На фиг. 5: 50 - установка в исходное состояние, 51 - генератор пилообразного напряжения, 52 - логические схемы, 53 - разделить на 2, 54 - схема стабилизации фазы и синхронизации, 55 - переключатель, 56 - генерированный синхросигнал, 57- выделенный синхросигнал, 58 - защелкивание данных, 59 - вывод данных, 60 - ввод манчестерского кода. Фигура 6. Схема синхронизации, иллюстрирующая принцип действия первого варианта выполнения системы идентификации, показывающая взаимодействие ответчика и запросчика. На фиг. 6: 61 - модулятор ответчика, 62 синхросигнал ответчика, 63 - мощность запросчика, 64 - действительный код запросчика, 65 - разблокирование ответчика. Фигура 7. Схема синхронизации второго примера выполнения системы идентификации. На фиг. 7: 66 - модулятор ответчика, 67 синхросигнал ответчика, 68 - мощность запросчика, 69 - разблокировка ответчика, 70 - устройство накопления заряда; осуществляющее отложенную разблокировку. Фигура 8. Упрощенная принципиальная блок-схема ответчика согласно второму примеру осуществления изобретения. На фиг. 8: 71 - антенна, 72 - модулятор, 73 логические схемы выявления отсутствия сигнала, 74 - разрешение кода, 75 - генератор кода, 76 - источник питания, 77 - силовой конденсатор, 78 тактовый генератор, 79 - разрешающий синхросигнал. Фигура 9. Принципиальная схема логической схемы выявления отсутствия сигнала, показанной на фигуре 8. На фиг. 9: 80 - мощность РЧ-сигнала, 81 синхросигнал, 82 - счетчик длины блока данных, 83 - синхросигнал, 84 - генератор случайных импульсов, установка в исходное состояние, 85 - сброс при включении питания, 86 - триггер подключения модулятора, 87 - код разрешения, 88 - параллельная загрузка правого сдвигового регистра, 89 - загрузка, 90 - триггер блокировки, 91 - триггеры-защелки, 92 - контроль. Фигура 10. Блок-схема, иллюстрирующая принцип действия ответчика, показанного на фигуре 8. На фиг. 10: 93 - прием РЧ-сигнала для формирования напряжения, 94 - начало интервала задержки случайного интерпакета, 95 - завершить интервал синхронизации, 96 - модулировать РЧ кодом, 97 - текущий контроль наличия подтверждения кода РЧ сигнала, 98 - блокировать генерирование кода, 99 - текущий контроль наличия подтверждения кода РЧ сигнала, 100 - зарядить конденсатор для подавления сигнала синхронизации, 101 - ожидать до снятия энергии РЧ, 102 - ожидать до снятия энергии РЧ в течение установленного времени, 103 - принцип действия ответчика. 4 37182 Описание примеров осуществления изобретения. Один пример системы идентификации содержит запросчик или устройство считывания, которое передает сигналы запроса с мощностью примерно 15 Вт и на частоте примерно 915 МГц к ряду пассивных ответчиков. Ответчики получают энергию из сигнала запроса и модулируют часть энергии, полученной от запросчика, кодом идентификации, и генерируют сигнал ответа, который передается обратно к запросчику. Ответчик может использовать отдельные антенны приемника и передатчика, или же для приема и передачи может использоваться одна антенна. Сигнал ответа может генерироваться модуляцией отражательной способности такой антенны вместо использования модулятора для переброса энергии от антенны приемника к антенне передатчика. В качестве альтернативы, ответчик может иметь независимый источник питания и может генерировать свой собственный сигнал ответа. Успешная идентификация любого ответчика указывается кратким прерыванием или другой модификацией сигнала запроса, которая следует непосредственно за успешным приемом сигнала ответа любого из ответчиков. Это действует как сигнал выключения для релевантного ответчика. Произвольная или псевдопроизвольная задержка в генерировании сигналов ответа в ответ на повторяемые сигналы запроса гарантирует, что все ответчики в конечном счете будут идентифицированы запросчиком. Обычно, если два ответчика передают соответствующие сигналы ответа по-существу одновременно, запросчик не будет успешно идентифицировать любым из ответчиков вследствие наложения сигналов ответа. В ответ на последующий сигнал запроса два ответчика будут передавать следующие сигналы ответа с соответственными новыми произвольными или псевдопроизвольными задержками, и затем будут обнаруживаться. Однако, в крайнем случае вышеуказанной ситуации, один из двух ответчиков может быть намного ближе к передатчику запроса, чем другой, вследствие чего его сигнал ответа подавляет одновременно передаваемый сигнал ответа другого. В этой ситуации запросчик может успешно принимать сигнал ответа ближайшего из двух ответчиков, и затем будет указывать на успешный прием такого сигнала ответа модификацией своего сигнала запроса, чтобы дать инструкцию ближайшему ответчику отключить себя. Это может интерпретироваться обоими ответчиками, что означает, что их соответствующие сигналы ответа были успешно приняты таким образом, что они оба выключаются. Это приведет к тому, что второй ответчик не будет учтен. С целью эффективной работы в наихудшем случае и, общего повышения степени надежности обнаружения ответчиков этого типа, запросчик содержит схему синхронизации, выделяющую сигнал синхронизации из успешно принятого сигнала ответа от ответчика, и синхронизирующую прерывание сигнала запроса, который используется для подтверждения успешного приема сигнала ответа с приведением в действие соответствующего ответчика. Поскольку каждый ответчик имеет свои собственные внутренние синхронизирующие импульсы, частота которых зависит от напряжения питания, получаемого из сигнала запроса, а также от допуска составляющих синхронизирующих импульсов в ответчике, частоты синхронизации различных ответчиков изменяются в относительно широком диапазоне. Таким образом, синхронизацией отключения сигнала запроса с частотой синхронизации соответствующего ответчика устраняется возможность по-существу одновременно передавать свой сигнал ответа другого ответчика, и также иметь по-существу идентичную частоту синхронизации. Это существенно повышает надежность обнаружения. На фигуре 1 показана схема синхронизации запросчика. Эта схема содержит усилитель 1, который усиливает принятый сигнал ответа из ответчика, который отвечает на сигнал запроса из запросчика. Этот сигнал несет код идентификации ответчика в формате манчестерского кода. Сигнал подается на схему 2 выделения синхросигнала ответчика, схему 3 выделения данных и схему 4 обнаружения запуска. Выделенные данные и выделенный синхросигнал посылаются на микропроцессор 5 для подтверждения правильности кода вместе с сигналом "Занято" из схемы 6 индикатора активности, который генерируется в то время, как схема 4 обнаружения запуска и схема 7 контроля выделенного синхросигнала обеспечивают выходной сигнал, указывающий на то, что аппарат занят обработкой принятого кода. Схема 4 обнаружения запуска осуществляет текущий контроль выходного сигнала усилителя 1 для определения начала кода ответа ответчика путем поиска битов отсутствия приема в начале принятого кода, и обеспечивает выходной сигнал для схемы 6 индикатора активности, когда обнаруживаются биты отсутствия приема. Если схема индикатора активности одновременно принимает выходной сигнал из схемы 7 текущего контроля выделенного сигнала синхронизации, он передает сигнал "Занято" на микропроцессор, чтобы начать цикл декодирования. Схема 2 выделения синхросигнала осуществляет текущий контроль всех переходов в полученном манчестерском коде, позволяя происходить только переходам в пределах определенного допуска примерно середины периода одного разряда, чтобы генерировать тактовые импульсы. Последовательность выходных импульсов схемы 2 выделения синхросигнала ответчика подается на схему 8 фазового компаратора и сравнивается с выходной мощностью генератора, управляемого напряжением (ГУН) 9 для модификации (Vref) опорного напряжения, установленного на выходе схемы формирования опорного напряжения. Это опорное напряжение позволяет ГУН 9 генерировать частоту "сигнала псевдосинхронизации ответчика", которая блокируется на частоте выделенного псевдосинхросигнала ответчика во время, когда был отправлен последний бит кода ответчика. Одновременно схема 7 текущего контроля осуществляет текущий контроль выделенного синхросигнала. После того, как был принят последний бит кода ответчика, импульсы синхронизации ответчика более не могут выделяться, и схема 7 текущего контроля выделенного синхросигнала 5 37182 подает сигнал на ГУН 9 поддерживать его настоящую частоту выходного сигнала, соответствующую частоте синхронизации ответчика во время передачи последнего бита данных из ответчика. Выходной сигнал ГУН 9 подается на логическую схему 10 отключения запросчика, которая контролирует работу схем 11 передатчика, в сочетании с сигналом "Достоверного кода" из микропроцессора 5 через логическую схему 12. При успешном приеме сигнала ответа запросчиком сигнал запроса модифицируется для того, чтобы уведомить соответственный ответчик о том, что его ответ был принят и что он должен прекратить дальнейшие передачи своего кода. Принцип работы ответчика схематически показан на Фигуре 2. Когда ответчик принимает сигнал запроса, он модулирует свой собственный идентифицирующий код на сигнал запроса и передает сигнал ответа обратно на запросчик. Затем внутренняя логическая схема ответчика осуществляет текущий контроль сигнала запроса относительно команды на "выключение", представленной кратким прерыванием в сигнале запроса. Если команда на выключение не выявляется, ответчик снова выдает свой идентифицирующий код после произвольной или псевдопроизвольной задержки в ответ на следующий сигнал запроса, и этот процесс повторяется. Как показано на Фигуре 2, передаваемый ответчиком код состоит из ряда битов отсутствия сигнала, за которыми следует бит синхронизации, за которым, в свою очередь, следует манчестерский код, содержащий идентифицирующие данные ответчика. Бит отсутствия сигнала представляет собой интервал одного бита, в котором ничего (логический низкий уровень LOW) не передается, и должен различаться от манчестерского НУЛЕВОГО бита, в котором низкий уровень LOW передается в первой половине периода одного бита, а высокий уровень HIGH во второй половине. В манчестерском коде изменение уровня сигнала от низкого к высокому или от высокого к низкому всегда происходит в середине периода одного бита. Этот факт используется схемой синхронизации запросчика для выделения синхросигнала, использованной для генерирования манчестерского кода в ответчике. Бит цикловой синхронизации (sync) представляет собой бит логической единицы ONE, который при передаче в манчестерском формате комбинируется с синхросигналом таким образом, что манчестерский бит находится на высоком уровне HIGH в первой половине бита и на низком уровне LOW во второй половине бита, когда период присутствия находится на низком уровне. Поскольку опорное напряжение получают на основе измерения длительности импульса в первой половине манчестерского представления бита цикловой синхронизации, важное значение имеет то, чтобы этот импульс происходил в первой, а не во второй половине бита. Блок-схема на Фигуре 3 показывает этапы, через которые проходят технические средства запросчика, тогда как на Фигуре 4 показаны некоторые из взаимодействующих форм волны. Этап 1: Осуществляется текущий контроль выходного сигнала усилителя 1 в отношении битов отсутствия сигнала для того, чтобы найти на чало идентифицирующего кода ответчика. Первым битом, переданным после битов отсутствия сигнала, является бит цикловой синхронизации, который используется для определения периода и, следовательно, частоты кода. Сигнал занятости из индикатора активности 6 передается на микропроцессор 5, чтобы указать начало цикла декодирования. Этап 2: Источник постоянного тока в схеме 17 формирования опорного напряжения генерирует опорное пилообразное напряжение (Vref), по которому производят выборку в течение длительности синхронизирующего импульса и затем поддерживают. Такое опорное напряжение непосредственно связано с частотой синхронизации кода. Этап 3: Непрерывно генерируется опорное пилообразное напряжение и сравнивается со взвешенным вариантом эталона. Из показанных на Фигуре 4 форм волны видно, как при увеличении опорного напряжения в 1,5 раза данные защелкиваются, а при вдвое увеличенном опорном напряжении генерируется синхросигнал, который используется микропроцессором 5 для считывания данных на выходе из схемы 3 выделения данных. Когда выделенный синхронизирующий импульс происходит в пределах принятого допуска, значение опорного пилообразного напряжения восстанавливается на уровне, который приблизительно в два раза превышает эталонное напряжение. Производится выборка значений пилообразного напряжения, которые фиксируются в момент, когда происходит синхронизация, и сравниваются с опорным напряжением, которое модифицируется для прослеживания частоты синхронизации ответчика. Этап 4: Когда синхронизирующие импульсы больше не принимаются (после того, как был декодирован последний бит кода) значение пилообразного напряжения не восстанавливается и достигает значения напряжения, в четыре раза превышающего опорное напряжение, активирующее этап 5. Этап 5: На этом этапе схема 7 текущего контроля выделенного синхросигнала выдает сигнал "поддерживать" к ГУН-у 9, который поддерживает опорное напряжение на его настоящем уровне таким образом, что ГУН продолжает генерировать свою настоящую частоту выходного сигнала. Если микропроцессор определяет, что декодированный код является достоверным, он позволяет логической схеме отключения запросчика указывать ответчику на то, что он успешно идентифицирован. Если это недостоверный код, микропроцессор 5 восстановит схему передачей сигнала "восстановления", чтобы начать обнаруживать схему 4 и она начнет искать следующий код. Этап 6: Сигнал запросчика модифицируется для того, чтобы указать соответствующему ответчику, что он был успешно идентифицирован. В настоящем примере осуществления изобретения это достигается выключением передатчика 11 на короткий период времени точно описанным ниже способом. Фигура 5 показывает более подробно, как происходит фазовая блокировка и процесс выделения синхросигнала. Схема 4 обнаружения на 6 37182 чала осуществляет текущий контроль манчестерского кода на выходе усилителя 1 и указывает на активность кода, которая запускает этап 2 получения опорного напряжения. Выходной сигнал генератора пилообразного напряжения 51 выбирается и удерживается выборочной фиксирующей схемой 52 в конце синхронизирующего импульса. Это опорное напряжение (Vref) увеличивается в четыре раза усилителем 104 и используется для генерирования ряда различных опорных уровней посредством сети 105 делителя и компаратора. Пилообразный сигнал синхронизации непрерывно генерируется и сравнивается с опорной сетью для определения предпринимаемого действия. При увеличении установленного опорного напряжения в 1,5 раза мы находимся в первой половине периода манчестерского бита, и состояние защелкивается в триггере 106 типа D. Когда в пределах его допуска происходит переход из одного состояния в другое состояние (1.8 Vref 2.2 Vref) в середине периода одного двоичного разряда генерируется выделенный синхронизирующий импульс. Этот импульс используется микропроцессором 5 для считывания защелкнутого выходного сигнала триггера типа D. Это действие повторяется в течение длительности кода и связанного выделенного сигнала синхронизации. Эти генерированные опорные сигналы основываются на том факте, что поддерживаемое опорное напряжение пропорционально длительности импульса половины периода бита, измеренного в первой половине периода бита синхронизации. Когда происходит синхронизирующий импульс, схема 107 квантования с запоминанием фазового компаратора выбирает и удерживает значение линейно изменяющейся опорной синхронизации и сравнивает его после деления его на два в 53 схеме делителя, чтобы удерживать опорное напряжение синхронизации (Vref). Если имеет место какая-либо разность, часть разности объединяется суммирующим устройством 108 с опорным напряжением (Vref), чтобы привести опорное напряжение и, следовательно, генерированную частоту синхронизации к новому значению частоты выделенного синхросигнала ответчика. Когда код заканчивается, никакой другой синхронизирующий сигнал не может выделяться, в результате этого генератор 51 пилообразного напряжения не перезапускается. Затем пилообразное напряжение достигает значения, в четыре раза превышающего Vref, и выходной сигнал компаратора 105 приводит в действие логический переключатель 55, который восстанавливает генератор пилообразного напряжения 51 и продолжает генерировать псевдосинхронизирующие импульсы при вдвое большем базовом периоде обновленной синхронизации (Vref). обработки запросной системы через системный интерфейс 13. Как видно из Фигуры 6, временная диаграмма сигналов схематически показывает, как запросчик синхронизирует свой сигнал краткой остановки или "выключения" с работой ответчика. Диаграмма на Фигуре 6 показывает сигнал модуляции 109, который генерируется ответчиком и который заканчивается на периоде N+1 формы 110 сигнала синхронизации ответчика. Через два тактовых интервала на тактовом интервале N+3 логические схемы ответчика проверяют, что сигнал запроса все еще принимается. Непосредственно после N+3 тактового интервала ответчика запросчик отключает свой сигнал запроса, уменьшая свою выходную мощность 111 до нуля, и остается отключенным до конца N+6 тактового интервала ответчика. В конце тактового интервала N+6 логическая схема ответчика проверяет, что сигнал запроса все еще отсутствует. Сигнал запроса затем восстанавливается до полной мощности на тактовом интервале N+8, логическая схема ответчика проверяет, присутствует ли снова сигнал запроса. Проверка повторяется на тактовом интервале N+8. Если все проверки являются правильными, ответчик решает, что на него подается сигнал выключения от запросчика, и блокирует передачу других сигналов ответа. Ответчик остается выключенным до такого времени, пока сигнал запроса остался выключенным в течение заранее установленного времени, обеспечивая возможность восстановления всех ответчиков, и пока впоследствии восстанавливается сигнал запроса. Форма сигнала 112 на Фигуре 6 представляет собой импульс, генерированный схемами извлечения данных и проверки достоверности кода запросчика при обнаружении кода достоверного сигнала ответа от ответчика, тогда как форма сигнала 113 представляет собой разрешающий сигнал ответчика, генерированный внутренними логическими схемами ответчика. Как можно увидеть из диаграммы, разрешающий сигнал ответчика изменяет состояние в конце N+8 тактового интервала ответчика после подтверждения сигнала выключения из запросчика. Чтобы избежать генерирования нежелательной внешней радиопомехи, сигнал запроса не отключается или восстанавливается мгновенно, но отключается и восстанавливается на регулируемой скорости логической схемы 10 отключения запросчика в пределах по крайней мере одного тактового интервала ответчика, как показано на Фигуре 6. Время нарастания и время спада последовательности регулируются с целью поддерживания максимальных частот, генерированных переходами в пределах приемлемого диапазона. Это достигается схемой установки фильтра на входе передатчика 11, которая ограничивает время нарастания и время спада скорости сигнала возбуждения, подаваемого на вход передатчика. Микропроцессор 15 считывает данные из сигнала на каждом синхронизирующем импульсе и определяет достоверность кода посредством алгоритма обнаружения ошибок. В настоящем примере осуществления изобретения используется простой алгоритм контроля по четности. Если код проходит контроль, микропроцессор позволяет логической схеме выключения запросчика модифицировать сигнал запроса и посылает код на схемы Ответчик осуществляет текущий контроль "нарастающего фронта" в конце сигнала отключения запросчика, а не заднего фронта импульса, поскольку характеристики последнего имеют тенденцию больше изменяться с изменениями в электрической емкости системы и другими зна 7 37182 чениями параметра компонента и с отведенной передатчиком мощностью. Результат вышеописанных методов состоит в том, что окно "отключения" в запросном сигнале, которыйконтролируется каждым ответчиком, является эффективным только шириной в один тактовый интервал (то есть, тактовый интервал между N+6 и N+7), который уменьшает вероятность для двух ответчиков передавать сигнал и отключаться одновременно. В системе, содержащей одну тысячу ответчиков, вероятность ошибки уменьшается примерно до 0,01%. В определенных случаях применения может быть необходимым, чтобы ответчики запрашивались более, чем один раз с короткими интервалами времени между запросами, и впоследствии они должны быть запрошены при более продолжительных интервалах времени. Пример такого применения имеет место в том случае, когда ответчики, описанные в настоящем изобретении, используются для идентификации изделий, находящихся на хранении в супермаркете. Когда автомобиль-фургон для доставки грузов прибывает в супермаркет, содержимое автофургона сканируется запросчиком, получаемая в результате распечатка или отображение данных сравнивается со счетом-фактурой на доставку или инвентаризационной описью. Если отмечаются какие-либо расхождения, может потребоваться повторение процесса запроса в течение относительно небольшого промежутка времени. Эта процедура приводится в действие так, как описано выше. На контрольном выходе из супермаркета, когда заказчик заполнил тележку различными изделиями, на каждом изделии имеется ответчик, ответчики реактивируются и считываются запросчиком, подсоединенным к кассе. Для предотвращения кражи в случае самообслуживания на контрольном выходе, запросчик передает дополнительный сигнал выключения для того, чтобы ответчик отключил его на промежуток времени, после того, как он был удален с поля запроса. На выходе из супермаркета размещается надежный контрольный пункт, способный обнаруживать любые ответчики, которые не были выведены из действия этой процедурой. Через некоторое время после того, как покупатель оставил супермаркет, ответчики еще раз приводятся в действие, позволяя им быть использованными дома. Например, покупатель может иметь запросчик дома, который может быть использован для считывания содержимого кладовой для провизии, чтобы определить, какие изделия необходимо перезакупить. В противном случае ответчики могут сниматься или уничтожаться после того, как они прошли через контрольный пункт. Для внедрения этого аспекта изобретения, ответчик предназначается для поиска подряд двух сигналов выключения. Как описано выше, ответчик отвечает на первый сигнал выключения. Когда этот сигнал выключения обнаруживается, ответчик прекращает дальнейшие передачи, пока он остается в области запросчика. Теперь ответчик занимается поиском второго сигнала выключения. Если обнаруживается второй сигнал выключения, ответчик заряжает конденсатор, используя энергию из сигнала запроса, который блокирует схемы генератора кода ответчика на заранее установленный период времени (скажем, десять минут), после которого ответчик снимается с поля запросчика. На Фигуре 8 показан пример ответчика, который может отвечать на двойные сигналы выключения. Ответчик содержит приемную/передающую антенну 71, выходной сигнал которой подается через диоды D1 и D2 на С1 конденсатор блока электропитания. Когда конденсатор С1 достаточно заряжается, активируются схемы ответчика, и ответчик начинает передавать свой идентифицирующий код, как описано выше. Блок электропитания от конденсатора С1 питает схему 75 генератора кода и схему 78 генератора тактовых импульсов, который принимает сигнал, "разрешающий синхронизацию" через резистор R. Генератор кода, который в нормальном режиме работы разрешается сигналом "разрешения кода" из логической схемы 73 обнаружения промежутка, передает свой выходной сигнал на схему 72 модулятора, которая модулирует идентифицирующий код ответчика из генератора кода 75 на сигнал запроса, на частоте синхронизации, определенной схемой 78 генератора тактовых импульсов. Если сигнал ответа из ответчика успешно обнаруживается запросчиком, запросчик передает первый сигнал выключения, как показано на Фигуре 7, между тактовыми интервалами ответчика N+3 N+8. Это прерывание в запросном сигнале обнаруживается логической схемой 73 обнаружения промежутка и сигнал "разрешения кода" снимается с генератора кода, блокируя ответчик. Теперь логическая схема 73 обнаружения промежутка осуществляет текущий контроль сигнала запроса для второго сигнала выключения, который, на Фигуре 7, происходит между тактовыми интервалами ответчика N+10 и N+11. Если обнаруживается второй сигнал выключения, 73логическая схема обнаружения промежутка передает управляющий сигнал переключателя на управляемый переключатель 114, замыкая переключатель. Это позволяет конденсатору синхронизации Ст заряжаться через диод D3. Когда этот конденсатор достиг заранее установленного уровня заряда, он включается на полевой транзистор Т1, снимая сигнал, "разрешающий синхронизацию" с 115 схемы генерирования синхронизации. Это блокирует ответчик, и ответчик остается в этом состоянии до тех пор, пока он не снимается с поля запросчика. Когда это происходит, конденсатор синхронизации Ст разряжается через параллельный резистор утечки. Когда конденсатор синхронизации Ст полностью разрядился, ответчик снова будет нормально работать, и будет отвечать на сигналы запроса. Однако, если ответчик перемещается в поле запроса в любое время, пока конденсатор Ст все еще заряжается, схема 115 генерирования синхросигнала будет блокированной, задерживая работу ответчика. Фигура 9 представляет собой схематическую диаграмму, иллюстрирующую логическую схему 73 обнаружения отсутствия сигнала, более подробно показанную на Фигуре 8. Эта схема имеет два входа и два выхода, соответствующих входам и выходам, показанным на Фигуре 8. Входы являются "синхронизирующим" входом для 8 37182 приема сигнала синхронизации ответчика и линия "мощности ВЧ-сигнала" для осуществления текущего контроля наличия принятой мощности ВЧсигнала от приемника запросчика. Выходами схем являются выходной сигнал "разрешения кода" для генератора кода 75, и "SW control", управляющий выходной сигнал переключателя для управления управляемым переключателем 114. Когда мощность первоначально подается на логическую схему 73 обнаружения отсутствия сигнала, схема 85 возврата включения питания подает восстанавливающий сигнал на триггер блокировки 90 и восстанавливает схему 5 генератора случайных промежутков. Схема 5 генератора случайных промежутков подает выходной импульс на триггер 116 подключения модулятора после псевдопроизвольной задержки, эффективно изменяя расстояние между последующими передачами данных из ответчика. Генератор случайных чисел в схеме генератора случайных промежутков подсевается каждый раз, когда восстанавливающий сигнал принимается из схемы 85 возврата включения питания. Триггер 116 подключения модулятора конфигурируется для запуска состояния восстановления, подавая восстанавливающий сигнал на счетчик 82 длины блока данных, который измеряет и контролирует длину кодов, переданных генератором кода 75. Q - выход 90 триггера блокировки подается на вход 1 триггера 116 подключения модулятора. Генератор 84 случайных промежутков генерирует выходной импульс на псевдопроизвольном расстоянии, которое периодически переключает триггер 116 подключения модулятора. Если 1 вход этого триггера имеет высокий уровень, его Q выход становится высоким уровнем. Это служит в качестве сигнала "разрешения кода", подключающего генератор кода 75. Этот выходной сигнал также подается на вентиль И 117, который позволяет синхронизирующему сигналу ответчика подаваться на счетчик 82 длины блока данных, который регистрирует одну единицу счета для каждого поступающего синхронизирующего импульса, когда генератор кода 75 выдает последовательность идентифицирующего кода ответчика. В конце последовательности кода счетчик длины блока данных переполняется, обеспечивая подачу восстанавливающего сигнала на триггер 116 подключения модулятора. Это перемещает сигнал "разрешения кода" из Q выхода триггера 116 подключения модулятора, и включает параллельную нагрузку правого сдвигового регистра 89, который загружается с последовательностью нуля за исключением первого разряда (самый левый двоичный разряд на Фигуре 9), который загружается с единицей. Каждый из шести триггеров с защелкой от 118 до 123 восстанавливается выходным сигналом из счетчика 82 длины блока данных. Последовательный ввод сдвигового регистра 89 удерживается на логическом "нуле", и сдвиговый регистр размещается таким образом, что для каждого синхронизирующего импульса загружение "1" смещает одну ячейку вправо. Выходы сдвигового регистра подсоединяются таким образом, чтобы синхронизировать триггеры с защелкой в надлежащем периоде повторения тактовых или синхронизирующих импульсов, соответствующем диаграмме синхронизации, показанной на Фигуре 7. Входы 1 триггеров с защелкой от 118 до 123 подсоединяются к "мощности РЧ" (RF-power) линии схемы и защелки либо регистрируют "1", либо "ноль", в зависимости от состояния линии "мощности РЧ", когда "1", распространяющаяся вдоль сдвигового регистра, синхронизирует соответствующую защелку. Если запросчик принял совершенный идентифицирующий код от ответчика и модулировал сигнал запроса с соответственным сигналом прерывания или выключения, состояние триггеров с защелками от 118 до 123 будет соответствовать заранее установленной последовательности единиц и нулей, которая декодируется несколькими вентилями, содержащими инверторы 124 и 125, и вентили И 126 и 127 многоканального входа. Когда принимается правильная модуляция выключения, фронт выводится вентилем И 126, который подается на вход синхронизации триггера 90 блокировки, блокирующего дальнейшее переключение из одного состояния в другое триггера 116 подключения модулятора. Если обнаруживается второй сигнал выключения, выходной сигнал вентиля И 127 имеет высокий уровень, повышая выходной сигнал "SWcontrol" и блокируя бортовой генератор синхронизирующих импульсов ответчика. Фигура 10 показывает принцип действия вышеописанной версии работы ответчика в формате блок-схемы. Вышеописанная технология со ссылкой на Фигуры 8 и 9 может также применяться для предотвращения воровства, в том случае, когда ответчики, описываемые в настоящем изобретении, используются для "связи" предметов торговли на выходе розничной продажи. В таком применении запросчик на кассе или контроле у выхода передает сигналы запроса ответчикам в отношении предметов торговли, и эффективно посылает сигналы выключения на эти ответчики, когда они успешно идентифицируются. Посредством схем, аналогичным описанным на Фигурах 8 и 9, ответчик блокируется на заранее установленный период времени (скажем, десять минут). Тогда заказчик пропускается через выход, на котором размещается второй запросчик. Те ответчики, которые были блокированы правильной обработкой на контроле у выхода, не будут отвечать на сигналы запроса от запросчика на выходе. Однако, ответчики в изделиях, которые были украдены в магазине, будут обнаруживаться запросчиком на выходе, который может генерировать соответствующий сигнал тревоги. Вышеописанные ответчики являются относительно устойчивыми и недорогими, и могут применяться для множества различных изделий, как упомянуто выше. В большинстве случаев единственный запросчик не потребовался бы для того, чтобы идентифицировать ответчики, связанные с полностью различными типами изделий. Например, запросчик, использованный в супермаркете для целей переучета товаров, не потребуется для того, чтобы идентифицировать автомобили. Если бы каждый запросчик требовался для того, чтобы идентифицировать все возможные ответчики, неприемлемо большое количество информации потребовалось бы хранить в передатчике запросчика, 9 37182 и обработка проверки на достоверность запросчика стала бы чрезмерной. Чтобы справиться с этой ситуацией, передатчики запросчиков и ответчики, предназначенные для использования с различными категориями товаров, имеют распределенные коды различной длины. Например, система идентификации, использованная при проверке на достоверность номерного знака автомобиля, может быть распределенными кодами, которые имеют длину 24 бита, которая не будет интерпретироваться как достоверная смежным устройством для считывания регистрационных номеров автомобиля, которое срабатывает с кодом 22 бита. Даже если ответчики двух систем передают свои сигналы ответа одновременно, случайные или псевдослучайные задержки между сигналами ответа будут гарантировать, что ответчики обеих систем будут в конечном счете услышаны. Фиг. 1 Фиг. 2 10 37182 11 37182 Фиг. 4 Фиг. 3 12 Фиг. 5 37182 13 37182 Фиг. 6 Фиг. 7 14 37182 Фиг. 8 15 Фиг. 9 37182 16 37182 Фиг. 10 Тираж 50 екз. Відкрите акціонерне товариство «Патент» Україна, 88000, м. Ужгород, вул. Гагаріна, 101 (03122) 3 – 72 – 89 (03122) 2 – 57 – 03 17

ДивитисяДодаткова інформація

Назва патенту англійськоюIdentification system and transponder for identification system

Автори англійськоюMarsh Michael John Kamill, Van Zil Klinton Aiden

Назва патенту російськоюСистема идентификации и ответчик для системы идентификации

Автори російськоюМарш Михаель Джон Камилл, Ван Зил Клинтон Айден

МПК / Мітки

МПК: G06K 19/00, G01S 13/74, H04B 1/59, G06K 19/07, G08B 26/00, G06K 7/00, G01S 13/78

Мітки: система, системі, відповідач, ідентифікації

Код посилання

<a href="https://ua.patents.su/17-37182-sistema-identifikaci-ta-vidpovidach-dlya-sistemi-identifikaci.html" target="_blank" rel="follow" title="База патентів України">Система ідентифікації та відповідач для системи ідентифікації</a>