Пристрій для обробки інформації мультипроцесорної системи

Формула / Реферат

Устройство для обработки информации мультипроцессорной системы, содержащее процессор, блок оперативной памяти, блок памяти команд, первый блок управления и входной регистр, отличающееся тем, что, с целью повышения быстродействия, оно содержит второй блок управления, блок памяти признаков, блок памяти готовых сегментов, блок памяти готовых результатов, блок памяти адресов, селектор адреса, селектор команд, блок модификации признаков, блок фиксации единиц, генератор тактовых импульсов, дешифратор, блок сравнения, арбитр магистрали, с первого по третий ключи, с первого по третий триггеры, первый и второй триггеры готовности приема, триггер готовности выдачи, триггер запроса прямого доступа, регистр признаков, счетчик адресов записи, счетчик адресов чтения, первый и второй счетчики адресов, счетчик количества слов, блок фиксации нулей и триггер признака захвата, причем выход генератора тактовых импульсов подключен к тактовым входам первого и второго блоков управления, выходы первого, второго и третьего триггеров подключены соответственно к управляющим входам первого, второго и третьего ключей, информационный вход-выход устройства для обработки информации подключен к первому информационному входу-выходу первого ключа, к первому информационному входу-выходу второго ключа, к информационному входу селектора команд, к информационному входу селектора адреса, к входу-выходу прямого доступа процессора, к первому входу режима первого блока управления, к первому выходу первого блока управленимя, к входу записи-чтения блока памяти адресов, к второму выходу первого блока управления, к третьему выходу первого блока управления, к первому входу записи счетчика количества слов, к счетному входу второго счетчика адреса, к входу установки в ''1'' третьего триггера, к четвертому выходу первого блока управления, к входам синхронизации счетчика количества слов, первого счетчика адреса, блока памяти адресов, к пятому выходу первого блока управления, к входу синхронизации блока памяти результатов, к шестому выходу первого блока управления, к входу установки в "1" второго триггера готовности приема, к второму входу установки в "0" третьего триггера, к входу синхронизации арбитра магистрали, выход признака разрешения прямого доступа процессора подключен к второму входу режима второго блока управления, выход селектора адреса подключен к входу установки в "1" первого триггера готовности приема и к первому входу установки в "І" триггера запроса прямого доступа, выход которого подключен к входу признака запроса прямого доступа процессора, второй информационный вход-выход первого ключа подключен к первому информационному входу-выходу третьего ключа, к информационному входу-выходу входного регистрa, к входу-выходу адреса данных блока оперативной памяти, к входу-выходу адреса данных блока памяти команд, к информационному входу-выходу процессора, к входу дешифратора, к выходу блока памяти номеров готовных сегментов и к выходу триггера готовности выдачи, вход начальной установки устройства для обработки информации подключен к входу запуска генератора тактовых импульсов, к первым входам установки в "0" первого, второго и третьего триггеров, первого и второго триггеров готовности приема триггера готовности выдачи, триггера признака захвата, триггера запроса прямого доступа, к первым входам установки в "0" счетчика адресов записи, счетчика адресов считывания, первого счетчика адреса, к входам установки в "0" второго счетчика адреса и счетчика количества слов и к входу установки в исходное состояние арбитра магистрали, второй информационный вход-выход второго ключа подключен к второму информационному входу-выходу третьего ключа, к информационному входу-выходу блока памяти результатов, к выходу блока памяти адресов, к выходу второго триггера готовности приема, к информационным входам первого и второго счетчиков адреса и счетчика количества слов, выход которого подключен к информационному входу блока фиксации нулей, выход которого подключен к третьему входу режима первого блока управления, седьмой выход которого подключен к второму входу установки в "1" триггера запроса прямого доступа, восьмой выход первого блока управления подключен к третьему входу установки в "0" первого счетчика адреса, к первому входу установки в "1" триггера признака захвата и к входу установки в "1" третьего триггера, девятый выход первого блока управления подключен к второму входу записи счетчика количества слов и к входу записи второго счетчика адреса, десятый выход первого блока управления подключен к счетному входу первого счетчика адреса, одиннадцатый выход первого блока управления подключен к входу декремента счетчика количества слов и к входу записи-чтения блока памяти результатов, двенадцатый выход первого блока управления подключен к входу чтения-записи блока фиксации нулей, тринадцатый выход первого блока управления подключен к второму входу установки в "0" второго триггера готовности приема, к вторым входам установки в "0" третьего триггера и триггера признака захвата, четырнадцатый выход первого блока управления подключен к третьему входу установки в "0" первого счетчика адреса и к первому управляющему входу арбитра магистрали, пятнадцатый выход первого блока управления подключен к второму управляющему входу арбитра магистрали шестнадцатый выход первого блока управления подключен к входу синхронизации блока фиксации нулей и к входу синхронизации второго счетчика адреса, выходы первого и второго счетчиков адреса подключены соответственно к адресным входамблока памяти результатовиблокапамяти адресов, выход арбитра магистрали подключен к четвертому входу режима первого блока управления, управляющий вход устройства для обработки информации для подключения к внешней магистрали вычислительной системы подключен к информационному входу селектора команд, управляющий вход которого подключен к выходу первого триггера готовности приема, первый вход селектора команд подключен к третьему входу установки в "1" триггера запроса прямого доступа, второй выход селектора команд подключен к входу разрешения выдачи признака прямого доступа процессора, третий выход селектора команд подключен к второму входу установки в "1" триггера признака захвата и к входу установки в ''1'' первого триггера, четвертый выход селектора команд подключен к входу чтения-записи входного регистра и к первому входу режима второго блока управления, пятый выход селектора команды подключен к вторым входам установки в "0" первого триггера и первого триггера готовности приема, к третьему входу установки в "0" триггера признака захвата и к второму входу установки в "0" триггера запроса прямого доступа, первый выход дешифратора подключен к входу синхронизации триггера готовности выдачи, второй выход дешифратора подключен к счетному входу счетчика адреса чтения, третий выход дешифратора - к входу синхронизации второго триггера готовности приема, четвертый выход дешифратора - к пятому входу режима первого блока управления, выход входного регистра подключен к адресному входу блока памяти признаков, к первому информационному входу блока модификации признаков и к информационному входу блока памяти номеров готовых сегментов, выход блока памяти признаков подключен к второму информационному входу блока модификации, выход которого подключен к информационному входу регистра признаков, выход которого подключен к информационным входам блока памяти признаков и блока фиксации единиц, выход которого подключен к второму входу режима второго блока управления, первый выход которого подключен к второму входу установки в "0" триггера готовности выдачи и к входу записи-считывания регистра признаков, второй выход второго блока управления подключен к управляющему входу блока фиксации единиц, третий выход второго блока управления подключен к входу записи-чтения блока памяти номера готовых сегментов и к входу записи блока памяти признаков, четвертый выход второго блока управления подключен к счетному входу счетчика адресов записи, пятый выход второго блока управления подключен к входу синхронизации блока сравнения, прямой и инверсный выходы которого подключены соответственно к входу установки в "1" и к третьему входу установки в "0" триггера готовности выдачи, шестой выход второго блока управления подключен к входу чтения блока памяти признаков, выход триггера признака захвата подключен к входу признака захвата процессора, вход-выход признака занятости магистрали устройства для обработки информации подключен к информационному входу-выходу арбитра магистрали, выход счетчика адресов записи подключен к первому информационному входу блока сравнения и к первому адресному входу блока памяти номеров готовых сегментов, выход счетчика адресов чтения подключен к второму информационному входу блока сравнения и к второму адресному входу блока памяти номеров готовых сегментов.

Текст

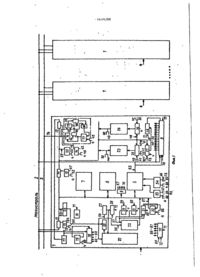

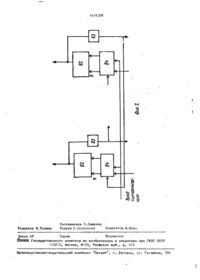

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИН (51)5 G 06 F ГОСУДАРСТВЕННЫЙ НОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ ПРИ ГКНТ СССР 15/00 " ОПИСАНИЕ ИЗОБРЕТЕНИЯ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) (22) (46) (72) 4679224/24 22.03.89 Г 1 07.01.91. В.Г.Коссовский (53) 681.325(088.8) (56) EKETrans on Computers, 1983, v.32, * 5, p.32. Хвощ С.Т., Вардинский Н.Н. и Попов Е.А. Микропроцессоры и никроЭВМ в системах автоматического управления. Справочник. Л.: Машиностроение, 1987, с.382, рис.11.14. (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ МУЛЬТИПРОЦЕССОРНОЙ СИСТЕМЫ (57) Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем высокой производительности. Цель изобретения - повышение быстродействия. Поставленная цель достига Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем высокой производительности. Цель изобретения - повышение быстродействия. На фиг.1 представлена схема устройства для обработки информации и его внешнее подключение; на фиг.2 схема блоков управления. Вычислительная система содержит устройства 1 для обработки информации, внешнюю магистраль 2 вычислительной системы, вход-выход признака занятости магистрали ется тем, что устройство для обработки информации содержит процессор, блок памяти команд, блок оперативной памяти, дешифратор, два блока управления, три ключа, три триггера, генератор тактовых импульсов, селектор адреса, селектор команд, два триггера готовности приема, блок памяти признаков, блок памяти номеров готовых сегментов, блок памяти результатов, блок памяти адресов, входной регистр, блок модификации, регистр признаков, блок фиксации єдиний, счетчик адресов записи, счетчик адресов считывания, блок сравнения, триггер готовности выдачи, триггер признака захвата, триггер запроса прямого доступа, два счетчика адреса, счетчик количества слов, блок фиксации нулей и арбитр магистрали. 2 ил. для обработки информации, вход 4 начальной установки устройства для обработки информации, процессор 5, блок 6 памяти команд, блок 7 оперативной памяти, дешифратор 8, первый 9 и вто00 рой 10 блоки управления, ключи 11 и 12, с первого 13 по третий 15 триггеры, генератор 16 тактовых импульсов, селектор 17 адреса, селектор 18 команд , первый 19 и второй 20 триггеры готовности приема, блок 21 памяти признаков, блок ?.?. памяти номеров готовых сегментов, блок 23 памяти результатов, блок 24 памяти адресов, входной регистр 25, блок 26 модифи кпцни признаков, регистр 27 признаков, блок 28 фиксации единиц, счетчик 29 адресов записи, счетчик 30 адресов считывания, блок 31 сравнения, триггер 32 готовности выдачи, триггер 33 признака захвата, триггер ЗА запроса прямого доступа, первый 35 и второй 36 счетчики адреса, счетчик 37 количества слол, бпок 38 фиксации ну. ей, арбитр 39 магистрали, с первого 60 по шестнадцатый 55 выходы блока 9 управления, с первого 56 по шестой 61 выходы блока 10 управления, с первого 62 по пятый 66 выходы селектора 18 команд, с первого 67 по четвертый 70 выходы дешифратора 3, выход 71 генератора 16 тактовых импульсов, выход 2 блока 28 фиксации единиц, выход 73 селектора 17 адреса, информационный вход-выход 74 арбитра 39 маги:трали, выход 75 арбитра 39 магистрали. Арбитр 39 магистрали содержит ключ 76, триггер 77 запроса магистрали, элемент 78 задержки и с первого 79 по третий 81 элементы ИЛИ. Первый 9 и второй 10 блоки управления содержат триггеры 82, элементы 83 задержки и формирователи .84 сигналов управления. признаков производится при поступлении каждого аргумента., Аргумент от одного устрой* тва для обработки информации к другому передается с помощью двух слоев: адресного и значащего. Адресное слово содержит номер устройства для обработки информации, номер сегмента, 10 которому предназначен аргумент, номер признака, который присвоен данному аргументу в линейке признака, и количество признаков данного сегмента. Адресное слово состоит из двух 15 слов (для случал, например, 16-разрядного процессора 5 ) : первая часть адресного слова 20 устройства вторая часть адресного слова 25 15 32 № сегмента 30 65 № признака к-во признаков 0 Значаще слово содержит собственно значение аргумента. Вся программа решения задачи разПри появлении на магистрали 2 первой части адресного слова в опредебивается на независимые участки (сегленном устройстве для обработки инменты) , которые могут быть выполнеформации срабатывает селектор 1 7 адны параллельно. Группы сегментов реса, который выдает сигнал на устазаносятся в блок 6 памяти команд новку триггера 19 (ТгТПІ) и триг(ПК) и запуск сегмента на исполнение гера 34, что подготовит адресуемое " производится по готовности аргуменустройство для обработки информации тов сегмента. Исполнение сегмента 40 к последующему приему второй части производится процессором 5 по проадресного слова и значагаего слова . грамме сегмента под управлением поРторая часть адресного слова потока команд (по счетчику команд). ступает на входной регистр 25 (РгЕх) Блок 21 памяти признаков (ІШР) сои служит адресом для записи в блок 7 держит линейки признаков, соответзначащего слова, а также адресом ствующие каждому сегменту данного отмечаемой линейки признаков. При устройства для обработки информации. этом запускается блок 10 управления, Количество признаков соответствует осу пест вляющий управление, отметку копичеству информационных и логичепризнаков и определение готовых сегских аргументов сегмента. Если ар50 ментов. гумент готов, то соответствующему В первом такте работы блока 10 • • признаку присваивается значение 1, управления производится выборка из если не готов - 0. Когда готовы все блока 21 памяти признаков сегмента аргументы сегмента, то в линейке по адресу, содержащемуся в разрядах признаков сегмента устанавливаются 55 15-6 регистра 25. Выбранный код логивсе единицы, что является сдвидечески суммируется с, кодом,выбранным тельством того, что данный сегмент блоком 26 модификации, на вход котоготов к исполнению. Отмека признарого поступает код разрядов с пятого ков и проверка единиц в пииейках 5 1619288 по нулевой входного регистра 25 и е каждый сегмент программы записывается в регистр 27 признаков. и содержание информацию о начальном При этом в разряд регистра 27, котоадресе в ЛАР и количестве рассылочрый соответствует номеру признаков, ных результатов. Формат информацион-1 записывается 1 (порядок номеров возпого слова имеет вид: растает справа налево) и, кроме то15 И 1 0 0 го, единицы записываются в такое коАдрес начала Ф Р Кол-во рассылок личество крайних слева разрядов, какое соответствует числу неиспользо10 Распределение памяти адресов ПАР ванных признаков (свободных мест), может иметь вид: равному разнице между максимально воз можным и числом используемых в сег1-е а пр. слово рез. 1 менте признаков, указанных в разрядах с второго по нулевой входного ре- 15 рез. 1 2-е адр. слово гистра 25. се-гм. № 1 Далее производится опрос блока 28 рез.2 1-е адр. слово фиксации единиц, Ксли в слове, записанном в регнс7*р 27, окажутся все рез, 2 2-е адр. слово 20 единицы, то производится запись номера сегмента, содержащегося в разрядах с пятнадцатого по шестой входно1-е адр. слово рез. 1 сегм. № 2 го регистра 25 в блок 22 памяти готовых сегментов по адресу, содержащему2-е адр. слово рез. 1 ся в счетчике 29, а в блоке 21 памя- 25 ти на место выбранного слова признаков записывается 0, если в регистре *айлы адресов результатов заносят27 признаков не все единицы, то зася в ПАР при программировании. пись в блок 22 памяти не производитМассив результатов и информационся, а в блок 21 памяти на место выб- 30 ное слово формируются в блоке 7 памяранного слова признаков записывается ти процессором 5 в процессе реализамодифицированное слово. Управление ции сегментов программы. ,^ блоком '?.?. памяти производится с поПо окончании выполнения сегмента мощью счетчиков 29 и 30. В начале программы процессор 5 запрашивает гоработы при поступлении сигнала на 35 товность к приему информации и при ее вход 4 оба счетчика устанавливаются наличии запускает блок 9 управле1 После записи первого кода ния, который управляет рассыпкой. готового сегмента (КГС) ' в счетчик Сначала осуществляется пересылка 29 адресов записи прибавляется едииз блока 7 памяти в блок 23 памяти ница. Чтение блока 22 памяти произ40 массива значений результатов сегменводится по запросу процессором 5. та, в счетчик 36 адреса начала ФР, Сначала опрашивается триггер 32 гов счетчик 37 - кода количества растовности выдачи» определяющий налисылок. Рассылка прекращается, когда чие информации (кодов готовых сегменв счетчике 37 будет нуль, что фиктов) в блоке 22 памяти. Триггер 32 45 сируется блоком 38. устанавливается в "і", если содерДалее осуществляется рассьитка режимое счетчика 29 и счетчика 30 не • зультатов по адресам согласно файлу равно (т.е. , когда в блоке 22 имеетрассыпки (Фр). Сначала производится ся информация). При этом чтение КГС захват магистрали 2 через арбитр 39 из блока 22 памяти производится по 50 магистрали. Для этого через первый адресу» определяемому счетчиком 30. управляющий вход арЛитра 39 подается После чтения КГС в счетчик 30 добавсигнал на первый вход элемента ИЛИ ляется 1. 79, второй вход которого связан с Исходными данными для рассылки явинформационным входом-выходом 74 ляются результаты работы сегмента, 55 занятости магистрали 2. Если на вхозаписанные в блок 7 памяти, файл адде-выходе 74 высокий потенциал ("Маресов рассылки (Лр), записанный в гистраль свободна"), то сигнал прообласти памяти адресов рассылки (ПАР) ходит через элемента ИЛИ 79, задержи информационное слово (ИС), сопроки 78, ИЛИ 80 и устанавливает триг •о 1619288 rep 77 в " 1 " . Сигнал с выхода триггера 77 поступает на управляющий вход ключа-If}, который открывается и устанавливает на магистрали 3 низкий потегциал,что о-знлчает занятость магистрали 2. Если магистраль занята другим устройством для обработки информации, то сигнал захвата через элемент И И 79 не проходит и триггер Л 10 77 остается із нулевом состоянии. После захвата магистрали производится чтение из блока 24 памяти и выдачи на магистраль 2 номера устройства обработки информации, в которое необходимо записать результат. Зятем производится чтение из блока 24 памяти и передача в соответствующее устройство дл/1 обработки информации второго адресного слова (но20 мер сегмента, номер признака), после чего производится чтение из блока 23 памяти и передача в блок 7 памяти значения результата. При этом в счетчик 36 прибаьлчется 1, в счетчик 35 25 прибавляется 1, из счетчика 37 вычитается 1. Далее проверяется содержимое счетчика 37 и, если оно не равно нулю, то производится пересыпка следующего результата и т . д . Если содержимое счетчика 37 равно нулю, рассыпка заканчивается, блок 9 управления ставится в исходное состояние и триггер устанавливается в " 1 " . Ф о р м у л а и з о б р е т е н и я 8 .ки адресов, счетчик количества слов, блок фиксации нулей и триггер признака захвата, причем выход 'енератора тактовых импульсов подключен к тактовым входам первого и второго блоков управления, выходы первого, второго и третьего триггеров подключены соответственно к управляющим 5 входам первого, второго и третьего ключей, информационный вход-выход устройства для обработки информации подключен к первому информационному входу-выходу первого ключа, к первому информационному входу-выходу второго ключа, к информационному пходу селектора команд, к информационному входу селектора адреса,к входу-выходу пря- мого доступа процессора,к первому входу ре-жима первого блока управления, к первому выходу первого блока ynpas-t ления, к входу записи-чтения блока памяти адресов, к второму выходу первого блока управления, к третьему выходу первого блока управления, к первому входу записи счетчика количества слов, к счетному входу второго '. счетчика адреса, к входу установки в " 1 " третьего триггера, к четвертому выходу первого блока управления, к входам синхронизации счетчика количества слов, первого счетчика адреса, блока памяти адресов, к пятому выходу первого блока управления, к входу синхронизации блока памяти реZS зультатов, к шестому выходу первого блока управления, к входу установки Устройство для обработки инфорв " 1 " второго триггера готовности мации мультипроцессорной системы, приема, к второму входу установки содержащее процессор, блок операв "О" третьего триггера, к входу синтивной памяти, блок памяти команд, хронизации арбнгра магистрали, вы40 первый блок управления и входной реход признака разрешения прямого догистр, о т л и ч а ю щ е е с я тем, ступа процессора подключен к зторочто, с целью повышения быстродейстму входу режима второго блока управвия, оно содержит второй блок управления, выход селектора адреса подления, блок памяти признаков, блок ключен к входу установки в " ї " перпамяти готовых сегментов, блок памяти вого триггера готовности приема и готовых результатов, блок памяти адк первому входу установки в " і " тригресов, селектор адреса, селектор когера запроса прямого доступа, выход манд, блок модификации признаков, которого подключен к входу признака блок Фиксации единчц, генератор такзапроса прямого доступа процессора, Ш второй информационный вход-выход пертовых импульсов, дешифратор, блок сравнения, арбитр магистрали, с первого ключа подключен к первому инвого по третий ключи, с первого по формационному входу-выходу третьего третий триггеры, первый и второй тригключа, к информационному входу-выходу геры готовности приема, триггер говходного регистра, к входу-выходу товности выд?чч, триггер запроса адреса данных блока оперативной папрямого доступа, регистр признаков, мяти, к пходу- выходу адреса данных счетчик адресов записи, счетчик адблока памяти команд, к информаиион ресов чтения, перпыл и гторой счетчн 1619288 ному входу-выходу процессора, к входу дешифратора, к выходу блока памяти номеров готовых сегментов и к выходу триггера готовности выдачи, вход _ начальной установки устройства для обработки информации подключен к входу запуска генератора тактовых импульсов, к первым входам установки В 0 ПервОГО, ВТОРОГО И Третьего |Q триггеров, первого и второго триггеров готовности приема триггера готовности выдачи, триггера признака захвата, триггера запроса прямого доступа, к первым входам установки в J5 "О" счетчика адресов записи, счетчика адресов считывания, первого счетчика адреса, к входам установки в "О" второго счетчика адреса и счетчика количества слов и к входу установ- pg ки в исходное состояние арбитра магистрали, второй информационный входвыход второго ключа подключен к второму информационному входу-выходу третьего ключа, к информационному 25 входу-выходу блока памяти результатов, к выходу блока памяти адресов, к выходу второго триггера готовности приема, к информационным входам первого и второго счетчиков зо адреса и счетчкка количества слов, выход которого подключен к информационному входу блока фиксации нулей, выход которого подключен к третьему входу режима первого блока управления, седьмой выход которого под35 ключен к второму входу установки в " 1 " триггера запроса прямого доступа, восьмой выход первого блока управления подключен к третьему входу установки в " 0 " первого счетчика 40 адреса, к первому входу установки в "і" триггера признака захвата и к входу установки з " 1 " третьего триггера, девятый выход первого блока управления подключен к второму вхо45 ду записи счетчика количества слов и к входу записи второго счетчика адреса, десятый выход первого блока управления подключен к счетному входу первого счетчика адреса, одиннад50 цатый выход первого блока управления подключен к входу декремента счетчика количества слов и к входу записи-чтения блока памяти результатов, двенадцатый выход первого блока управления подключен к входу чтения-записи бло- 55 ка фиксации нулей, тринадцатый выход первого блока управления под 1 Э ключей к второму входу установки в "О" второго триггера готовности приема, к вторым входам установки в "О" третьего триггера и триггера признака захвата, четырнадцатый выход первого блока упр-тления подключен к третьему входу установки в " 0 " первого счетчика адреса и к первому управляющему входу арбитра магистрали, п я т надцатый выход первого блока управления подключен к второму управляющему/ входу арбитра магистрали шестнадцатый выход первого блока управления подключен к входу синхронизации блока фиксации нулей и к входу синхронизации второго счетчика адреса, выходы первого и второго счетчиков адреса подключены соответственно к адресным входам блока памяти результатов и блока памяти адресов, выход арбитра магистрали подключен к четвертому входу режима первого блока упуправления, управляющий' вход устройства для обработки информации для подключения к внешней магистрали вычислительной системы подключен к информационному входу селектора команд, управляющий вход которого подключен к выходу первого триггера готовности приема, первый вход селек-' тора команд подключен к третьему входу установки в " 1 й триггера запроса прямого доступа, второй выход селектора команд подключен к входу разрешения выдачи признака прямого доступа процессора, третий выход селектора команд подключен к второму , входу установки в " і " триггера признака захвата и к входу установки в " 1 " первого триггера, четвертый выход селектора команд подключен к входу чтения-записи входного регистра и к первому входу режима второго блока управления, пятый выход селектора команды подключен к вторым входам установки в " 0 " первого триггера и первого триггера готовности приема, к третьему входу установки в "0 триггера признака захвата и к второму входу установки в " 0 й триггера запроса прямого доступа, первый выход дешифратора подключен к входу синхронизации триггера готовности выдачи, второй выход дешифратора подключен к счетному входу счетчика адреса,чтения, третий выход дешифратора - к входу синхронизации .второго триггера готовности приема, четвертый выход !1 1619288 дешифратора - к пятому входу режима первого блока управления, выход входного регистра подключен к адресному входу блока памяти признаков, к первому информационному входу блока модификации признаков и к информационному входу блока памяти номеров готовых сегментов,выход блока памяти признаков подключен к второму информационному входу блока модификации, выход которого подключен к информационному входу регистра признаков, выход которого подключен к информационным входам блока памяти признаков и 15 блока фиксации единиц, выход которого подключен к второму входу режима второго блока управления, первый выход которого подключен к второму входу установки в " О " триггера готовно20 сти выдачи и к входу записи-считывания регистра признаков, второй выход второго блока управления подключен к управляющему входу блока фиксации единиц, третий выход второго блока 25 управления подключен к входу записичтения блока памяти номера готовых сегментов и'К входу записи блока памяти признаков, четв'ертый выход вто 12 рого блока управления подключен к счетному входу счетчика адресов записи, пятый выход второго блока уп* равления подключен к входу синхронизации блока сравнения, прямой и инверсный выходы которого подключены соответственно к входу установки в " 1 " и к третьему входу установки в " 0 " триггера готовности выдачи, шестой выход второго блока управления подключен к входу чтения блока памяти признаков, выход триггера признака захвата подключен к входу признака захвата процессора, вход-выход признака занятости магистрали устройства для обработки информации подключен к информационному входу-выходу арбитра магистрали, выход счетчика адресов записи подключен к первому информационному входу блока сравнения и к первому адресному входу блока памяти номеров готовых сегментов ,выход счетчика адресов чтения подключен к второму информационному входу блока сравнения и к второму адресному входу блока памяти номеров готовых сегментов. tftі ч im 1619288 I ! Редактор Н.Тупица Составитель Л.Смирнов Техред Л.Ссрдюкова Корректор М.Пожо Заказ Ь9 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. Производственно-издательский комбинат "Патент", г,-Ужгород, ул. Гагарина, 101

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/00, G06F 15/76

Мітки: мультипроцесорної, інформації, пристрій, обробки, системі

Код посилання

<a href="https://ua.patents.su/8-5007-pristrijj-dlya-obrobki-informaci-multiprocesorno-sistemi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для обробки інформації мультипроцесорної системи</a>

Попередній патент: Електропривід постійного струму

Наступний патент: Пристрій для експрес-діагностики білірубінемії

Випадковий патент: Спосіб визначення нормативних гормональних показників жіночої статевої системи у дівчаток підліткового віку в різних фазах менструального циклу