Пристрій для реалізації швидкого перетворення хартлі

Номер патенту: 64265

Опубліковано: 16.02.2004

Автори: Дуденко Сергій Васильович, Рубан Ігор Вікторович, Голубничий Дмитро Юрійович, Корольова Наталія Анатоліївна, Колмиков Максим Миколайович

Формула / Реферат

Пристрій для реалізації швидкого перетворення Хартлі, що містить блок оперативної пам'яті, блок постійної пам'яті, перемножувач, накопичуючий суматор, блок управління, до складу якого входять генератор тактових імпульсів, тригер, перший та другий лічильники, дешифратор, одновібратор, перший, другий, третій та четвертий елементи І, який відрізняється тим, що додатково введені три елементи І в блоці управління та усунуті зайві елементи, при цьому введені нові зв'язки у всьому пристрої, вхід запуску пристрою з'єднаний з входом блока управління, вхід дозволу читання блока оперативної пам'яті з'єднаний з першим виходом блока управління, адресні входи блока оперативної пам'яті та блока постійної пам'яті з'єднані з другим виходом блока управління, вихід блока оперативної пам'яті з'єднаний з першим входом перемножувача, вихід якого з'єднаний з входом накопичуючого суматора, вихід блока постійної пам'яті з'єднані з другим входом перемножувача, третій вихід блока управління з'єднаний з входом управління читанням блока оперативної пам'яті, з входом дозволу читанням блока постійної пам'яті, з входом управління множенням елементів в перемножувачі, з входом управління накопичуючого суматора, в блоці управління вхід з'єднаний з входом переводу тригера в одиницю, вихід тригера з'єднаний з входом генератора тактових імпульсів, вихід якого з'єднаний з рахунковим входом другого лічильника та другим входом першого, другого, третього та четвертого елементів І, перший вихід другого лічильника (молодший розряд) з'єднаний з першим входом дешифратора (молодший розряд), другий вихід другого лічильника (старший розряд) з'єднаний з другим входом дешифратора (старший розряд) та входом четвертого елементу І, вихід якого з'єднаний з входом одновібратора, вихід якого з'єднаний з входом скидання другого лічильника і рахунковим входом першого лічильника, вихід переповнення першого лічильника з'єднаний з входом скидання тригера, виходи лічення першого лічильника з'єднані з другим виходом блока управління, перший вихід дешифратора з'єднаний з першим входом першого елемента І та з першим виходом блока управління, другий вихід дешифратора з'єднаний з першим входом другого елемента І, третій вихід дешифратора з'єднаний з першим входом третього елемента І, вихід першого елемента І по третьому виходу блока управління з'єднаний з входом дозволу читання блока постійної пам'яті та з входом управління читанням блока оперативної пам'яті, вихід другого елемента І по третьому виходу блока управління з'єднаний з входом управління перемноженням елементів перемножувача, вихід третього елемента І по третьому виходу блока управління з'єднаний з входом управління накопичуючого суматора.

Текст

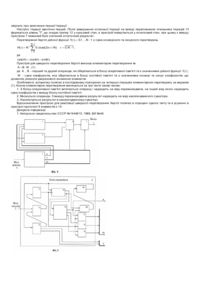

Пропонований винахід відноситься до галузі автоматики й обчислювальної техніки і може бути використаний в системах обробки і відображення інформації. Найбільш близьким до запропонованого технічним рішенням, обраним як прототип, є "Пристрій для реалізації швидкого перетворення Хартлі" [1], який містить блок пам'яті, блок постійної пам'яті, блок управління, перший та другий накопичуючий суматор, елемент АБО, перший, другий та третій комутатори, перший та другий лічильники, перемножувач, перший та другий регістри зсуву. Блок управління містить: одновібратор, елемент АБО, тригер обробки, лічильник ітерацій, генератор тактових імпульсів, накопичуючий суматор, двійковий лічильник, дешифратор нульової операції, елемент АБО, еле мент АБО-НІ, елемент І. Недоліком пристрою-прототипу є необхідність дворазового множення елементів, що в свою чергу виражається у низькій швидкодії пристрою. В основу винаходу поставлена задача створити такий пристрій для реалізації швидкого перетворення Хартлі, який дозволить зменшити час одержання результату. Поставлена задача вирішується за рахунок того, що у пристрої-прототипі, що містить блок пам'яті, блок постійної пам'яті, блок управління, перший та другий накопичуваючий суматор, елемент АБО, перший, другий та третій комутатори, перший та другий лічильники, перемножувач, перший та другий регістри зсуву, усун уті регістри зсуву, елемент АБО, лічильники, комутатори, один накопичуючий суматор, в блоці управлінні, що включає одновібратор, елемент АБО, тригер обробки, лічильник ітерацій, генератор тактових імпульсів, накопичуючий суматор, двійковий лічильник, дешифратор нульової операції, елемент АБО, елемент АБО-НІ, елемент І, відповідно усун уті два елементи АБО, накопичуючий суматор, елемент АБО-НІ, та додатково введені нові зв'язки у всьому пристрої та три елементи І в блоці управління. Технічний результат, який може бути отриманий при здійсненні винаходу, полягає в спрощенні пристрою для реалізації швидкого перетворення Хартлі та підвищенні його швидкодії. На фіг.1 приведена блок-схема пристрою. На фіг.2 приведена структурна схема блоку управління пристрою. Запропонований пристрій для реалізації швидкого перетворення Хартлі (фіг.1) містить: блок оперативної пам'яті 1, блок постійної пам'яті 2, блок управління 3, перемножувач 4, накопичуючий суматор 5, вхід запуску пристрою 6, ви хід 7, виходи блоку управління 8, 9 та 10, причому вхід запуску пристрою 6 з'єднаний з входом блоку управління 3. Вхід дозволу читання блоку оперативної пам'яті 1 з'єднаний з виходом 8 блоку управління 3. Адресні входи блоку оперативної пам'яті 1 та блоку постійної пам'яті 2 з'єднані з виходом 9 блоку управління 3. Вихід блоку оперативної пам'яті 1 з'єднаний з першим входом перемножувача 4. Вихід блоку постійної пам'яті 2 з'єднаний з другим входом перемножувача 4 відповідно. Вихід перемножувача 4 з'єднаний з входом накопичуваючого суматора 5. Вихід суматора 5 є виходом пристрою 7. Вихід 10 блоку управління 3 з'єднаний з входом управління читанням блоку оперативної пам'яті 1, з входом дозволу читанням блоку постійної пам'яті 2, з входом управління множенням елементів в перемножувачі 4, з входом управління накопичуваючого суматора 5. Блок управління 3 пристрою для реалізації швидкого перетворення Хартлі (фіг.2) містить: генератор тактових імпульсів 11, тригер 12, лічильники 13 та 14, дешифратор 15, одновібратор 16, елементи І 17-20, причому вхід блоку управління 3 з'єднаний з входом переводу тригера 12 в одиницю, вихід тригеру 12 з'єднаний зі входом генератору тактових імпульсів 11, вихід якого з'єднаний з рахунковим входом лічильника 14 та другими входами елементів І 17-20. Перший вихід (молодший розряд) лічильника 14 з'єднаний з першим входом (молодший розряд) дешифратора 15. Другий вихід (старший розряд) лічильника 14 з'єднаний з входом елементу І 20 та др угим входом (старший розряд) дешифратора 15. Вихід елементу І 20 з'єднаний з входом одновібратора 16. Вихід одновібратора 16 з'єднаний з входом скидання лічильника 14 і рахунковим входом лічильника 13. Вихід переповнення лічильника 13 з'єднаний з входом скидання тригера 12. Виходи лічення лічильника 13 з'єднані через вихід 9 блоку управління 3 з адресними входами блоку оперативної пам'яті 1 та блоку постійної пам'яті 2. Перший вихід дешифратора 15 з'єднаний з першим входом елемента І 17 та через вихід 8 блоку управління 3 з входом дозволу читання блоку оперативної пам'яті 1, другий вихід дешифратора 15 з'єднаний з першим входом елемента І 18, третій вихід дешифратора 15 з'єднаний з першим входом елемента І 19. Вихід елемента 117 з'єднаний через перший розряд виходу 10 блоку управління 3 з входом дозволу читання блоку постійної пам'яті 2 та з входом управління читанням блоку оперативної пам'яті 1. Вихід елемента 118 з'єднаний через другий розряд виходу 10 блоку управління 3 з входом управління множенням операндів поданих на входи перемножувача 4. Вихід елемента 119 з'єднаний через третий розряд виходу 10 блоку управління 3 з входом управління накопичуваючого суматора 5. Робота запропонованого пристрою полягає в наступному. Перед початком роботи в блок оперативної пам'яті 1 записані операнди А та В в додатковому коді, а в блок постійні пам'яті 2 записана сума коефіцієнтів W1 та W2, накопичуючий суматор 5, лічильник ітерацій 13, лічильник тактів 14 і тригер 12 у нульовому стані. По сигналу "Запуск обробки", що надходить по входу пристрою 6, тригер 12 встановлюється в одиничний стан, сигнал "1" з виходу тригера обробки 12 надходить на вхід генератора тактових імпульсів 11, що починає формувати послідовність тактових імпульсів, що надходять на рахунковий вхід лічильника тактів 14 та другі входи елементів І 17 -1 20. На виході дешифратора 15 формується унітарний код такту, причому рівень "1" буде тільки на одному з чотирьох його ви ходів, з'єднаних з першими входами відповідних елементів І 17 -1 20. На першому такті формується рівень "1" на першому виході дешифратора 15, що дозволяє проходження тактового імпульсу з генератора 11 через вихід 10 блоку управління 3 на вхід управління блоку постійної пам'яті 2 та на тактовий вхід блоку оперативної пам'яті 1. На адресні входи блоку оперативної пам'яті 1 і блоку постійної пам'яті 2 через вихід 9 блоку управління 3 подається код адреси, що відповідає номеру ітерації, що задається лічильником ітерацій 13. Рівень "1" першого входу деши фратора 15 через вихід 8 блоку управління 3 дозволяє робити операцію читання даних із блоку оперативної пам'яті 1. Одночасно цей імпульс синхронізує передачу з блоку постійної пам'яті 2 суми коефіцієнтів на другий вхід перемножувача 4, на перший вхід якого надходить операнд із блоку оперативної пам'яті 1. На другому такті при надходженні через елемент І 18 виходу 10 блоку управління 3 тактового імпульсу результат множення суми коефіцієнтів і операнда формується на виході перемножувача 4. На четвертому такті кожної ітерації в суматорі 5 накопичується результат перетворення при надходженні через елемент І 19 виходу 10 блоку управління 3 тактового імпульсу. На рахунковий вхід лічильника ітерацій 13 з виходу одновібратора 16 надходить рахунковий імпульс, формований із заднього фронту старшого розряду лічильника тактів 14, при цьому вміст лічильника ітерацій 13 інкрементується, що свідчить про закінчення першої ітерації. Наступні ітерації ідентичні першій. Після завершення останньої ітерації на виході переповнення лічильника ітерацій 13 формується рівень "І", що скидає тригер 12 у нульовий стан, а пристрій повертається у початковий стан, при цьому з виходу пристрою 7 повинний бути зчитаний остаточний результат. Перетворення Хартлі дійсної функції f (t ), = 0,1K, N - 1 є сума косинусного та синусного перетворень N -1 å f( t)cas( 2pnt / N) H(n ) = N -1 n = 0, N - 1 , t -0 де cas( Q) = cos(Q) + sin(Q ) Пристрій для швидкого перетворення Хартлі виконує елементарне перетворення як A + B × W , (1) де A , B - перший та другий операнди, які зберігаються в блоці оперативної пам'яті та є значеннями дійсної функції f (t ) ; W - сума коефіцієнтів, яка зберігається в блоці постійної пам'яті та є значеннями косинус та синус коефіцієнтів, що дозволяє уникнути дворазового множення елементів. Особливість алгоритму полягає в послідовному повторенні на чотирьох ітераціях елементарних перетворень за виразом (1). Кожне елементарне перетворення виконується за три такти таким чином: 1. З блоку оперативної пам'яті витягається операнд і надходить на вхід перемножувача, на інший вхід якого надходить сума коефіцієнтів з виходу блоку постійної пам'яті. 2. Множуться операнди. З виходу перемножувача результат надходить на вхід накопичуваючого суматора. 3. Накопичується результат в накопичуваючому суматорі. Вдосконалення пристрою для реалізації швидкого перетворення Хартлі полягає в спрощені одного такту та в усуненні в пристрої прототипі 9 елементів з 14. Джерела інформації 1. Авторское свидетельство СССР №1444815, 1988, БИ №46.

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for the fast hartley transform

Автори англійськоюRuban Ihor Viktorovych, Dudenko Serhii Vasyliovych, Koroliova Nataliya Anatoliivna

Назва патенту російськоюУстройство для быстрого преобразования хартли

Автори російськоюРубан Игорь Викторович, Дуденко Сергей Васильевич, Королева Наталья Анатольевна

МПК / Мітки

МПК: G06F 15/00, G06F 17/14, G06F 7/04

Мітки: перетворення, пристрій, швидкого, хартлі, реалізації

Код посилання

<a href="https://ua.patents.su/2-64265-pristrijj-dlya-realizaci-shvidkogo-peretvorennya-khartli.html" target="_blank" rel="follow" title="База патентів України">Пристрій для реалізації швидкого перетворення хартлі</a>

Попередній патент: Хвильова енергетична установка

Наступний патент: Спосіб побудови стойки

Випадковий патент: Спосіб охолоджування безперервнолитого зливка в зоні вторинного охолоджування машини безперервного лиття заготовок