Арифметичний пристрій для виконання швидкого перетворення хартлі-фур’є

Формула / Реферат

Арифметичний пристрій для виконання швидкого перетворення Хартлі-Фур'є, що містить два помножувачі комплексних чисел, перший комутатор та шість суматорів-віднімачів, причому перший та другий входи першого, другого та четвертого суматорів-віднімачів підключені відповідно до першого, п'ятого, другого, шостого, четвертого та восьмого входів операндів пристрою, виходи суми з першого по четвертий суматорів-віднімачів є відповідно першим, другим, третім та четвертим виходами результату пристрою, перший та другий входи першого помножувача комплексних чисел підключені відповідно до виходу суми п'ятого суматора-віднімача та першого виходу першого комутатора, вхід керування якого є першим входом задавання типу операції пристрою, третій та четвертий входи першого помножувача комплексних чисел підключені відповідно до першого та другого входів задавання фазових множників пристрою, перший та другий виходи другого помножувача комплексних чисел є відповідно сьомим та восьмим виходами результату пристрою, який відрізняється тим, що в пристрій введені другий, третій та четвертий комутатори, причому перший та другий входи третього суматора-віднімача підключені відповідно до сьомого та третього входів операндів пристрою, виходи різниці з першого по четвертий суматорів-віднімачів підключені відповідно до другого та першого входів п'ятого суматора-віднімача і першого та другого входів шостого суматора-віднімача, виходи суми та різниці якого підключені до других входів відповідно першого та другого комутаторів, виходи суми та різниці п'ятого суматора-віднімача підключені відповідно до першого входу третього комутатора та перших входів другого і четвертого комутаторів, перший та другий виходи другого комутатора підключені до перших входів відповідно першого комутатора та другого помножувача комплексних чисел, до другого входу якого підключений другий вихід першого комутатора, вхід керування якого з'єднаний з входами керування третього та четвертого комутаторів, третій та четвертий входи другого помножувача комплексних чисел підключені відповідно до першого та другого входів задавання фазових множників пристрою, перший та другий виходи першого помножувача комплексних чисел підключені до других входів відповідно третього та четвертого комутаторів, виходи яких є відповідно п'ятим та шостим виходами результату пристрою, вхід керування другого комутатора підключений до другого входу задавання типу операції пристрою.

Текст

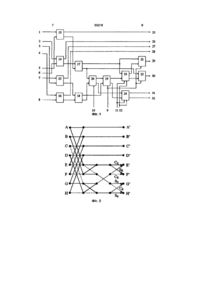

Арифметичний пристрій для виконання швидкого перетворення Хартлі-Фур'є, що містить два помножувачі комплексних чисел, перший комутатор та шість суматорів-віднімачів, причому перший та другий входи першого, другого та четвертого суматорів-віднімачів підключені ВІДПОВІДНО до першого, п'ятого, другого, шостого, четвертого та восьмого входів операнд їв пристрою, виходи суми з першого по четвертий суматорів-віднімачів є ВІДПОВІДНО першим, другим, третім та четвертим виходами результату пристрою, перший та другий входи першого помножувача комплексних чисел підключені ВІДПОВІДНО до виходу суми п'ятого суматоравіднімача та першого виходу першого комутатора, вхід керування якого є першим входом задавання типу операції пристрою, третій та четвертий входи першого помножувача комплексних чисел підключені ВІДПОВІДНО до першого та другого входів задавання фазових множників пристрою, перший та другий виходи другого помножувача комплексних чисел є ВІДПОВІДНО сьомим та восьмим виходами результату пристрою, який відрізняється тим, що в пристрій введені другий, Винахід належить до галузі цифрової обчислювальної техніки і може бути застосований у складі процесорів швидкого перетворення Хартлі-Фур'є (ШПХФ), що використовуються в пристроях обчислення спектрів, згорток та кореляційних функцій Відомий арифметичний пристрій процесора ШПХФ дійсних послідовностей [А с СССР №1594562, кл G 06 F 15/332, 1990], що містить перший помножувач комплексних чисел, суматор та віднімач Недоліком даного пристрою є низька третій та четвертий комутатори, причому перший та другий входи третього суматора-віднімача підключені ВІДПОВІДНО до сьомого та третього входів операнд їв пристрою, виходи різниці з першого по четвертий суматорів-віднімачів підключені ВІДПОВІДНО до другого та першого входів п'ятого суматора-віднімача і першого та другого входів шостого суматора-віднімача, виходи суми та різниці якого підключені до других входів ВІДПОВІДНО першого та другого комутаторів, виходи суми та різниці п'ятого суматора-віднімача підключені ВІДПОВІДНО до першого входу третього комутатора та перших входів другого і четвертого комутаторів, перший та другий виходи другого комутатора підключені до перших входів ВІДПОВІДНО першого комутатора та другого помножувача комплексних чисел, до другого входу якого підключений другий вихід першого комутатора, вхід керування якого з'єднаний з входами керування третього та четвертого комутаторів, третій та четвертий входи другого помножувача комплексних чисел підключені ВІДПОВІДНО до першого та другого входів задавання фазових множників пристрою, перший та другий виходи першого помножувача комплексних чисел підключені до других входів ВІДПОВІДНО третього та четвертого комутаторів, виходи яких є ВІДПОВІДНО п'ятим та шостим виходами результату пристрою, вхід керування другого комутатора підключений до другого входу задавання типу операції пристрою швидкодія, оскільки одночасно обробляється лише два операнда Найбільш близьким за технічною сутністю до пропонованого є арифметичний пристрій для виконання ШПХФ [А с СССР, №1795473, кл G 06 F 15/332, Бюл № 6,1993], що містить два помножувачі комплексних чисел, перший комутатор та шість суматорів-віднімачів, причому перший та другий входи першого, другого та четвертого суматорів-віднімачів підключені ВІДПОВІДНО до першого, п'ятого, другого, шостого, четвертого та восьмого входів операнд їв 00 со ю 53218 пристрою, виходи суми з першого по четвертий суматорів-віднімачів є ВІДПОВІДНО першим, другим, третім та четвертим виходами результату пристрою, перший та другий входи першого помножувача комплексних чисел підключені ВІДПОВІДНО до виходу суми п'ятого суматоравіднімача та першого виходу першого комутатора, вхід керування якого є першим входом завдання типу операції пристрою, третій та четвертий входи першого помножувача комплексних чисел підключені ВІДПОВІДНО до першого та другого входів завдання фазових множників пристрою, перший та другий виходи другого помножувача комплексних чисел є ВІДПОВІДНО сьомим та восьмим виходами результату пристрою Недоліком даного пристрою є складність, обумовлена великою КІЛЬКІСТЮ ВХОДІВ завдання фазових множників та великим об'ємом пам'яті, необхідним для їх збереження В основу винаходу поставлено задачу створення арифметичного пристрою для виконання ШПХФ, котрий реалізує базову операцію алгоритму ШПХФ з спряженими парами з проріджуванням по частоті, в якому за рахунок введення нових блоків разом з їх зв'язками досягається спрощення пристрою внаслідок зменшення КІЛЬКОСТІ входів завдання фазових множників та об'єму пам'яті, необхідного для їх збереження Поставлена задача досягається за рахунок того, що в арифметичний пристрій для виконання ШПХФ, що містить два помножувачі комплексних чисел, перший комутатор та шість суматоріввіднімачів, причому перший та другий входи першого, другого та четвертого суматоріввіднімачів підключені ВІДПОВІДНО ДО першого, п'ятого, другого, шостого, четвертого та восьмого входів операндів пристрою, виходи суми з першого по четвертий суматорів-віднімачів є ВІДПОВІДНО першим, другим, третім та четвертим виходами результату пристрою, перший та другий входи першого помножувача комплексних чисел пщключені ВІДПОВІДНО до виходу суми п'ятого суматора-віднімача та першого виходу першого комутатора, вхід керування якого є першим входом завдання типу операції пристрою, третій та четвертий входи першого помножувача комплексних чисел підключені ВІДПОВІДНО до першого та другого входів завдання фазових множників пристрою, перший та другий виходи другого помножувача комплексних чисел є ВІДПОВІДНО сьомим та восьмим виходами результату пристрою, введені другий, третій та четвертий комутатори, причому перший та другий входи третього суматора-віднімача підключені ВІДПОВІДНО до сьомого та третього входів операндів пристрою, виходи різниці з першого по четвертий суматорів-віднімачів підключені ВІДПОВІДНО до другого та першого входів п'ятого суматора-віднімача і першого та другого входів шостого суматора-віднімача, виходи суми та різниці якого підключені до других входів ВІДПОВІДНО першого та другого комутаторів, виходи суми та різниці п'ятого суматора-віднімача підключені ВІДПОВІДНО до першого входу третього комутатора та перших входів другого і четвертого комутаторів, перший та другий виходи другого комутатора підключені до перших входів ВІДПОВІДНО першого комутатора та другого помножувача комплексних чисел, до другого входу якого підключений другий вихід першого комутатора, вхід керування якого з'єднаний з входами керування третього та четвертого комутаторів, третій та четвертий входи другого помножувача комплексних чисел підключені ВІДПОВІДНО до першого та другого входів завдання фазових множників пристрою, перший та другий виходи першого помножувача комплексних чисел підключені до других входів ВІДПОВІДНО третього та четвертого комутаторів, виходи яких є ВІДПОВІДНО п'ятим та шостим виходами результату пристрою, вхід керування другого комутатора підключений до другого входу завдання типу операції пристрою Введення в пристрій другого, третього та четвертого комутаторів разом з їх зв'язками дозволило реалізувати базову операцію алгоритму ШПХФ з спряженими парами з проріджуванням по частоті, внаслідок чого досягнуто спрощення пристрою за рахунок зменшення КІЛЬКОСТІ ВХОДІВ завдання фазових множників та об'єму пам'яті, необхідного для їх збереження Пропонований пристрій, як і прототип, обробляє одночасно ВІСІМ операндів, але вимагає ВДВІЧІ меншої КІЛЬКОСТІ входів завдання фазових множників і ВДВІЧІ меншого об'єму пам'яті для їх збереження На фіг 1 представлена блок-схема арифметичного пристрою для виконання ШПХФ, на фіг 2-5 - граф-схеми базових операцій алгоритму швидкого перетворення Хартлі (ШПХ) різних типів, на фіг 6 - граф-схема алгоритму ШПХ з спряженими парами з проріджуванням по частоті для N=32, де N - КІЛЬКІСТЬ ВІДЛІКІВ оброблюваної ПОСЛІДОВНОСТІ Пристрій (фиг 1) містить входи 1-8 операндів, входи 9-10 завдання типу операції, входи 11-12 завдання фазових множників, суматори-віднімачі 13-18, комутатори 19-22, помножувачі 23 і 24 комплексних чисел, виходи 25-32 результату Перший та другий входи з першого по четвертий суматорів-віднімачів 13-16 підключені ВІДПОВІДНО до першого 1, п'ятого 5, другого 2, шостого 6, сьомого 7, третього 3, четвертого 4 та восьмого 8 входів операндів пристрою Виходи суми з першого по четвертий суматорів-віднімачів 13-16 є ВІДПОВІДНО першим, другим, третім та четвертим виходами 25-28 результату пристрою, а виходи різниці підключені ВІДПОВІДНО до другого та першого входів п'ятого суматора-віднімача 17 і першого та другого входів шостого суматоравіднімача 18 Виходи суми та різниці п'ятого суматора-віднімача 17 підключені до перших входів ВІДПОВІДНО першого помножувача 23 комплексних чисел і третього комутатора 21 та другого і четвертого комутаторів 20, 22 Виходи суми та різниці шостого суматора-віднімача 18 підключені до других входів ВІДПОВІДНО першого та другого комутаторів 19-20 Перший та другий виходи другого комутатора 20 підключені до перших входів ВІДПОВІДНО першого комутатора 19 та другого помножувача 24 комплексних чисел, до другого входу якого підключений другий вихід 53218 першого комутатора 19, перший вихід якого підключений до другого входу першого помножувача 23 комплексних чисел Вхід керування першого комутатора 19 з'єднаний з входами керування третього та четвертого комутаторів 21-22 і є першим входом 9 завдання типу операції пристрою Вхід керування другого комутатора 20 підключений до другого входу 10 завдання типу операції пристрою Треті та четверті входи першого та другого помножувачів 23-24 комплексних чисел підключені ВІДПОВІДНО до першого та другого входів 11-12 завдання фазових множників пристрою Перший та другий виходи першого помножувача 23 комплексних чисел підключені до других входів ВІДПОВІДНО третього та четвертого комутаторів 21-22, виходи яких є ВІДПОВІДНО п'ятим та шостим виходами 29-30 результату пристрою Перший та другий виходи другого помножувача 24 комплексних чисел є ВІДПОВІДНО сьомим та восьмим виходами 31-32 результату пристрою Алгоритм ШПХФ з спряженими парами з проріджуванням по частоті містить декілька типів базових операцій, котрі виконуються згідно з графсхемами, зображеними на фіг 2-5, на яких прийняті такі позначення А, В, С, D, E, F, G, Н ВХІДНІ значення базової операції, А', В', С , D', Е', F', G', Н' -ВИХІДНІ значення базової операції, безперервна ЛІНІЯ позначає операцію додавання, пунктирна ЛІНІЯ - операцію віднімання, ЛІНІЯ З стрілкою на КІНЦІ - операцію множення на значення, розташоване біля неї Порядок вхідних та вихідних значень на граф-схемах базових операцій визначає спосіб їх комутації (фіг 6) Пристрій працює наступним чином По входам 1-8 в пристрій поступають ВХІДНІ операнди, а по входам 11-12 - фазові множники На суматорах-віднімачах 13-18 виконуються операції додавання та віднімання у ВІДПОВІДНОСТІ З виразами L+M L-M, де L, М - ВХІДНІ значення суматорів-віднімачів На помножувачах 23-24 комплексних чисел виконуються операції множення значень, що поступають на перший і другий входи помножувачів, на фазові множники, що поступають на третій і четвертий входи помножувачів, у ВІДПОВІДНОСТІ З виразами XI+YR XR-YI, де X Y - значення на першому та другому входах помножувачів, І, R - значення фазових множників Комутатори 19-20 пропускають дані, що поступають на їх входи, прямо або навхрест в залежності від значення на входах 9-10 завдання типу операції при нульовому значенні - прямо, при одиничному - навхрест Комутатори 21-22 пропускають значення з перших входів при нульовому значенні на вході 9 завдання типу операції та з других входів - при одиничному На граф-схемі алгоритму ШПХ (фіг 6) базові операції позначені прямокутниками, всередині яких перші дві цифри визначають значення ВІДПОВІДНО на входах 9 і 10 завдання типу операції, третя та четверта цифри визначають значення параметрів К та N, котрі використовуються для визначення фазових множників Для K=1,N/8-1 фазовими множниками є тригонометричні к о е ф і ц і є н т и C K = C O S ( 2 T I K / N ) т а S K = s m ( 2 7 i K / N ) ( ф і г 2) Для К=0 значення фазових множників зображені на граф-схемах базових операцій (фіг 3-5) Графсхеми базових операцій на фіг 4-5 відображають виконання ВІДПОВІДНО чотирьохточкового (N=4) та двох двохточкових перетворень (N=2), котрі виконуються на останньому етапі алгоритму перетворення (фіг 6) На деякі входи цих базових операцій подаються нулі, а деякі виходи не використовуються Зв'язок між входами та виходами операцій показаний на фіг 6 базових 53218 13 25 26 27 28 14 21 29 22 ЗО 17 23 15 20 19 24 IS 10 Фіг. 1 A В Н Фіг. 2 9 1112 31 32 53218 Фіг. З Фіг. 4 Фіг. 5 10 11 53218 31 ФІГ. 6 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)236-47-24 12

ДивитисяДодаткова інформація

Назва патенту англійськоюArithmetic unit for fast hartley-fourier transform

Автори англійськоюVolynets Viktor Ivanovych

Назва патенту російськоюАрифметическое устройство для быстрого преобразования хартли-фурье

Автори російськоюВолынец Виктор Иванович

МПК / Мітки

МПК: G06F 17/14

Мітки: виконання, хартлі-фур'є, пристрій, швидкого, арифметичний, перетворення

Код посилання

<a href="https://ua.patents.su/6-53218-arifmetichnijj-pristrijj-dlya-vikonannya-shvidkogo-peretvorennya-khartli-fureh.html" target="_blank" rel="follow" title="База патентів України">Арифметичний пристрій для виконання швидкого перетворення хартлі-фур’є</a>

Попередній патент: Процесор швидкого перетворення хартлі дійсних послідовностей

Наступний патент: Пристрій для формування адрес процесора швидкого перетворення фур’є

Випадковий патент: Спосіб регулювання динамічного моменту інерції маховика