Пристрій для вибору мінімального числа

Номер патенту: 65036

Опубліковано: 25.11.2011

Автори: Дорошенко Юрій Іванович, Чечко Олександр Ігорович, Рисований Олександр Миколайович, Шостак Анатолій Васильович

Формула / Реферат

Пристрій для вибору мінімального числа, що містить групу елементів І, вхідний елемент І, m´n лічильників, де m - кількість рядків, n - кількість стовпців у матричному масиві чисел, вихідний лічильник, m´n забороняючих елементів І, елемент І-НІ, виходи елементів І групи є виходами пристрою, другий вхід вхідного елемента І з'єднаний з входом тактових імпульсів пристрою, вихід вхідного елемента І з'єднаний з другими входами m´n забороняючих елементів І і входом додавання вихідного лічильника, виходи m´n забороняючих елементів І з'єднані з входами віднімання відповідних m´n лічильників, виходи вихідного лічильника порозрядно з'єднані з другими входами елементів І групи, вихід елемента І-НІ з'єднаний з першими входами елементів І групи і з інверсним входом вхідного елемента І, перші входи m´n забороняючих елементів І з'єднані з інверсними виходами ознаки нуля відповідних m´n лічильників, які з'єднані також з відповідними входами елемента І-НІ, вихід якого є виходом сигналу "Кінець" пристрою, входи m´n лічильників з'єднані з відповідними інформаційними входами пристрою, входи скиду m´n лічильників і вихідного лічильника з'єднані з входом скиду пристрою, який відрізняється тим, що в нього введено m´n дозволяючих елементів І та m´n RS-тригерів, причому інверсні виходи ознаки нуля m´n лічильників з'єднані відповідно з першими входами m´n дозволяючих елементів І, вихід елемента І-НІ з'єднаний з другими входами m´n дозволяючих елементів І, прямі виходи m´n RS-тригерів з'єднані з відповідними виходами ознак пристрою, їх S-входи з'єднані з входом встановлення пристрою, R-вхід кожного з m´n RS-тригерів з'єднаний з виходом відповідного дозволяючого елемента І.

Текст

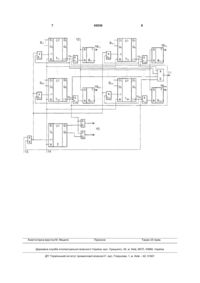

Пристрій для вибору мінімального числа, що містить групу елементів І, вхідний елемент І, mn лічильників, де m - кількість рядків, n - кількість стовпців у матричному масиві чисел, вихідний лічильник, mn забороняючих елементів І, елемент І-НІ, виходи елементів І групи є виходами пристрою, другий вхід вхідного елемента І з'єднаний з входом тактових імпульсів пристрою, вихід вхідного елемента І з'єднаний з другими входами mn забороняючих елементів І і входом додавання вихідного лічильника, виходи mn забороняючих елементів І з'єднані з входами віднімання відповідних mn лічильників, виходи вихідного лічильника U 2 (19) 1 3 групи є виходами пристрою, другий вхід вхідного елемента І з'єднаний з входом тактових імпульсів пристрою, вихід вхідного елемента І з'єднаний з другими входами mn забороняючих елементів І і входом додавання вихідного лічильника, виходи mn забороняючих елементів І з'єднані з входами віднімання відповідних mn лічильників, виходи вихідного лічильника порозрядно з'єднані з другими входами елементів І групи, вихід елемента І-НІ з'єднаний з першими входами елементів І групи і з інверсним входом вхідного елемента І, перші входи mn забороняючих елементів І з'єднані з інверсними виходами ознаки нуля відповідних mn лічильників, які з'єднані також з відповідними входами елемента І-НІ, вихід якого є виходом сигналу "Кінець" пристрою, входи mn лічильників з'єднані з відповідними інформаційними входами пристрою, входи скиду mn лічильників і вихідного лічильника з'єднані з входом скиду пристрою. Недоліком даного пристрою є його обмежені функціональні можливості через те, що він виконує тільки вибір мінімального числа серед елементів матричного масиву І не може визначити його місце розташування. В основу корисної моделі поставлено задачу створення пристрою для вибору мінімального числа серед елементів матричного масиву, в якому за рахунок введення нових елементів та зв'язків розширюються його функціональні можливості через визначення не тільки величини мінімального числа, але й його місце розташування серед елементів матричного масиву. Поставлена задача досягається тим, що у пристрій для вибору мінімального числа, який містить групу елементів І, вхідний елемент І, mn лічильників, де m - кількість рядків, n - кількість стовпців у матричному масиві чисел, вихідний лічильник, mn забороняючих елементів І, елемент І-НІ, виходи елементів І групи є виходами пристрою, другий вхід вхідного елемента І з'єднаний з входом тактових імпульсів пристрою, вихід вхідного елемента І з'єднаний з другими входами mn забороняючих елементів І і входом додавання вихідного лічильника, виходи mn забороняючих елементів І з'єднані з входами віднімання відповідних mn лічильників, виходи вихідного лічильника порозрядно з'єднані з другими входами елементів І групи, вихід елемента І-НІ з'єднаний з першими входами елементів І групи і з інверсним входом вхідного елемента І, перші входи mn забороняючих елементів І з'єднані з інверсними виходами ознаки нуля відповідних mn лічильників, які з'єднані також з відповідними входами елемента АБОНІ, вихід якого є виходом сигналу "Кінець" пристрою, входи mn лічильників з'єднані з відповідними інформаційними входами пристрою, входи скиду mn лічильників і вихідного лічильника з'єднані з входом скиду пристрою, згідно з корисною моделлю введено mn дозволяючих елементів І та mn RS-тригерів, причому інверсні виходи ознаки нуля mn лічильників з'єднані відповідно з першими входами mn дозволяючих елементів І, вихід елемента І-НІ з'єднаний з другими входами mn дозволяючих елементів І, прямі виходи mn RS 65036 4 тригерів з'єднані з відповідними виходами ознак пристрою, їх S-входи з'єднані з входом встановлення пристрою, R-вхід кожного з mn RS-тригерів з'єднаний з виходом відповідного дозволяючого елемента І. На фіг. зображено структурну схему пристрою для вибору мінімального числа. Пристрій для вибору мінімального числа містить mn лічильників 111, ..., lmn (де mn - кількість елементів у матричному масиві чисел), вихідний лічильник 2, елемент І-НІ 3, вхідний елемент І 4, mn забороняючих елементів І 511, ..., 5mn, групу елементів І 61, ..., 6k (де k -розрядність чисел масиву), mn дозволяючих елементів І 711, ..., 7mn та mn RS-тригерів 811, ..., 8mn, групу інформаційних входів 911, ... ,9mn пристрою, виходи 10 пристрою, вихід 11 сигналу "Кінець" пристрою, вхід 12 встановлення пристрою, вхід 13 тактових імпульсів пристрою, вхід 14 скиду, інверсні виходи 1511, ..., 15mn ознаки нуля mn лічильників 111, ..., 1mn та виходи 1611, ..., 16mn ознак пристрою. Інверсний вхід вхідного елемента І 4 з'єднаний з виходом елемента I-НІ 3, його другий вхід з'єднаний з входом 13 тактових імпульсів пристрою, а його вихід з'єднаний з другими входами забороняючих елементів 511, ..., 5mn і входом додавання вихідного лічильника 2, виходи якого порозрядно з'єднані з другими входами елементів І 61, ..., 6k групи. Виходи забороняючих елементів І 511, ..., 5mn з'єднані з входами віднімання відповідних лічильників 111, ..., 1mn інверсні виходи 1511, ..., 15mn ознаки нуля яких з'єднані з входами відповідного елемента І-НІ 3, вихід якого є виходом 11 сигналу "Кінець" пристрою. Інверсні виходи 1511, ..., 15mn ознаки нуля лічильників 111, ..., 1mn з'єднані також відповідно з першими входами забороняючих елементів І 511, ..., 5mn. Входи 911, ... ,9mn відповідних лічильників 111, ..., 1mn підключені до інформаційних входів пристрою відповідно, вхід 14 скиду пристрою підключений до входів скиду лічильників 111, ..., 1mn i вихідного лічильника 2. Вихід елемента І-НІ 3 з'єднаний з першими входами відповідних елементів І 61 ..., 6k групи, виходи яких є виходами 10 пристрою. Інверсні виходи 1511, ..., 15mn ознаки нуля mn лічильників 111, ..., 1mn з'єднані відповідно з першими входами mn дозволяючих елементів І 711, ..., 7mn, вихід елемента І-НІ 3 з'єднаний з другими входами mn дозволяючих елементів І 711, ..., 7mn, прямі виходи mn RS-тригерів 811, ..., 8ті1 з'єднані з відповідними виходами ознак пристрою 16ц, ..., 16ІШ, їх S-входи з'єднані з входом встановлення пристрою 12, R-вхід кожного з mn RS-тригерів 811, ..., 8mn з'єднаний з виходом відповідного дозволяючого елемента І 711,..., 7mn. Пристрій для вибору мінімального числа працює таким чином. Спочатку лічильники 111, ..., 1mn і вхідний лічильник 2 встановлюють у початковий (нульовий) стан за одиничним сигналом на вході 14 скиду пристрою, який подають на їх входи скиду, а RSтригери 811, ..., 8mn встановлюють в одиничний 5 стан за одиничним сигналом на вході 12 встановлення пристрою, який подають на їх S-входи. Потім у лічильники 111, ..., 1mn по їх інформаційних входах 911, ... , 9mn відповідно записують матричний масив mn чисел. На виходах дозволяючих елементів І 711, ..., 7mn та елемента І-НІ 3 присутній нульовий сигнал, так як вміст лічильників 111, ..., lmn не дорівнює нулю І на їх інверсних виходах 1511, ..., 15mn ознаки нуля присутні одиничні сигнали. Таким чином, вхідний елемент І 4 і забороняючі елементи 511, ..., 5mn відкриті. На вхід 13 пристрою подають тактові імпульси, які через відкритий вхідний елемент І 4 поступають на вхід додавання вихідного лічильника 2 і через відкриті забороняючі елементи І 511, ..., 5mn на входи віднімання відповідних лічильників 111, ..., 1mn. При цьому вміст лічильників 111, ..., 1mn зменшується, а вміст вихідного лічильника 2 -збільшується одночасно на одиницю з приходом кожного тактового імпульсу. Коли на вхід 13 пристрою буде подано кількість тактових імпульсів, що відповідає значенню мінімального числа серед чисел, що були записані в лічильниках 111, ..., 1mn, а тепер сформоване у вихідному лічильнику 2, вміст лічильника 1ij, де i=1, ..., m, j=1, ..., n, в якому записане мінімальне число, стане дорівнювати нулю, на його інверсному виході 15,, ознаки нуля з'являється нульовий сигнал, що закриває забороняючий елемент 5jj і відповідно, вхід віднімання лічильника 1ij. Одночасно нульовий сигнал з інверсного виходу 15ij ознаки нуля лічильника 1ij подається на відповідний вхід дозволяючoго елемента І 7ij, та на вхід елемента ІНІ 3, сигнал на виході якого з'являється одиничний сигнал. Отже, на виходах всіх дозволяючих елементів І 711, ..., 7mn, крім дозволяючого елемента І 7ij, формуються одиничні сигнали, оскільки на їх входах присутні одиничні сигнали, i тільки на виході до 65036 6 зволяючого елемента І 7jj присутній нульовий сигнал, який подається на R-вхід RS-тригера 8jj і залишає його в одиничному стані. Таким чином, на виході 16jj ознаки пристрою формується одиничний сигнал. Всі інші RS-тригери 811, ..., 8mn скидаються у нульовий стан за одиничним сигналом на їх Rвходах. Одночасно одиничний сигнал з виходу елемента І-.НІ 3 припинить надходження тактових імпульсів через вхідний елемент І 4, будучи поданий на його інверсний вхід. Тактові імпульси на входи віднімання лічильників 111, ..., 1mn через закриті забороняючі елементи І 511, ..., 5mn і на вхід додавання вихідного лічильника 2 не поступають. При цьому у вихідному лічильнику 2 зафіксовано значення мінімального числа серед чисел матричного масиву. Отже, на виході елемента І-НТ 3 зафіксований одиничний сигнал, який, будучи поданий на перші входи елементів 61,...,6k групи, дозволяє проходження через них на виходи 10 пристрою інформації з виходів вихідного лічильника 2, тобто значення мінімального числа серед елементів матричного масиву чисел. Таким чином здійснюється визначення не тільки величини мінімального числа серед елементів матричного массиву, але й його місце розташування за одиничним сигналом на виході 16ij, i=1, ..., m, j=1, ..., n ознаки пристрою. Отже, роботу пристрою для вибору мінімального числа закінчено, на виході 11 сигналу "Кінець" пристрою, який з'єднаний з виходом елемента I-НІ 3, присутній одиничний сигнал. Запропонований пристрій для вибору мінімального числа має розширені функціональні можливості за рахунок здатності визначення не тільки величини мінімального числа, але й його місце розташування серед елементів матричного масиву. 7 Комп’ютерна верстка М. Мацело 65036 8 Підписне Тираж 23 прим. Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for selection of minimum number

Автори англійськоюShostak Anatolii Vasyliovych, Doroshenko Yurii Ivanovych, Rysovanyi Oleksandr Mykolaiovych, Chechko Oleksandr Ihorovych

Назва патенту російськоюУстройство для выбора минимального числа

Автори російськоюШостак Анатолий Васильевич, Дорошенко Юрий Иванович, Рисованый Александр Николаевич, Чечко Александр Игоревич

МПК / Мітки

МПК: G06F 7/08

Мітки: пристрій, мінімального, вибору, числа

Код посилання

<a href="https://ua.patents.su/4-65036-pristrijj-dlya-viboru-minimalnogo-chisla.html" target="_blank" rel="follow" title="База патентів України">Пристрій для вибору мінімального числа</a>

Попередній патент: Пристрій для вибору екстремальних чисел

Наступний патент: Спосіб лікування дорослих хворих з соматоформними розладами

Випадковий патент: Абразивно-доводочна паста