Генератор компенсувального сигналу

Номер патенту: 71304

Опубліковано: 10.07.2012

Автори: Кириленко Дмитро Олегович, Азаров Олексій Дмитрович, Дудник Олександр Вікторович

Формула / Реферат

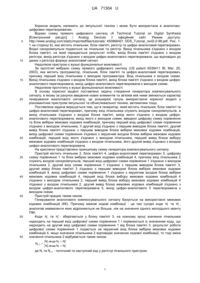

Генератор компенсувального сигналу, що містить лічильник, блок пам′яті та цифро-аналоговий перетворювач, причому вхід лічильника є входом схеми, вихід блока пам'яті з'єднано з входом цифро-аналогового перетворювача, вихід якого є виходом схеми, який відрізняється тим, що введено цифрову схему порівняння та блок вибірки межових кодових комбінацій, причому перший вхід цифрової схеми порівняння з'єднано з виходом лічильника, її другий вхід з'єднано з першим виводом блока пам'яті, другий вивід якого з'єднано з першим виводом блока вибірки межових кодових комбінацій, вихід цифрової схеми порівняння з'єднано з керуючим входом блока вибірки межових кодових комбінацій, перший вхід блока якого з'єднано з виходом лічильника, перший вивід блока вибору межових кодових комбінацій з'єднано з входом лічильника, його другий вивід з'єднано з входом цифро-аналогового перетворювача.

Текст

Реферат: UA 71304 U UA 71304 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах. Відомо схему прямого цифрового синтезу (A Technical Tutorial on Digital Synthesis [Електронний ресурс] / Analog Devices // офіційний сайт. Режим доступу: http://www.analog.com/static/importedfiles/tutorials/ 450968421 DDS_Tutorial_revl2-2-99.pdf. Рис. 11 на сторінці 6), яка містить лічильник, блок пам'яті, регістр та цифро-аналоговий перетворювач. Вхідні синхроімпульси подаються на лічильник та регістр. Вихід лічильника з'єднано з входом блока пам'яті, на який передається результат лічби, вихід блока пам'яті з'єднано з входом регістра, вихід регістра з'єднано з входом цифро-аналогового перетворювача, що відповідно до даних з регістра формує аналоговий сигнал. Недоліком пристрою є вузькі функціональні можливості. За прототип вибрано схему прямого цифрового синтезу (US patent 6539411 Bl, Mar. 25, 2003), яка містить програматор, лічильник, блок пам'яті та цифро-аналоговий перетворювач, причому перший вхід лічильника є виходом програматора. Вхід лічильника є входом схеми. Вихід лічильника з'єднано з входом блока пам'яті, вихід блока пам'яті з'єднано з входом цифроаналогового перетворювача, вихід цифро-аналогового перетворювача є виходом схеми. Недоліком прототипу є вузькі функціональні можливості. В основу корисної моделі поставлено задачу створення генератора компенсувального сигналу, в якому за рахунок введення нових елементів та зв'язків між ними змінюється характер генерування аналогового сигналу, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що в генератор, який містить лічильник, блок пам'яті та цифро-аналоговий перетворювач, причому вхід лічильника служить входом синхроімпульсів, а вихід лічильника з'єднано з входом блока пам'яті, вихід якого з'єднано з входом цифроаналогового перетворювача, вихід якого є виходом схеми, введено цифрову схему порівняння та блок вибірки межових кодових комбінацій, причому перший вхід цифрової схеми порівняння з'єднано з виходом лічильника, її другий вхід з'єднано з першим виводом блока пам'яті, другий вивід блока пам'яті з'єднано з першим виводом блока вибірки межових кодових комбінацій, вихід цифрової схеми порівняння з'єднано з керуючим входом блока вибірки межових кодових комбінацій, перший вхід якого з'єднано з виходом лічильника, перший вивід блока вибору межових кодових комбінацій з'єднано з входом лічильника, його другий вивід з'єднано з входом цифро-аналогового перетворювача. На кресленні представлено принципову схему генератора компенсувального сигналу. Пристрій містить лічильник 2, блок пам'яті 4, цифро-аналоговий перетворювач 5, цифрову схему порівняння 1 та блок вибірки межових кодових комбінацій 4, причому вхід лічильника 2 служить входом синхроімпульсів, перший вхід цифрової схеми порівняння 1 з'єднано з виходом лічильника 2, другий вхід схеми порівняння 1 з'єднано з першим виводом блока пам'яті 3, другий вивід блока пам'яті 3 з'єднано з першим виводом блока вибірки межових кодових комбінацій 4, вихід цифрової схеми порівняння 1 з'єднано з керуючим входом блока вибірки межових кодових комбінацій 4, перший вхід блока вибору межових кодових комбінацій 4 з'єднано з виходом лічильника 2, перший вивід блока вибору межових кодових комбінацій 4 з'єднано з входом лічильника 2, другий вивід блока межових кодових комбінацій з'єднано з входом цифро-аналогового перетворювача 5, вихід цифро-аналогового 5 перетворювача є виходом схеми. Пристрій працює таким чином. Генерування аналогового компенсувального сигналу базується на використанні межових кодових комбінацій (КК). Причому межові кодові комбінації - це такі сусідні коди N та N , i i аналогові еквіваленти яких відрізняються не більше, ніж на значення одного молодшого кванту ПФІ. Коди N та N - зберігаються у блоку пам'яті 3, на кожному кроці значення лічильника i i надходить на перший вхід цифрової схеми порівняння 1 і порівнюється із значенням коду, що надходить на другий вхід цифрової схеми порівняння 1 від блока пам'яті 3, результат роботи цифрової схеми порівняння 1 подається на керуючий вхід блока вибірки межових кодових комбінацій 4, якщо значення лічильника 2 відповідає значенню кодової комбінації, то тоді зміна значення лічильника 2 відбувається таким чином: N, якщо Ni : N; i Ni1 i N, якщо Ni : N; i i де Ni та Ni+1 - поточний та наступний код у регістрі лічильного пристрою. 1 UA 71304 U 5 Якщо ж значення лічильника 2 не відповідає значенню кодової комбінації, то тоді зміна значення лічильника 2 відбувається за законом роботи лічильника 2. Дані з виходу лічильника 2 через блок вибірки межових кодових комбінацій 4 подаються на вхід цифро-аналогового перетворювача 5. На виході цифро-аналогового перетворювача 5 формується вихідний компенсувальний сигнал. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 Генератор компенсувального сигналу, що містить лічильник, блок пам′яті та цифро-аналоговий перетворювач, причому вхід лічильника є входом схеми, вихід блока пам'яті з'єднано з входом цифро-аналогового перетворювача, вихід якого є виходом схеми, який відрізняється тим, що введено цифрову схему порівняння та блок вибірки межових кодових комбінацій, причому перший вхід цифрової схеми порівняння з'єднано з виходом лічильника, її другий вхід з'єднано з першим виводом блока пам'яті, другий вивід якого з'єднано з першим виводом блока вибірки межових кодових комбінацій, вихід цифрової схеми порівняння з'єднано з керуючим входом блока вибірки межових кодових комбінацій, перший вхід блока якого з'єднано з виходом лічильника, перший вивід блока вибору межових кодових комбінацій з'єднано з входом лічильника, його другий вивід з'єднано з входом цифро-аналогового перетворювача. Комп’ютерна верстка А. Крижанівський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 2

ДивитисяДодаткова інформація

Назва патенту англійськоюCompensating signal generator

Автори англійськоюAzarov Oleksii Dmytrovych, Dudnyk Oleksandr Viktorovych, Kyrylenko Dmytro Olehovych

Назва патенту російськоюГенератор компенсирующего сигнала

Автори російськоюАзаров Алексей Дмитриевич, Дудник Александр Викторович, Кириленко Дмитрий Олегович

МПК / Мітки

МПК: H03K 3/011

Мітки: компенсувального, сигналу, генератор

Код посилання

<a href="https://ua.patents.su/4-71304-generator-kompensuvalnogo-signalu.html" target="_blank" rel="follow" title="База патентів України">Генератор компенсувального сигналу</a>

Попередній патент: Спосіб комплексної оцінки апоптозу ендокриноцитів панкреатичних острівців

Наступний патент: Спосіб комплексної оцінки проліферативної активності ендокриноцитів панкреатичних острівців

Випадковий патент: Спосіб очистки плавильно-формувального обладнання від полікапроаміда