Генератор компенсувального сигналу

Номер патенту: 70191

Опубліковано: 25.05.2012

Автори: Азаров Олексій Дмитрович, Дудник Олександр Вікторович

Формула / Реферат

Генератор компенсувального сигналу, що містить лічильник, блок пам'яті та цифро-аналоговий перетворювач, причому вхід лічильника є входом схеми, на який подаються синхроімпульси, вихід блока пам'яті з'єднано з входом цифро-аналогового перетворювача, вихід цифро-аналогового перетворювача є виходом схеми, який відрізняється тим, що введено дешифратор, причому вихід лічильника є входом дешифратора, а вихід дешифратора є входом блока пам'яті.

Текст

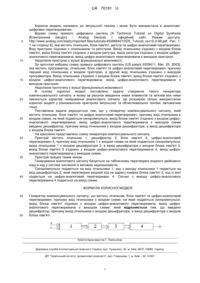

Реферат: UA 70191 U UA 70191 U 5 10 15 20 25 30 35 40 Корисна модель належить до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах. Відомо схему прямого цифрового синтезу [A Technical Tutorial on Digital Synthesis [Електронний ресурс] / Analog Devices // офіційний сайт. Режим доступу: http://www.analog.com/static/imported-files/tutorials/450968421DDS_Tutorial_rev12-2-99.pdf. Рис. 11 на сторінці 6], яка містить лічильник, блок пам'яті, регістр та цифро-аналоговий перетворювач. Вхід пристрою з'єднано з лічильником та регістром. Вихід лічильника з'єднано з входом блока пам'яті, вихід блока пам'яті з'єднано з входом регістра, вихід регістра з'єднано з входом цифроаналогового перетворювача, вихід цифро-аналогового перетворювача є виходом пристрою. Недоліком пристрою є вузькі функціональні можливості. За прототип вибрано схему прямого цифрового синтезу [US patent 6539411, Mar. 25, 2003], яка містить програматор, лічильник, блок пам'яті та цифро-аналоговий перетворювач, причому перший вхід лічильника є входом пристрою, а другий вхід лічильника з'єднано з виходом програматора. Вихід лічильника з'єднано з входом блока пам'яті, вихід блока пам'яті з'єднано з входом цифро-аналогового перетворювача, вихід цифро-аналогового перетворювача є виходом пристрою. Недоліком прототипу є вузькі функціональні можливості. В основу корисної моделі поставлено задачу створення такого генератора компенсувального сигналу, в якому за рахунок введення нових елементів та зв'язків між ними змінюється характер генерування аналогового сигналу. Це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у генератор компенсувального сигналу, який містить лічильник, блок пам'яті та цифро-аналоговий перетворювач, причому вхід лічильника є входом схеми, на який подаються синхроімпульси, вихід блока пам'яті з'єднано з входом цифроаналогового перетворювача, вихід цифро-аналогового перетворювача є виходом схеми введено дешифратор, причому вихід лічильника є входом дешифратора, а вихід дешифратора є входом блока пам'яті. На кресленні представлено схему генератора компенсувального сигналу. Пристрій містить лічильник 1, дешифратор 2, блок пам'яті 3, цифро-аналоговий перетворювач 4, причому вхід лічильника 1 є входом схеми на який подаються синхроімпульси, вихід лічильника 1 є входом дешифратора 2, а вихід дешифратора є входом блока пам'яті 3, вихід блока пам'яті 3 з'єднано з входом цифро-аналогового перетворювача 4, вихід цифроаналогового перетворювача є виходом схеми. Пристрій працює таким чином. Генерування аналогового сигналу базується на табличному перетворені вхідного двійкового коду в код у системі числення із ваговою надлишковістю. Синхроімпульси подаються на вхід лічильника 1, код з виходу лічильника 1 подається на вхід дешифратора 2, який перетворює вхідний код на адресу комірки блока пам'яті 3, код із якої подається на цифро-аналоговий перетворювач 4. Сигнал з виходу цифро-аналогового перетворювача 4 подається на вихід схеми. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 45 50 Генератор компенсувального сигналу, що містить лічильник, блок пам'яті та цифро-аналоговий перетворювач, причому вхід лічильника є входом схеми, на який подаються синхроімпульси, вихід блока пам'яті з'єднано з входом цифро-аналогового перетворювача, вихід цифроаналогового перетворювача є виходом схеми, який відрізняється тим, що введено дешифратор, причому вихід лічильника є входом дешифратора, а вихід дешифратора є входом блока пам'яті. Комп’ютерна верстка Г. Паяльніков Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 1

ДивитисяДодаткова інформація

Назва патенту англійськоюCompensation signal generator

Автори англійськоюAzarov Oleksii Dmytrovych, Dudnyk Oleksandr Viktorovych

Назва патенту російськоюГенератор компенсирующего сигнала

Автори російськоюАзаров Алексей Дмитриевич, Дудник Александр Викторович

МПК / Мітки

МПК: H03K 3/011

Мітки: генератор, компенсувального, сигналу

Код посилання

<a href="https://ua.patents.su/3-70191-generator-kompensuvalnogo-signalu.html" target="_blank" rel="follow" title="База патентів України">Генератор компенсувального сигналу</a>

Попередній патент: Спосіб оцінки біологічної відповіді організму онкологічних хворих на імунотерапію

Наступний патент: Мікроелектронний вимірювач магнітної індукції

Випадковий патент: Водогрійний твердопаливний котел