Мультиядерний сигнальний спецпроцесор паралельного опрацювання даних

Номер патенту: 113538

Опубліковано: 10.02.2017

Автори: Николайчук Ярослав Миколайович, Гуменний Петро Володимироич

Формула / Реферат

Мультиядерний сигнальний спецпроцесор, який містить пристрій управління і синхронізації, перші виходи якого підключені до відповідних входів першого ядра ВІТ спецпроцесора, який відрізняється тим, що додатково перші виходи пристрою управління і синхронізації підключені до відповідних перших входів М-1 ВІТ спецпроцесорів, а другий вихід підключений до другого входу БАЦК, другі входи якого є входами пристрою, а виходи підключені до відповідних входів ВІТ процесорів, виходи яких підключені до відповідних входів комутаційної мережі, перші виходи якої підключені до відповідних входів пристрою управління і синхронізації, а виходи з виходами пристрою.

Текст

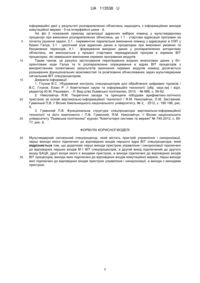

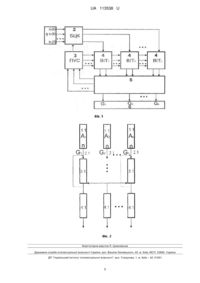

Реферат: Мультиядерний сигнальний спецпроцесор містить пристрій управління і синхронізації, перші виходи якого підключені до відповідних входів першого ядра ВІТ спецпроцесора. Додатково перші виходи пристрою управління і синхронізації підключені до відповідних перших входів М-1 ВІТ спецпроцесорів. Другий вихід підключений до другого входу БАЦК, другі входи якого є входами пристрою. Виходи підключені до відповідних входів ВІТ процесорів, виходи яких підключені до відповідних входів комутаційної мережі, перші виходи якої підключені до відповідних входів пристрою управління і синхронізації, а виходи з виходами пристрою. UA 113538 U (54) МУЛЬТИЯДЕРНИЙ СИГНАЛЬНИЙ СПЕЦПРОЦЕСОР ПАРАЛЕЛЬНОГО ОПРАЦЮВАННЯ ДАНИХ UA 113538 U UA 113538 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислюваної техніки і до сигнальних спецпроцесорів, які працюють в кодовій системі теоретико-числового базису (ТЧБ) Галуа і забезпечують виконання арифметико-логічних обчислень на основі біт орієнтованої вертикально-інформаційної технології (ВІТ). Технічний результат досягається зменшенням числа з'єднань між операційними пристроями процесора за рахунок заміни багатоканальних шин адресу даних та управління призначених для передавання багаторозрядних двійкових кодів у ТЧБ Радемахера, біторієнтованими однорозрядними відповідними шинами, а також виконання арифметико-логічних операцій над числами представленими в кодах Галуа. Відомий аналог, пристрій для перетворення потоків імпульсів унітарного коду в біторієнтований потік коду поля Галуа як спецпроцесора [1]. Недоліком даного пристрою є обмежені функціональні можливості, обумовлені тим, що пристрій, який реалізує вертикально-інформаційну технологію перетворює числа з унітарного базису у ТЧБ Галуа, а також виконує тільки операцію сумування числа імпульсів з можливістю представлення суми імпульсів паралельними кодонами Галуа. Відомий аналог [2], який містить шини операндів чисел представлених у кодах поля Галуа дешифратори та суматори у кожному з розрядів призначений для виконання операції додавання чисел в теоретико-числовому базисі Галуа, який характеризується високим ступенем паралелелізму та відсутність наскрізних переносів. Недоліком відомого пристрою є обмежені функціональні можливості обумовлені тим, що пристрій може виконувати тільки операцію сумування чисел у базисі Галуа. Найбільш близьким аналогом є відомий пристрій як спецпроцесор вертикальноінформаційної технології [3], який містить арифметико-логічний пристрій, оперативно запам'ятовуючий пристрій, регістри загального призначення, пристрій управління і синхронізації, буфер зовнішнього інтерфейсу, лічильник команд у базисі Галуа, зовнішні біт орієнтовані інтерфейсні шини даних, які з'єднані між собою відповідним чином, які з'єднанні з блоком зовнішнього інтерфейсу. Недоліком такого пристрою є обмежені функціональні можливості обумовлені тим, що даний пристрій не дозволяє опрацьовувати і вирішувати обчислювані задачі з колективними даними. Даний пристрій неможливо використати як сигнальний процесор паралельного опрацювання даних. В основу корисної моделі поставлена задача вдосконалення спецпроцесора ВІТ шляхом розширення його функціональних можливостей. Поставлена задача вирішується тим, що мультиядерний сигнальний спецпроцесор, який містить пристрій управління і синхронізації, перші виходи якого підключені до відповідних входів першого ядра ВІТ спецпроцесора, згідно з корисною моделлю, що додатково перші виходи пристрою управління і синхронізації підключені до відповідних перших входів М-1 ВІТ спецпроцесорів, а другий вихід підключений до другого входу БАЦК, другі входи якого є входами пристрою, а виходи підключені до відповідних входів ВІТ процесорів, виходи яких підключені до відповідних входів комутаційної мережі, перші виходи якої підключені до відповідних входів пристрою управління і синхронізації, а виходи є виходами пристрою. Корисна модель пояснюється кресленнями, де на фіг. 1 показана структура багатоядерного сигнального спецпроцесора. на основі ВІТ у базисі Галуа: 1 - вхідна шина аналогових сигналів, 2 - багатоканальний аналого-цифровий кодер (БАЦК) Галуа, 3 - пристрій управління і синхронізації (ПУС), 4 - спецпроцесори ВІТ, 5 - комутаційна мережа, 6 - вихідна інформаційна шина. Мультиядерний сигнальний спецпроцесор працює наступним чином: вхідні аналогові сигнали через шину - 1 надходять на відповідні входи багатоканального аналого-цифрового кодера (БАЦК) - 2, другий вхід якого підключений до першого виходу пристрою управління і синхронізації - 3, а виходи підключені до шин даних відповідних перших входів процесорів - 4, другі входи яких підключені до відповідних виходів пристрою управління і синхронізації - 3, а виходи підключені до відповідних входів комутаційної мережі - 5, перші виходи якої підключені до відповідних входів пристрою управління і синхронізації - 3, а другі виходи є інформаційними виходами мультиядерного сигнального спецпроцесора. Вхідні аналогові сигнали xj(t) поступають па входи БАЦК-2, де синхронно перетворюється скануючими АЦП у біт орієнтовані коди поля Галуа, які надходять на біт орієнтовані шипи даних відповідних ВІТ процесорів, які реалізовують обчислювані операції в розпаралеленому режимі у кодах Галуа. ПУС - 2 генерує адресні коди у базисі Галуа та формує керуючі сигнали на входи біторієнтованих шин адреси та управління. Результати обчислень, які отримуються асинхронно кожним ядром спецпроцесора - 4 надходять на відповідні входи комутаційної мережі, оснащеної кільцевими регістрами зсуву, адресні виходи яких під'єднані до відповідних входів ПУС - 3, а 1 UA 113538 U 5 10 15 20 25 інформаційні дані у результаті розпаралелених обчислень надходять з інформаційних виходів комутаційної мережі - 5 на інтерфейсні шини - 6. На фіг. 2 показаний приклад організації адресних вибірок команд у мультиядерному процесорі при виконанні розпаралелених обчислень, де 1.1 - стартова адресація програми на початку рішення задачі, 2.1 - інкрементне паралельне виконання команд з адресацією в ОЗП у базисі Галуа, 3.1 - циклічний зсув адресних даних в процесорах при виконанні умовних та безумовних переходів, 4.1 - формування вихідних даних у розпаралелених алгоритмах обчислень, які виконуються у процесі стартових переадресацій програм в окремих ВІТ процесорах, які завершили виконаним окремих програмних модулів. Таким чином, за рахунок застосування перетворення вхідних аналогових даних у біторієнтовані коди Галуа та їх розпаралелене опрацювання в ядрах ВІТ процесорів з використанням колективних результатів виконання окремих модулів команд досягається розширення функціональних можливостей та розв'язання обчислюваних задач мультиядерним сигнальним ВІТ спецпроцесором. Джерела інформації: 1. Глухов B.C. Убудований контроль спецпроцесорів для оброблення цифрових підписів / B.C. Глухое, Еліас P. // Комп'ютерні науки та інформаційні технології: [збр. наук.пр] / відп. редактор Ю.М. Рашкевич, - Л: Вид-цтво Львівської політехніки, 2010. - № 686, с. 56-62. 2. Николайчук Я.М. Теоретичні засади та принципи побудови арифметико-логічного пристрою за основі вертикально-інформаційної технології / Я.М. Николайчук, О.М. Заставний, Гуменный П.В. // Вісник Хмельницького національного університету, № 2, - 2012, с. 190-196, рис. 9. 3. Гуменний П.В. Функціональна структура спецпроцесора вертикально-інформаційної технології та його компоненти / П.В. Гуменний, Я.М. Николайчук, // Вісник національного університету "Львівська політехніка" журнал "Комп'ютерні системи та мережі" № 745-2012, с. 6977, рис. 6. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 30 35 Мультиядерний сигнальний спецпроцесор, який містить пристрій управління і синхронізації, перші виходи якого підключені до відповідних входів першого ядра ВІТ спецпроцесора, який відрізняється тим, що додатково перші виходи пристрою управління і синхронізації підключені до відповідних перших входів М-1 ВІТ спецпроцесорів, а другий вихід підключений до другого входу БАЦК, другі входи якого є входами пристрою, а виходи підключені до відповідних входів ВІТ процесорів, виходи яких підключені до відповідних входів комутаційної мережі, перші виходи якої підключені до відповідних входів пристрою управління і синхронізації, а виходи з виходами пристрою. 2 UA 113538 U Комп’ютерна верстка Л. Ціхановська Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 13/00, G06F 7/57

Мітки: опрацювання, сигнальний, мультиядерний, спецпроцесор, даних, паралельного

Код посилання

<a href="https://ua.patents.su/5-113538-multiyadernijj-signalnijj-specprocesor-paralelnogo-opracyuvannya-danikh.html" target="_blank" rel="follow" title="База патентів України">Мультиядерний сигнальний спецпроцесор паралельного опрацювання даних</a>

Попередній патент: Пов’язка-бандаж на дистальний відділ кінцівок у свиней

Наступний патент: Спосіб регулювання температури повітря в підземній камері

Випадковий патент: Вимірювач симетрії для діагностичної моделі