Пристрій додавання багаторозрядних двійкових чисел

Номер патенту: 117789

Опубліковано: 10.07.2017

Автори: Трембач Богдан Ростиславович, Сидор Андрій Володимирович, Трембач Ростислав Богданович

Формула / Реферат

Пристрій додавання багаторозрядних двійкових чисел, що містить k-розрядну вхідну шину, k+m-розрядну вихідну шину, k+m-розрядний накопичуючий суматор, виходи якого з'єднані з першими входами k+m-розрядного паралельного регістра, другий вхід якого з'єднаний з першим входом синхронізації запису, а виходи з'єднані з першими входами накопичуючого суматора і з виходами пристрою, який відрізняється тим, що пристрій містить додатково введений другий вхід синхронізації, який з'єднаний з додатково введеними третіми входами скиду у "0" k+m-розрядного паралельного регістра, додатково введений 2k-розрядний паралельний регістр, перші входи якого з'єднані з додатково введеною 2k-розрядною вхідною шиною, другі входи регістра з'єднані з додатково введеним третім входом синхронізації, прямі та інверсні виходи D-тригерів 2k-розрядного паралельного регістра додатково з'єднані з відповідними першими та другими входами додатково введених першого та другого k-розрядних суматорів, входи переносу нульових розрядів яких додатково з'єднані з додатково введеним входом логічної одиниці, виходи першого k-розрядного суматора додатково з'єднані з відповідними першими входами додатково введеного мультиплексора, виходи другого k-розрядного суматора додатково з'єднані з відповідними другими входами мультиплексора, третій вхід якого додатково з'єднаний з другим виходом переносу старшого розряду першого k-розрядного суматора, а виходи мультиплексора додатково з'єднані з другими молодшими k-розрядами k+m розрядного накопичуючого суматора, другі входи m-старших розрядів якого додатково з'єднані з додатково введеним входом логічного нуля.

Текст

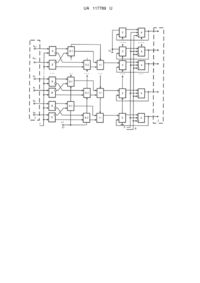

Реферат: Пристрій додавання багаторозрядних двійкових чисел містить k-розрядну вхідну шину, k+mрозрядну вихідну шину, k+m-розрядний накопичуючий суматор. Виходи якого з'єднані з першими входами k+m-розрядного паралельного регістра. Другий вхід якого з'єднаний з першим входом синхронізації запису. Виходи з'єднані з першими входами накопичуючого суматора і з виходами пристрою. Пристрій містить додатково введений другий вхід синхронізації. Вхід синхронізації з'єднаний з додатково введеними третіми входами скиду у "0" k+m-розрядного паралельного регістра. Додатково введений 2k-розрядний паралельний регістр. Перші входи якого з'єднані з додатково введеною 2k-розрядною вхідною шиною, другі входи регістра з'єднані з додатково введеним третім входом синхронізації. Прямі та інверсні виходи D-тригерів 2k-розрядного паралельного регістра додатково з'єднані з відповідними першими та другими входами додатково введених першого та другого k-розрядних суматорів. Входи переносу нульових розрядів яких додатково з'єднані з додатково введеним входом логічної одиниці. Виходи першого k-розрядного суматора додатково з'єднані з відповідними першими входами додатково введеного мультиплексора. Виходи другого k-розрядного суматора додатково з'єднані з відповідними другими входами мультиплексора. Третій вхід якого додатково з'єднаний з другим виходом переносу старшого розряду першого k-розрядного суматора. Виходи мультиплексора додатково з'єднані з другими молодшими k-розрядами k+m розрядного накопичуючого суматора. Другі входи m-старших розрядів якого додатково з'єднані з додатково введеним входом логічного нуля. UA 117789 U (54) ПРИСТРІЙ ДОДАВАННЯ БАГАТОРОЗРЯДНИХ ДВІЙКОВИХ ЧИСЕЛ UA 117789 U UA 117789 U 5 10 15 20 25 30 Корисна модель належить до засобів обчислювальної техніки і призначена для визначення усередненого значення суми модульних різниць вибірки двох потоків двійкових чисел, що відповідає статистичній оцінці Хеммінгової віддалі між двома дискретизованими випадковими процесами і може бути використана як компонент багатоканальних цифрових кореляторів. Відомим аналогом є пристрій додавання багаторозрядних двійкових чисел шляхом визначення залишку по модулю багаторозрядного числа, який містить вхідну і вихідну шини, які є відповідно m-розрядними входами і n-розрядними виходами пристрою, в кожному розряді пристрою міститься однорозрядний суматор та D-тригер, вхід якого з'єднаний з відповідним розрядом вхідної шини, входи синхронізації об'єднані між собою і є другим входом пристрою, вихід суми найстаршого розряду суматора з'єднаний з третім входом мультиплексора [див. Николайчук Я.М., Кімак В.Л., Волинський О.І., Круліковський Б.Б./ Пристрій визначення залишку по модулю багаторозрядного числа// Патент України на корисну модель № 90144, Бюл. № 9, 2014]. Недоліком аналога є обмежені функціональні можливості, обумовлені тим, що він здійснює визначення модульної різниці між двома двійковими числами тільки у випадку, коли перше більше число, представлене прямим двійковим кодом, а друге менше число, яке представлене доповнюючим кодом і не дозволяє накопичувати усереднене значення суми вибірки двох потоків двійкових чисел. Найближчим аналогом до корисної моделі є багаторозрядний пристрій для накопичуючого додавання, який містить n-розрядну вхідну шину, k+m-розрядну вихідну шину, k+m-розрядний накопичуючий суматор, виходи якого з'єднані з першими входами k+m-розрядного паралельного регістра, другий вхід якого з'єднаний з входом синхронізації запису, а виходи з'єднанні з входами накопичуючого суматора і з виходами пристрою (див. Устройство для суммирования. [Електронний ресурс]. Режим доступу:/http//www.findpatent.ru/patent/254/2546569.html.). Недоліком найближчого аналога є обмежені функціональні можливості, обумовлені тим, що даний пристрій не дозволяє накопичувати усереднене значення модульних різниць вибірки двох потоків двійкових чисел. В основу корисної моделі поставлена задача розширення функціональних можливостей пристрою накопичення усередненого значення суми модульних різниць двох потоків двійкових чисел, що відповідає визначенню Хеммінгової віддалі між двома дискретизованими випадковими процесами, згідно з виразом Z 35 40 45 50 55 1 k xi yi , n i1 де i 1, n - об'єм вибірки двійкових чисел x i та y i ; 0 x i 2 k 1; 0 y i 2 k 1; kрозрядність двійкових чисел x i та y i . Поставлена задача вирішується тим, що для накопичення усередненої суми модульних різниць двох потоків двійкових чисел здійснюється одночасне додавання їх прямих та доповнюючих кодів у двох додатково введених суматорах, логікою переносу старшого розряду одного з суматорів та мультиплексором визначаються прямі коди модульних різниць між двома двійковими числами, які додаються n разів у накопичуючому суматорі та шляхом віднімання n числа молодших розрядів формується вихідний m-розрядний двійковий код оцінки Хеммінгової віддалі між двома дискретизованими випадковими процесами (m=log2 n). Пристрій додавання багаторозрядних двійкових чисел, що містить 2k-розрядну вхідну шину 1, k+m-розрядну вихідну шину 2, k+m-розрядний накопичуючий суматор 3, виходи якого з'єднані з першими входами k+m-розрядного паралельного регістра 4, другий вхід якого з'єднаний з першим входом синхронізації запису 5, а виходи з'єднані з першими входами накопичуючого суматора 3 і з виходами пристрою 2, згідно з корисною моделлю, містить додатково введений другий вхід синхронізації 6, який з'єднаний з додатково введеними третіми входами скиду у "0" k+m-розрядного паралельного регістра 7, додатково введений 2k-розрядний паралельний регістр 8, перші входи якого з'єднані з додатково введеною 2k-розрядною вхідною шиною 1, другі входи регістра 8 з'єднані з додатково введеним третім входом синхронізації 7, прямі та інверсні виходи D-тригерів 2k-розрядного паралельного регістра 8 додатково з'єднані з відповідними першими та другими входами додатково введених першого 9.1 та другого 9.2 kрозрядних суматорів, входи переносу нульових розрядів яких додатково з'єднані з додатково введеним входом логічної одиниці 10, виходи першого k-розрядного суматора 9.1 додатково з'єднані з відповідними першими входами додатково введеного мультиплексора 11, виходи другого к-розрядного суматора 9.2 додатково з'єднані з відповідними другими входами мультиплексора 11, третій вхід якого додатково з'єднаний з другим виходом переносу старшого 1 UA 117789 U 5 10 15 20 25 розряду першого 9.1 k-розрядного суматора, а виходи мультиплексора 11 додатково з'єднані з другими молодшими k-розрядами k+m розрядного накопичуючого суматора 3, другі входи mстарших розрядів якого додатково з'єднані з додатково введеним входом логічного нуля 12. Корисна модель пояснюється кресленням, де представлена схема пристрою: 1 - вхідна 2kрозрядна шина ( a o , a1,..., an1 та b o , b1,..., bn1 - відповідні входи x i та y i , багаторозрядних двійкових чисел); 2 - вихідна k+m- розрядна шина; 3-k+m-розрядний накопичуючий суматор; 4k+m-розрядний паралельний регістр; 5 - перший вхід синхронізації запису; 6 - другий вхід синхронізації скиду у нуль; 7 - третій вхід синхронізації запису; 8-D-тригери 2k-розрядного паралельного регістра; 9.1 та 9.2 - однорозрядні повні суматори відповідно першого та другого k-розрядних суматорів; 10 - вхід логічної одиниці; 11 - розрядні компоненти мультиплексора; 12 вхід логічного нуля. Пристрій працює наступним чином. На початку роботи пристрою після подачі сигналу синхронізації у вигляді фронту наростання на вхід синхронізації 6 скиду у нуль k+m-розрядного паралельного регістра 4 на вихідній k+mрозрядній шині 2 формується двійкове число нуль, яке також поступає на перші входи k+mрозрядного накопичуючого суматора 3. Після подачі аналогічного сигналу на вхід синхронізації 7 вхідні двійкові числа x i та y i записуються у D-тригери 2k-розрядного паралельного регістра. Вихідні прямі та інверсні коди тригерів подаються на відповідні перші та другі входи першого 9.1 та другого 9.2 k-розрядних суматорів. У результаті логічними сигналами переносу у старшому розряді суматора 9.1, який поступає на керуючий вхід мультиплексора на його виходах формуються прямі коди модульних різниць між двома двійковими числами x i y i , які подаються на входи k+m- розрядного накопичуючого суматора 3, де додаються до коду, який сформований на виходах k+mрозрядного паралельного регістра 4, а отримана на виходах суматора 3 сума записується і запам'ятовується у регістрі 4. Після n - циклів роботи пристрою, отриманий у регістрі 4 код суми модульних різниць двійкових чисел надходить на вихідну k+m- розрядну шину у вигляді k+m-nрозрядного двійкового коду, починаючи зі старших розрядів паралельного регістра 4. Наявність додаткового входу логічної одиниці на входах переносу нульових розрядів суматорів 9.1 та 9.2 дозволяє одночасно з формуванням зворотних кодів двійкових чисел x i та 30 y i на інверсних виходах D-тригерів 2k-розрядного паралельного регістра 8 формувати їх доповнюючі коди на входах суматорів 9 без додаткових операцій. Якщо на виході переносу старшого розряду суматора 9.1 формується логічна "1", це означає, що число x i y i і на виході першого суматора 9.1 формується код модульної різниці x i y i , який з виходу мультиплексора поступає на другі входи накопичуючого суматора 3. 35 Якщо на такому виході формується логічний "0", це означає що число x i y i , то на виході суматора 9.1 формується результат у вигляді доповнюючого коду, який не надходить на вихід мультиплексора 11. При цьому на вихід мультиплексора 11 надходить прямий код модульної різниці x i y i сформований на виході суматора 9.2. Наприклад: x i 11(10) 1011( 2) ; yi 17(10) 10001(2) . 40 Нехай x i y i , тоді число x i представляється у прямому нормалізованому коді з фіксованою комою, а y i у доповнюючому коді x i 0,01011; [ y i ] доп 101111 . , Додаємо x i [ y i ] доп 0,01011 101111 111010 . , , 45 Тобто результат від'ємний у доповнюючому коді, оскільки у знаковому розряді одиниця і такий код не надходить на вихід мультиплексора 11. Нехай y i x i тоді число y i представляється у прямому нормалізованому коді з фіксованою комою, а x i у доповнюючому коді y i 0,10001; [ x i ] доп 110101 . , Додаємо y i [ x i ] доп 0,10001 110101 0,00110 . , 50 Тобто результат додатний у прямому коді, оскільки у знаковому розряді нуль і цей код відповідає модульній різниці x i y i і надходить на вихід мультиплексора 11. 2 UA 117789 U Таким чином, корисна модель характеризується розширеними функціональними можливостями, оскільки забезпечується визначення усередненого значення суми модульних різниць вибірки двох потоків двійкових чисел незалежно від того, яке з чисел більше або менше. 5 10 15 20 25 ФОРМУЛА КОРИСНОЇ МОДЕЛІ Пристрій додавання багаторозрядних двійкових чисел, що містить k-розрядну вхідну шину, k+mрозрядну вихідну шину, k+m-розрядний накопичуючий суматор, виходи якого з'єднані з першими входами k+m-розрядного паралельного регістра, другий вхід якого з'єднаний з першим входом синхронізації запису, а виходи з'єднані з першими входами накопичуючого суматора і з виходами пристрою, який відрізняється тим, що пристрій містить додатково введений другий вхід синхронізації, який з'єднаний з додатково введеними третіми входами скиду у "0" k+mрозрядного паралельного регістра, додатково введений 2k-розрядний паралельний регістр, перші входи якого з'єднані з додатково введеною 2k-розрядною вхідною шиною, другі входи регістра з'єднані з додатково введеним третім входом синхронізації, прямі та інверсні виходи Dтригерів 2k-розрядного паралельного регістра додатково з'єднані з відповідними першими та другими входами додатково введених першого та другого k-розрядних суматорів, входи переносу нульових розрядів яких додатково з'єднані з додатково введеним входом логічної одиниці, виходи першого k-розрядного суматора додатково з'єднані з відповідними першими входами додатково введеного мультиплексора, виходи другого k-розрядного суматора додатково з'єднані з відповідними другими входами мультиплексора, третій вхід якого додатково з'єднаний з другим виходом переносу старшого розряду першого k-розрядного суматора, а виходи мультиплексора додатково з'єднані з другими молодшими k-розрядами k+m розрядного накопичуючого суматора, другі входи m-старших розрядів якого додатково з'єднані з додатково введеним входом логічного нуля. Комп’ютерна верстка Г. Паяльніков Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

Мітки: двійкових, чисел, пристрій, додавання, багаторозрядних

Код посилання

<a href="https://ua.patents.su/5-117789-pristrijj-dodavannya-bagatorozryadnikh-dvijjkovikh-chisel.html" target="_blank" rel="follow" title="База патентів України">Пристрій додавання багаторозрядних двійкових чисел</a>

Попередній патент: З’єднання торсіонного вала

Наступний патент: Зірочка

Випадковий патент: Комплекс спектральної корекції "барс"