Аналого-цифровий перетворювач

Номер патенту: 119397

Опубліковано: 25.09.2017

Автори: Бортник Геннадій Григорович, Бортник Олександр Геннадійович, Васильківський Микола Володимирович

Формула / Реферат

Аналого-цифровий перетворювач, який у випадку n розрядів містить резистивну матрицю, що складається з 2n-1 резисторів, n-розрядну вихідну шину, шину джерела опорної напруги, 2n-1 лінійки компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а неінвертувальні входи з'єднано з шиною джерела вхідного сигналу, який підлягає перетворенню, перетворювач коду, виходи якого є відповідно вихідною розрядною шиною пристрою, який відрізняється тим, що введено резистор та перший і другий компаратори, причому один вивід резистора під'єднано до шини джерела опорної напруги, а другий вивід резистора під'єднано до входу резистивної матриці, неінвертувальні входи першого та другого компараторів з'єднано з шиною джерела вхідного сигналу, а інвертувальний вхід першого компаратора під'єднано до шини джерела опорної напруги, а інвертувальний вхід другого компаратора під'єднано до спільної шини пристрою, у кожен з і-х розрядних каналів компараторів під'єднано перший, другий і третій логічні елементи І та логічний елемент АБО, причому перший вхід третього логічного елемента І під'єднано до виходу і-го компаратора та до другого входу другого логічного елемента І, а другий вхід під'єднано до виходу і-1-го компаратора та до другого входу першого логічного елемента І, перший вхід другого логічного елемента І під'єднано до виходу і+1-го компаратора та до першого входу першого логічного елемента І, перший, другий та третій входи логічного елемента АБО під'єднано відповідно до виходів першого, другого та третього логічних елементів І, а вихід логічного елемента АБО під'єднано до відповідного і-го входу перетворювача коду.

Текст

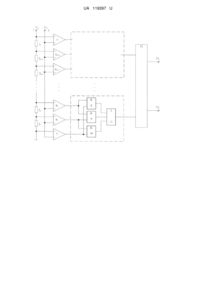

Реферат: Аналого-цифровий перетворювач у випадку n розрядів містить резистивну матрицю, що n n складається з 2 -1 резисторів, n-розрядну вихідну шину, шину джерела опорної напруги, 2 -1 лінійки компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а неінвертувальні входи з'єднано з шиною джерела вхідного сигналу, який підлягає перетворенню, перетворювач коду, виходи якого є відповідно вихідною розрядною шиною пристрою. Введено резистор та перший і другий компаратори, причому один вивід резистора під'єднано до шини джерела опорної напруги, а другий вивід резистора під'єднано до входу резистивної матриці, неінвертувальні входи першого та другого компараторів з'єднано з шиною джерела вхідного сигналу, а інвертувальний вхід першого компаратора під'єднано до шини джерела опорної напруги, а інвертувальний вхід другого компаратора під'єднано до спільної шини пристрою, у кожен з і-х розрядних каналів компараторів під'єднано перший, другий і третій логічні елементи І та логічний елемент АБО, причому перший вхід третього логічного елемента І під'єднано до виходу і-го компаратора та до другого входу другого логічного елемента І, а другий вхід під'єднано до виходу і-1-го компаратора та до другого входу першого логічного елемента І, перший вхід другого логічного елемента І під'єднано до виходу і+1-го компаратора та до першого входу першого логічного елемента І, перший, другий та третій входи логічного елемента АБО під'єднано відповідно до виходів першого, другого та третього логічних елементів І, а вихід логічного елемента АБО під'єднано до відповідного і-го входу перетворювача коду. UA 119397 U (54) АНАЛОГО-ЦИФРОВИЙ ПЕРЕТВОРЮВАЧ UA 119397 U UA 119397 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до імпульсної техніки і призначена для використання в системах обробки швидкоплинної інформації. Відомий аналого-цифровий перетворювач (АЦП) паралельної дії, який містить групу компараторів старших розрядів і групу компараторів молодших розрядів, перші входи яких підключені до джерел опорних напруг, сигнальні входи групи компараторів старших розрядів підключені до джерела сигналу, який перетворюється, а виходи компараторів в кожній групі, крім компараторів старших розрядів, об'єднані попарно і підключені до керуючих входів елементів пам'яті, і резистивні підсилювачі, перші входи яких підключені до джерел струмів зміщення, другі через повторювач та інвертор підключені до джерела сигналу, який перетворюється, а виходи попарно із зсувом на один підключені до входів елемента, виходи яких через елемент АБО з'єднані з сигнальними входами компараторів молодших розрядів, входи стробування елементів пам'яті підключені до джерела стробуючого сигналу (А.С. СРСР № 879771, м.кл. Н03К 5/22, бюл. № 41, 1981 р.). Недоліком даного перетворювача є низьке значення відношення сигнал/шум, що зменшує точність перетворення. Відомий аналого-цифровий перетворювач, який у випадку n розрядів містить резистивну матрицю, вхід якої під'єднано до шини джерела опорної напруги, Т-1 лінійки компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а неінвертувальні входи з'єднано з шиною джерела напруги, яка підлягає перетворенню, виходи лінійки компараторів під'єднано до відповідних входів кодувальної логіки, виходи якої є вихідною розрядною шиною аналого-цифрового перетворювача (Гельман М.М. Системные аналого-цифровые преобразователи и процессоры сигналов. - М.: Мир, 1996. - С. 142, рис. 2.4). Недоліком даного перетворювача є низьке значення відношення сигнал/шум. Найбільш близьким аналогом є аналого-цифровий перетворювач, який у випадку n розрядів містить резистивну матрицю, що складається з Т-1 резисторів, вхід якої під'єднано до шини джерела опорної напруги, Т-1 лінійки компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а неінвертувальні входи з'єднано з шиною джерела напруги, яка підлягає перетворенню, виходи розрядних каналів Т-1 лінійки компараторів під'єднано до відповідних входів перетворювача унітарного коду у позиційний двійковий код, в подальшому перетворювач коду, виходи якого є відповідно вихідною розрядною шиною пристрою (Патент США № 4393372, м.кл. - Н03К 13/02). Недоліком даного пристрою є низьке значення відношення сигнал/шум, пов'язане з виникненням короткочасних збоїв вихідного коду АЦП при переході деяких компараторів із стану логічного 0 в 1 і навпаки. Це призводить до виникнення неоднозначності зчитування вихідних відліків та відповідно до погіршення шумових властивостей пристрою і зниження його відношення сигнал/шум. В основу корисної моделі поставлено задачу створення такого аналого-цифрового перетворювача, в якому за рахунок введення нових блоків та зв'язків підвищується значення відношення сигнал/шум, що дає можливість підвищити точність перетворення. Поставлена задача вирішується тим, що в аналого-цифровий перетворювач (АЦП), який у n випадку n розрядів містить резистивну матрицю, що складається з 2 -1 резисторів, n-розрядну n вихідну шину, шину джерела опорної напруги, 2 -1 лінійки компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а неінвертувальні входи з'єднано з шиною джерела вхідного сигналу, який підлягає перетворенню, перетворювач коду, виходи якого є відповідно вихідною розрядною шиною пристрою, згідно з корисною моделлю, введено резистор та перший і другий компаратори, причому один вивід резистора під'єднано до шини джерела опорної напруги, а другий вивід резистора під'єднано до входу резистивної матриці, неінвертувальні входи першого та другого компараторів з'єднано з шиною джерела вхідного сигналу, а інвертувальний вхід першого компаратора під'єднано до шини джерела опорної напруги, а інвертувальний вхід другого компаратора під'єднано до спільної шини пристрою, у кожен з і-х розрядних каналів компараторів під'єднано перший, другий і третій логічні елементи І та логічний елемент АБО, причому перший вхід третього логічного елемента І під'єднано до виходу i-го компаратора та до другого входу другого логічного елемента І, а другий вхід під'єднано до виходу і-1-го компаратора та до другого входу першого логічного елемента І, перший вхід другого логічного елемента І під'єднано до виходу і+1-го компаратора та до першого входу першого логічного елемента І, перший, другий та третій входи логічного елемента АБО під'єднано відповідно до виходів першого, другого та третього логічних елементів І, а вихід логічного елемента АБО під'єднано до відповідного і-го входу перетворювача коду, що дає можливість знизити неоднозначність зчитування вихідних кодів 1 UA 119397 U 5 10 15 20 25 АЦП внаслідок збоїв у роботі деяких компараторів, а отже і підвищити його значення відношення сигнал/шум, що дає можливість підвищити точність перетворення. На кресленні наведена структурна електрична схема аналого-цифрового перетворювача. Пристрій містить шину 1 джерела опорної напруги Uon, яку під'єднано до інвертувального входу першого 5 компаратора та першого вивода першого 3 резистора, другий вивід якого під'єднано до інвертувального входу лінійки з m-1 компараторів 6 та входу резистивної матриці n 2, що складається з m-1 послідовно ввімкнених резисторів, де m=2 , виходи якої під'єднано до інвертувальних входів лінійки з m-1 компараторів 6. Шину 4 джерела вхідного сигналу Uвx, що підлягає перетворенню під'єднано до неінвертувальних входів лінійки з m-1 компараторів 6, а інвертувальний вхід другого 7 компаратора під'єднано до спільної шини пристрою. У кожен з і-х розрядних каналів компараторів під'єднано перший 8, другий 9 і третій 10 логічні елементи І та логічний елемент АБО 11, причому перший вхід третього 10 логічного елемента І під'єднано до виходу і-го компаратора 6 та до другого входу другого 9 логічного елемента І, а другий вхід під'єднано до виходу i-1-го компаратора 6 та до другого входу першого 8 логічного елемента І, перший вхід другого 9 логічного елемента І під'єднано до виходу i+1-го компаратора 6 та до першого входу першого 8 логічного елемента І, перший, другий та третій входи логічного елемента АБО 11 під'єднано відповідно до виходів першого 8, другого 9 та третього 10 логічних елементів І, а вихід логічного елемента АБО 11 під'єднано до відповідного і-гo входу перетворювача коду 12, виходи якого під'єднано до n-розрядної вихідної шини 13. Аналого-цифровий перетворювач працює наступним чином. Вхідний сигнал, який перетворюється, Uвx через шину 4 джерела вхідного сигналу надходить на неінвертувальні входи компараторів 5, 6, 7, де відбувається його порівняння з опорними рівнями, сформованими з напруги шини 1 джерела опорної напруги Uon за допомогою резистивної матриці 2 та резистора 3. За допомогою перетворювача коду 12 відбувається перетворення m-1-розрядного унітарного коду з i-х розрядних каналів компараторів 6 у nрозрядний позиційний двійковий код. На виході і-го розрядного каналу компаратора 6 формується цифровий сигнал, згідно з таблицею істинності: Таблиця 30 35 40 45 Кі-1 Кі Кі+1 Yі 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 де Кі - значення виходу і-го компаратора; Yі - значення виходу і-го розрядного каналу компаратора. Таким чином, рівень логічної 1 на виході і-го розрядного каналу компаратора 6 формується лише за обов'язкової умови її наявності на виходах не менше, ніж двох компараторів з трьох сусідніх компараторів, що формують і-й розряд унітарного коду. Тому невизначеність стану одного компаратора у ряді кодових комбінацій ліквідується і тим самим знижується вплив випадкових помилок на значення вихідного коду АЦП, що призводить до підвищення відношення сигнал/шум перетворювача. Виконання аналого-цифрового перетворювача, згідно зі схемою корисної моделі, з використанням резистора 3, першого 5 і другого компаратора 7, а також трьох логічних елементів І 8, 9, 10 та логічного елемента АБО 11 у кожному розрядному каналі компаратора 6, дозволяє знизити рівень невизначеності вихідних відліків АЦП, що призводить до зменшення вихідного шуму. Таким чином, пониження рівня шумів невизначеності підвищує значення відношення сигнал/шум АЦП. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Аналого-цифровий перетворювач, який у випадку n розрядів містить резистивну матрицю, що n n складається з 2 -1 резисторів, n-розрядну вихідну шину, шину джерела опорної напруги, 2 -1 лінійки компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної 2 UA 119397 U 5 10 15 матриці, а неінвертувальні входи з'єднано з шиною джерела вхідного сигналу, який підлягає перетворенню, перетворювач коду, виходи якого є відповідно вихідною розрядною шиною пристрою, який відрізняється тим, що введено резистор та перший і другий компаратори, причому один вивід резистора під'єднано до шини джерела опорної напруги, а другий вивід резистора під'єднано до входу резистивної матриці, неінвертувальні входи першого та другого компараторів з'єднано з шиною джерела вхідного сигналу, а інвертувальний вхід першого компаратора під'єднано до шини джерела опорної напруги, а інвертувальний вхід другого компаратора під'єднано до спільної шини пристрою, у кожен з і-х розрядних каналів компараторів під'єднано перший, другий і третій логічні елементи І та логічний елемент АБО, причому перший вхід третього логічного елемента І під'єднано до виходу і-го компаратора та до другого входу другого логічного елемента І, а другий вхід під'єднано до виходу і-1-го компаратора та до другого входу першого логічного елемента І, перший вхід другого логічного елемента І під'єднано до виходу і+1-го компаратора та до першого входу першого логічного елемента І, перший, другий та третій входи логічного елемента АБО під'єднано відповідно до виходів першого, другого та третього логічних елементів І, а вихід логічного елемента АБО під'єднано до відповідного і-го входу перетворювача коду. Комп’ютерна верстка О. Гергіль Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 1/00

Мітки: аналого-цифровий, перетворювач

Код посилання

<a href="https://ua.patents.su/5-119397-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий перетворювач</a>

Попередній патент: Портативний генератор лінійної дії

Наступний патент: Пристрій для вимірювання вологості

Випадковий патент: Твердотільний датчик складу газу