Генератор псевдовипадкових двійкових наборів з рівною вагою

Формула / Реферат

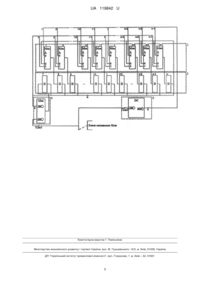

Генератор псевдовипадкових двійкових наборів з рівною вагою, що містить багатоканальний вузол генерації випадкових бітів, кожен канал в якому включає в себе послідовно з'єднані генератор шуму, підсилювач-обмежувач і лічильний тригер, виходи усіх вузлів об'єднані схемою "ВИКЛЮЧНЕ АБО", і канал спряження з ПЕОМ, що включає в себе регістр зсуву, виходи якого увімкнуті до входів вихідного регістра, з'єднаного виходами з шиною даних ПЕОМ, тактовий генератор, вихід якого з'єднаний з синхровходом регістра зсуву та входом лічильника імпульсів, вихід якого під'єднаний до синхровходу вихідного регістра та входу тригера "прапора", а його вихід з'єднаний з виходом запиту переривання та через буферний елемент І з шиною даних ПЕОМ, і дешифратор адреси, включений входами до шини адрес ПЕОМ, а першим виходом до входу дозволу вихідного регістра та входу скидання тригера "прапора", а другим виходом до буферного елемента І, який відрізняється тим, що присутні n-1 одноадресних мультиплексорів 1, n D-тригерів 2, дешифратор 3, [Lbn]-адресний мультиплексор 4, причому на адресні входи n-1 одноадресних мультиплексорів 1 підключено 1 …(n-1) розряди виходу дешифратора 3 відповідно, а на інформаційні входи подається значення 1…(n-1)-го D-тригера відповідно та n-ний D-тригер, на вхід 2…n D-тригерів 2 підключені виходи n-1 одноадресних мультиплексорів 1, а на вхід 1-го D-тригера 2 підключений вихід [Lbn]-адресного мультиплексора 4, на n інформаційних входів [Lbn]-адресного мультиплексора 4 підключено n D-тригерів 2, а на адресні входи подається канал випадкових бітів, також він подається й на вхід дешифратора 3.

Текст

Реферат: UA 119842 U UA 119842 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки, а саме до генераторів вхідних послідовностей для тестування цифрових пристроїв, і може бути використана в машинобудівних технологіях. Відомий лічильник Джонсона на основі замкнутого регістра зсуву з одним перехресним (інверсним) зв'язком, вихід останнього розряду регістра з'єднаний з входом D-тригера, а на 5 інформаційний вхід регістра подано сигнал з інверсного виходу тригера [1]. Недоліки аналога: при розрядності n(n2) лічильника Джонсона на вихід пристрою видається 2n двійкових наборів, тобто генерується обмежена множина різних двійкових наборів. Найбільш близьким по сукупності ознак є генератор рівномірно розподілених ймовірних чисел [2], що містить багатоканальний вузол генерації випадкових бітів, кожен канал в якому включає в себе послідовно з'єднані генератор шуму, підсилювач-обмежувач і лічильний тригер, виходи усіх вузлів об'єднані схемою "ВИКЛЮЧНЕ АБО", і канал спряження з ПЕОМ, що включає в себе регістр зсуву, виходи якого увімкнуті до входів вихідного регістра, з'єднаного виходами з шиною даних ПЕОМ, тактовий генератор, вихід якого з'єднаний з синхровходом регістра зсуву та входом лічильника імпульсів, вихід якого під'єднаний до синхровходу вихідного регістра та входу тригера "прапора", а його вихід з'єднаний з виходом запиту переривання та через буферний елемент І з шиною даних ПЕОМ, і дешифратор адреси, включений входами до шини адрес ПЕОМ, а першим виходом до входу дозволу вихідного регістра та входу скидання тригера "прапора", а другим виходом до буферного елемента І. Недоліки найближчого аналога: генератор видає на вихід числа з різною вагою у двійковому представленні. В основу корисної моделі поставлено задачу створення генератора послідовності nрозрядних двійкових наборів з рівною вагою шляхом введення дешифратора та n мультиплексорів забезпечено генерування послідовності псевдовипадкових двійкових наборів з повним перебором всіх двійкових наборів заданої ваги на виходах пристрою, в результаті чого розширюються функціональні можливості щодо тестування цифрових схем. Поставлена задача вирішується тим, що у генераторі псевдовипадкових двійкових наборів з рівною вагою, що містить багатоканальний вузол генерації випадкових бітів, кожен канал в якому включає в себе послідовно з'єднані генератор шуму, підсилювач-обмежувач і лічильний тригер, виходи усіх вузлів об'єднані схемою "ВИКЛЮЧНЕ АБО", і канал спряження з ПЕОМ, що включає в себе регістр зсуву, виходи якого увімкнуті до входів вихідного регістра, з'єднаного виходами з шиною даних ПЕОМ, тактовий генератор, вихід якого з'єднаний з синхровходом регістра зсуву та входом лічильника імпульсів, вихід якого під'єднаний до синхровходу вихідного регістра та входу тригера "прапора", а його вихід з'єднаний з виходом запиту переривання та через буферний елемент І з шиною даних ПЕОМ, і дешифратор адреси, включений входами до шини адрес ПЕОМ, а першим виходом до входу дозволу вихідного регістра та входу скидання тригера "прапора", а другим виходом до буферного елемента І, згідно з корисною моделлю, присутні n-1 одноадресних мультиплексорів 1, n D-тригерів 2, дешифратор 3, [Lbn]-адресний мультиплексор 4, причому на адресні входи n-1 одноадресних мультиплексорів 1 підключено 1…(n-1) розряди виходу дешифратора 3 відповідно, а на інформаційні входи подається значення 1…(n-1)-го D-тригера відповідно та n-ний D-тригер, на вхід 2…n D-тригерів 2 підключені виходи n-1 одноадресних мультиплексорів 1, а на вхід 1-го D-тригера 2 підключений вихід [Lbn]адресного мультиплексора 4, на n інформаційних входів [Lbn]-адресного мультиплексора 4 підключено n D-тригерів 2, а на адресні входи подається канал випадкових бітів, також він подається й на вхід дешифратора 3. Суть корисної моделі пояснюється кресленням, де зображена функціональна схема генератора. На кресленні присутні n-1 одноадресних мультиплексорів 1, n D-тригерів 2, дешифратор 3, [Lbn]-адресний мультиплексор 4, причому на адресні входи n-1 одноадресних мультиплексорів 1 підключено 1…(n-1) розряди виходу дешифратора 3 відповідно, а на інформаційні входи подається значення 1…(n-1)-го D-тригера відповідно та n-ний D-тригер, на вхід 2…n D-тригерів 2 підключені виходи n-1 одноадресних мультиплексорів 1, а на вхід 1-го D-тригера 2 підключений вихід [Lbn]-адресного мультиплексора 4, на n інформаційних входів [Lbn]адресного мультиплексора 4 підключено n D-тригерів 2, а на адресні входи подається канал випадкових бітів, також він подається й на вхід дешифратора 3. Пристрій працює у такий спосіб. Після встановлення початкових значень n D-тригерів 2 у початковий момент часу на вхід дешифратора 3 та [Lbn]-адресного мультиплексора 4 подається число k через канал випадкових бітів у проміжку 1…n у двійковому вигляді (номер елемента, який умовно ділить n Dтригерів 2 на дві частини, у яких відбуваються циклічний зсув). На вхід 1-го D-тригера 2 1 UA 119842 U 5 10 подається k-ий D-тригер 2 через вихід [Lbn]-адресного мультиплексора 4, на адресні входи n-1 одноадресних мультиплексорів 1 подається сигнал з дешифратора 3, на k-ий D-тригер 2 через (k-і)-ий одноадресний мультиплексор 1 подається n-ний D-тригер, на всі інші входи n D-тригерів 2 (окрім 1-го та k-го) через n-1 одноадресних мультиплексорів 1 подається сигнал з попереднього D-тригера, тобто на і-й подається (і-1)-й. Таким чином, отримуємо дві частини n D-тригерів 2, у яких відбувається циклічний зсув. Джерела інформації: 1. Угрюмов Е.П. Цифровая схемотехника: Учеб. пособие для вузов. - СПб.: БХВ-Петербург, 2004. - 800 с. - С. 218, рис. 3.59; 2. UA №33361 МПК G06F 7/58, G07C 15/00. Генератор рівномірно розподілений ймовірних чисел / Горбенко I.Д., Торба О.О., Єлаков С.Г., Степченко О.3., Риженко О.I. - Опубл. Бюл. №1, 2001. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 15 20 25 30 Генератор псевдовипадкових двійкових наборів з рівною вагою, що містить багатоканальний вузол генерації випадкових бітів, кожен канал в якому включає в себе послідовно з'єднані генератор шуму, підсилювач-обмежувач і лічильний тригер, виходи усіх вузлів об'єднані схемою "ВИКЛЮЧНЕ АБО", і канал спряження з ПЕОМ, що включає в себе регістр зсуву, виходи якого увімкнуті до входів вихідного регістра, з'єднаного виходами з шиною даних ПЕОМ, тактовий генератор, вихід якого з'єднаний з синхровходом регістра зсуву та входом лічильника імпульсів, вихід якого під'єднаний до синхровходу вихідного регістра та входу тригера "прапора", а його вихід з'єднаний з виходом запиту переривання та через буферний елемент І з шиною даних ПЕОМ, і дешифратор адреси, включений входами до шини адрес ПЕОМ, а першим виходом до входу дозволу вихідного регістра та входу скидання тригера "прапора", а другим виходом до буферного елемента І, який відрізняється тим, що присутні n-1 одноадресних мультиплексорів 1, n D-тригерів 2, дешифратор 3, [Lbn]-адресний мультиплексор 4, причому на адресні входи n-1 одноадресних мультиплексорів 1 підключено 1…(n-1) розряди виходу дешифратора 3, відповідно, а на інформаційні входи подається значення 1…(n-1)-го D-тригера відповідно та nний D-тригер, на вхід 2…n D-тригерів 2 підключені виходи n-1 одноадресних мультиплексорів 1, а на вхід 1-го D-тригера 2 підключений вихід [Lbn]-адресного мультиплексора 4, на n інформаційних входів [Lbn]-адресного мультиплексора 4 підключено n D-тригерів 2, а на адресні входи подається канал випадкових бітів, також він подається й на вхід дешифратора 3. 2 UA 119842 U Комп’ютерна верстка Г. Паяльніков Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/58, G06F 11/263

Мітки: двійкових, наборів, рівною, генератор, вагою, псевдовипадкових

Код посилання

<a href="https://ua.patents.su/5-119842-generator-psevdovipadkovikh-dvijjkovikh-naboriv-z-rivnoyu-vagoyu.html" target="_blank" rel="follow" title="База патентів України">Генератор псевдовипадкових двійкових наборів з рівною вагою</a>

Попередній патент: Спосіб передсадивного замочування посадкового матеріалу верби енергетичної для контролю ґрунтових шкідників

Наступний патент: Препарат для лікування еймеріозу та криптоспоридіозу тварин “ампролев-плюс”

Випадковий патент: Комбінована силова установка транспортного засобу