Генератор послідовності n-розрядних двійкових кодів

Номер патенту: 102743

Опубліковано: 12.08.2013

Автори: Мартинюк Олександр Миколайович, Нестеренко Сергій Анатолійович, Дрозд Олександр Валентинович, Борисевич Павло Андрійович, Антонюк Віктор Вікторович

Формула / Реферат

Генератор послідовності n-розрядних двійкових кодів, що містить двійковий лічильник, вхід скидання R та тактовий вхід С якого є відповідно першим R та другим Т входами пристрою, який відрізняється тим, що до нього введені лічильник за модулем n-1, дешифратор, один r-адресний мультиплексор, де r=log2n, та n-1 одноадресних мультиплексорів, при цьому перший інформаційний вихід двійкового лічильника підключено до (n-1)-го iнформаційного входу r-адресного мультиплексора та до перших інформаційних входів одноадресних мультиплексорів, i-й інформаційний вихід, де і=2,…,n, підключено до (n-і)-го інформаційного входу r-адресного мультиплексора та до нульових інформаційних входів одноадресних мультиплексорів, вихід С0 переносу двійкового лічильника підключений до входу Р дозволу рахування лічильника за модулем n-1, вхід V прийому коду та тактовий вхід С якого підключені відповідно до першого R та другого Т входів пристрою, а r-розрядний вихід підключено до r-розрядного адресного входу r-адресного мультиплексора та r-розрядного входу дешифратора, j-й вихід дешифратора, де j=0,…,n-2, підключено до адресного входу k-го одноадресного мультиплексора, де k=n,…,2, виходи мультиплексорів є виходами пристрою, при цьому вихід r-адресного мультиплексора є першим виходом пристрою, вихід l-го одноадресного мультиплексора, де l=2,…, n, є l-м виходом пристрою.

Текст

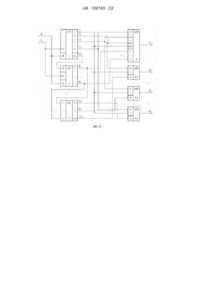

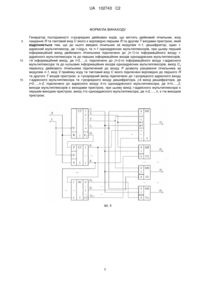

Реферат: Винахід належить до обчислювальної техніки, а саме до генераторів вхідних послідовностей для тестування цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Генератор послідовності n-розрядних двійкових кодів за рахунок введення лічильника за модулем n-1, дешифратора та n мультиплексорів забезпечує генерацію послідовності двійкових наборів з d-перепадами на кожному виході пристрою з повним перебором всіх двійкових наборів на інших виходах пристрою, що розширює функціональні можливості при тестуванні цифрових схем. UA 102743 C2 (12) UA 102743 C2 UA 102743 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до обчислювальної техніки, а саме до генераторів вхідних послідовностей для тестування цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Відомий лічильник Джонсона на основі замкнутого регістра зсуву з одним перехресним (інверсним) зв'язком, вихід останнього розряду регістра з'єднаний з входом D-тригера, а на інформаційний вхід регістру подано сигнал з інверсного виходу тригера [1]. Недоліки аналогу: при розрядності n(n≥2) лічильника Джонсона на вихід пристрою видається 2n двійкових наборів, тобто генерується обмежена множина різних двійкових наборів. Найбільш близьким до запропонованого винаходу по технічній суті та результату, що досягається, є пристрій для генерації послідовності n-розрядних двійкових кодів, який містить двійковий лічильник, вхід скидання та тактовий вхід якого є відповідно першим та другим входами пристрою, а виходи розрядів двійкового лічильника є виходами пристрою [2]. Недоліки прототипу: розряди двійкового лічильника забезпечують формування d-перепадів (переходів з нуля в одиницю) тільки на першому виході пристрою при повному переборі всіх двійкових наборів на решті виходах. Не забезпечено формування d-перепадів на кожному виході пристрою при повному переборі всіх двійкових наборів на решті виходів, що суттєво обмежує функціональні можливості щодо тестування цифрових схем за такими вхідними послідовностями двійкових кодів. Задача винаходу - створення генератора послідовності n-розрядних двійкових кодів, в якому шляхом введення лічильника за модулем n-1, дешифратора та n мультиплексорів забезпечено генерування послідовності двійкових наборів з d-перепадами на кожному виході пристрою з повним перебором всіх двійкових наборів на інших виходах пристрою, в результаті чого розширюються функціональні можливості щодо тестування цифрових схем. Поставлена задача вирішується тим, що у генератор послідовності n-розрядних двійкових кодів (n≥2), що містить двійковий лічильник, вхід скидання R та тактовий вхід С якого є відповідно першим R та другим Т входами пристрою, відповідно до винаходу введені: лічильник за модулем n-1, дешифратор, один r-адресний (r=log2n) мультиплексор та n-1 одноадресних мультиплексорів, при цьому перший інформаційний вихід двійкового лічильника підключено до (n-1)-го інформаційного входу r-адресного мультиплексора та перших інформаційних входів одноадресних мультиплексорів, і-й інформаційний вихід (i=2,…, n) підключено до (n-і)-го інформаційного входу r-адресного мультиплексора та нульових інформаційних входів одноадресних мультиплексорів; вихід Со переносу двійкового лічильника підключений до входу Р дозволу рахування лічильника за модулем n-1, вхід V прийому коду та тактовий вхід С якого підключені відповідно до першого R та другого Т входів пристрою, а r-розрядний вихід підключено до r-розрядного адресного входу r-адресного мультиплексора та r-розрядного входу дешифратора; j-й вихід дешифратора (j=0,…, n-2) підключено до адресного входу k-го (k=n, …, 2) одноадресного мультиплексора, виходи мультиплексорів є виходами пристрою, при цьому вихід r-адресного мультиплексора є першим виходом пристрою, вихід l-го (l=2,…, n) одноадресного мультиплексора є l-й виходом пристрою. Технічний ефект від запропонованого рішення полягає в тому, що шляхом введення лічильника за модулем n-1, дешифратора та n мультиплексорів забезпечується генерація послідовності двійкових наборів з d-перепадами на кожному виході пристрою з повним перебором всіх двійкових наборів на інших виходах пристрою, що призводить до розширення функціональних можливостей при тестуванні цифрових схем. Розширення функціональних можливостей формування d-перепадів можна оцінити наступним чином. В прототипі при повному переборі двійкових наборів формується один dперепад на молодшому виході пристрою (що є виходом молодшого розряду двійкового лічильника) і вдвічібільше на кожному наступному більш старшому виході (розряді). Загальна n-1 кількість d-перепадів визначається як сума 1+2+4 + … + 2 геометричної прогресії, що n-1 дорівнює SП=2 . В запропонованому рішенні d-перепади формуються на кожному з n виходів n-1 пристрою для повного перебору всіх 2 двійкових наборів на його інших n-1 виходах, що n-1 складає загальну кількість d-перепадів S=2 n. Таким чином, запропоноване рішення формує майже в n/2 разів більше d-перепадів порівняно до прототипу, що відповідно може активізувати більше шляхів у цифровій схемі, що тестується. Суть винаходу пояснюється кресленням на фіг. 1, де зображено генератор послідовності nрозрядних двійкових кодів, що містить двійковий лічильник 1, лічильник 2 за модулем n-1, дешифратор 3, r-адресний мультиплексор 4, n-1 одноадресних мультиплексорів 5.2,…, 5.n, перший R скидання та другий T тактовий входи пристрою та виходи пристрою O1,…, Оn, причому вхід R підключено до входу R скидання лічильника 1 і входу V прийому коду лічильника 2, вхід Т пристрою підключено до тактових входів С лічильників 1 і 2, інформаційний вихід 1 лічильника 1 підключено до (n-1)-го інформаційного входу r-адресного мультиплексора 4 та 1 UA 102743 C2 5 10 15 20 25 30 35 40 45 50 інформаційних входів 1 одноадресних мультиплексорів 5.2,…,5.n, і-й інформаційний вихід лічильника 1 (і=2,…,n) підключений до (n-1) -го інформаційного входу мультиплексора 4 та інформаційного входу 0 мультиплексорів 5.2,…,5.n, а вихід переносу СO підключено до входу дозволу рахування Р лічильника 2, виходи 1,…, r якого підключені до адресних входів 1,…, r мультиплексора 4 та входів 1,…, r дешифратора 3, j-й вихід (j=0,…, n-2) дешифратора 3 підключено до адресного входу А k-го (k=n, …, 2) мультиплексора 5.2,…, 5.n, вихід мультиплексора 4 є виходом О1; пристрою, виходи мультиплексорів 5.2,…, 5.n є виходами пристрою О2,…, Оn. Пристрій працює у такий спосіб. У початковий момент часу на вхід скидання R пристрою подається сигнал, що скидає у нуль розряди 1,…, n лічильника 1 та встановлює в початкове значення n-1 розряди 1,…, r лічильника 2. На тактовий вхід Т пристрою надходять тактові імпульси типу "меандр", що далі подаються на тактові входи С лічильника 1 та лічильника 2. Лічильник 1 формує на інформаційних виходах 1,…, n послідовності сигналів T 1,…, Тn. Послідовність T1, що складається з d-перепадів, надходить на (n-1)-й інформаційний вхід мультиплексора 4 та інформаційні входи 1 мультиплексорів 5.2,…, 5.n. Послідовності Т2,…, Тn відповідно надходять на інформаційні входи n-2,…, 0 мультиплексора 4, а також на інформаційні входи 0 мультиплексорів 5.2,…, 5.n. n-1 При досягненні максимального значення 2 лічильника 1 на виході СO лічильника 1 формується сигнал переносу Оf, що надходить на вхід дозволу рахування Р лічильника 2, який дозволяє лічильнику 2 сприйняти тактовий імпульс на вході С та зменшити на одиницю значення двійкового коду K1…, Kr на його виходах 1,…, r. Код K1…, Kr з виходів 1,…, r лічильника 2 подається на входи 1,…, r дешифратора 3 та адресні входи 1,…, r мультиплексора 4. Дешифратор формує унітарний код, розряди якого DO, …, Dn-2 подаються на адресні входи А мультиплексорів 5.n, …, 5.2, відповідно. При початковому значенні n-1 коду K1,…, K2 на виходах 1,…, r лічильника 2 мультиплексор 4 підключає послідовність Т1 з (n-1)-то інформаційного входу на вихід О1 пристрою. Мультиплексори 5.2,…, 5.n підключають послідовності Т2,…,Тn з інформаційних входів 0 відповідно на виходи О2,…,Оn пристрою. Таким чином, пристрій функціонує як його двійковий лічильник 1. При наступних x=n-2,…, 0 значеннях коду K1,…, Kr на виходах 1,…, r лічильника 2 мультиплексор 4 підключає послідовність Тn-x з х-го інформаційного входу на вихід О1 пристрою. Мультиплексор 5.n-х підключає послідовність Т1 з інформаційного входу 1 на вихід Оn-x пристрою. Інші мультиплексори 5.2,…, 5.n (крім 5.n-х) підключають послідовності Т2 … Тn (крім Тn-x) з інформаційних входів 0 відповідно на виходи О2,…, Оn (крім Оn-x) пристрою. При кожному значенні х виходи пристрою O1 та Оn-x міняються послідовностями Т1 та Тn-х. Таким чином, на початковому та наступних значеннях х пристрій забезпечує формування послідовності двійкових наборів з d-перепадами на виході кожного розряду пристрою з повним перебором всіх двійкових наборів на інших розрядах. Розглянемо приклад реалізації генератора n-розрядних двійкових кодів для n=4. В цьому випадку пристрій міститиме двійковий лічильник розрядністю n=4, лічильник за модулем n-1=3 розрядністю r=log2n=2, дешифратор з r=2 входами та n-2=2 виходами, один r=2 адресний та n1=3 одноадресних мультиплексора. На фіг. 2 показані часові діаграми роботи блоків пристрою для n=4, а, саме для входів R і T пристрою, виходівT1…, Т4 лічильника 1, СТ2 лічильника 2, D2,…, D0 дешифратора та виходів О1,…,О4 пристрою. Як бачимо, на кожному виході генератора, починаючи з О1, забезпечено генерування d-перепадів з повним перебором всіх двійкових наборів на інших виходах пристрою. Пристрій може бути використаний для генерації тестової послідовності при вирішенні задач діагностування цифрових схем. Джерела інформації: 1. Угрюмов Е.П. Цифровая схемотехника: Учеб. пособие для вузов. - СПб.:БХВ-Петербург, 2004.-800 с., стр. 218, рис. 3.59; 2. Шило В.Л. Популярные микросхемы КМОП: Справочник. - М.: Ягуар, 1993.-64 с., стр. 27. 55 2 UA 102743 C2 ФОРМУЛА ВИНАХОДУ 5 10 15 Генератор послідовності n-розрядних двійкових кодів, що містить двійковий лічильник, вхід скидання R та тактовий вхід С якого є відповідно першим R та другим Т входами пристрою, який відрізняється тим, що до нього введені лічильник за модулем n-1, дешифратор, один rадресний мультиплексор, де r=log2n, та n-1 одноадресних мультиплексорів, при цьому перший інформаційний вихід двійкового лічильника підключено до (n-1)-го iнформаційного входу rадресного мультиплексора та до перших інформаційних входів одноадресних мультиплексорів, i-й інформаційний вихід, де і=2,…,n, підключено до (n-і)-го інформаційного входу r-адресного мультиплексора та до нульових інформаційних входів одноадресних мультиплексорів, вихід С0 переносу двійкового лічильника підключений до входу Р дозволу рахування лічильника за модулем n-1, вхід V прийому коду та тактовий вхід С якого підключені відповідно до першого R та другого Т входів пристрою, а r-розрядний вихід підключено до r-розрядного адресного входу r-адресного мультиплексора та r-розрядного входу дешифратора, j-й вихід дешифратора, де j=0,…,n-2, підключено до адресного входу k-го одноадресного мультиплексора, де k=n,…,2, виходи мультиплексорів є виходами пристрою, при цьому вихід r-адресного мультиплексора є першим виходом пристрою, вихід l-го одноадресного мультиплексора, де l=2,…, n, є l-м виходом пристрою. 3 UA 102743 C2 Комп’ютерна верстка Л. Литвиненко Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Назва патенту англійськоюN-bit code sequence generator

Автори англійськоюDrozd Oleksandr Valentynovych, Antoniuk Viktor Viktorovych, Borysevych Pavlo Andriiovych, Martyniuk Oleksandr Mykolaiovych, Nesterenko Serhii Anatoliiovych

Назва патенту російськоюГенератор последовательности n-разрядных двоичных кодов

Автори російськоюДрозд Александр Валентинович, Антонюк Виктор Викторович, Борисевич Павел Андреевич, Мартынюк Александр Николаевич, Нестеренко Сергей Анатолиевич

МПК / Мітки

МПК: G06F 11/263

Мітки: генератор, послідовності, двійкових, кодів, n-розрядних

Код посилання

<a href="https://ua.patents.su/6-102743-generator-poslidovnosti-n-rozryadnikh-dvijjkovikh-kodiv.html" target="_blank" rel="follow" title="База патентів України">Генератор послідовності n-розрядних двійкових кодів</a>

Попередній патент: Спосіб одержання композитного матеріалу-перетворювача енергії поля

Наступний патент: Пристрій для контролю справжності банкнот

Випадковий патент: Розмелювальна гарнітура дискового млина