Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів

Формула / Реферат

Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів, що містить блоки регістрів діленого, дільника та суматори, який відрізняється тим, що пристрій додатково устаткований генератором тактових імпульсів, першим елементом І пристрою, розподільником імпульсів, блоком модульних дільників, другим елементом І пристрою, блоком регістрів результату, першим елементом АБО пристрою, блоком допоміжних регистрів, другими елементами АБО пристрою, першим блоком елементів І, який містить перші, другі, ..., (к-2)-гі та (к-1)-ший елементи І, другим блоком елементів І, який містить перші, другі,..., (к-2)-гі та (к-1)-ший елементи І, першими, другими та третіми елементами АБО, другим, третім,..., к-тим блоками вибору констант, першими, другими,..., (к-2)-гими та (к-1)-шим блоками констант, вхідною шину пристрою, причому виходи регістрів блока регістрів діленого, починаючи із першого по (к-1)-й, підключені до перших входів своїх модульних дільників, другі входи яких з'єднані із виходами регістрів блока регістрів дільника, починаючи із першого по (к-1)-й, а їх треті входи та другий вхід другого елемента І пристрою зв’язані із першим виходом розподільника імпульсів, а перший вхід другого елемента І пристрою підключений до виходу к-го регістру блока регістрів діленого, вихід другого елемента І пристрою зв’язаний із другим входом першого елемента АБО пристрою, перший вхід якого з'єднаний із виходом k-го модульного суматору, а вихід першого елемента АБО пристрою підключений до входу k-го регістру блока регістрів результату, вихід якого зв’язаний із першим входом k-гo модульного суматору, виходи модульних дільників, починаючи із першого по (к-1)-ий, підключені до входів своїх регістрів блока регістрів результату та до входів своїх регістрів блока допоміжних регістрів, причому до першого регістру безпосередньо, а до інших - через другі входи других елементів АБО пристрою, перші входи яких з'єднані із виходами своїх модульних суматорів, вихід і-го регістру блока допоміжних регістрів підключений до других входів (і+1)-х елементів І першого блока елементів І, перші входи яких з'єднані із 2і-ми виходами розподільника імпульсів та першими входами (і+1)-х елементів І другого блока елементів І, другі входи яких зв’язані із виходами своїх блоків констант, виходи елементів І першого та другого блоків І підключені - для перших елементів І безпосередньо, а для всіх наступних - через перші та другі елементи АБО до блоків вибору констант, виходи яких підключені до других входів своїх суматорів, а третій вхід і-го суматора зв’язаний із третім, п'ятим,..., (2і+1)-м виходами розподільника імпульсів, причому для другого суматора - безпосередньо, а для всіх наступних - через треті елементи АБО, вхід розподільника імпульсів зв’язаний із виходом першого елемента І пристрою, перший вхід якого підключений до вхідної шини пристрою, а другий - до виходу генератора тактових імпульсів.

Текст

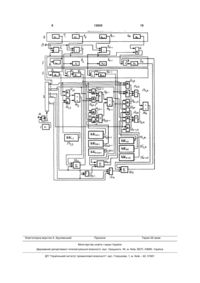

Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів, що містить блоки регістрів діленого, дільника та суматори, який відрізняється тим, що пристрій додатково устаткований генератором тактових імпульсів, першим елементом І пристрою, розподільником імпульсів, блоком модульних дільників, другим елементом І пристрою, блоком регістрів результату, першим елементом АБО пристрою, блоком допоміжних регистрів, другими елементами АБО пристрою, першим блоком елементів І, який містить перші, другі, ..., (к-2)-гі та (к-1)-ший елементи І, другим блоком елементів І, який містить перші, другі,..., (к-2)-гі та (к-1)-ший елементи І, першими, другими та третіми елементами АБО, другим, третім,..., к-тим блоками вибору констант, першими, другими,..., (к-2)-гими та (к-1)-шим блоками констант, вхідною шину пристрою, причому виходи регістрів блока регістрів діленого, починаючи із першого по (к-1)-й, підключені до перших входів своїх модульних дільників, другі входи яких з'єднані із виходами регістрів блока регістрів дільника, починаючи із першого по (к-1)-й, а їх треті входи та другий вхід другого елемента І пристрою зв’язані із першим виходом розподільника імпульсів, а перший вхід другого елемента І пристрою підключений до виходу к-го регістру блока регістрів діленого, вихід другого елемента І пристрою U 2 (11) 1 3 До переваг СЗК відносять максимальний паралелизм при виконанні операцій по обробці інформації. Але виникають значні труднощі при реалізації ділення на число, що кратне одному із модулів системи, бо виникає невизначеність типу 0/0. Відомий пристрій дня перетворювання коду із СЗК у поліадичний код містить в собі вхідний регістр, суматори, елементи І, АБО [2]. Недоліком цього пристрою є значна кількість обладнання. Недоліком пристрою для перетворювання коду із СЗК у поліадичний код [3], що містить в собі регістри, суматори, елементи 1, АБО, шифратори, є його невисока швидкодія, обумовлена тим, що для отримання результату порівняння необхідно витратити значну кількість модульних операцій. Пристрій для реалізації ділення чисел у СЗК [4] визначає цифри частки, крім цифр по тих модулях системи, на які виконується ділення. Для визначення останніх пристрій потребує розширення набору модулів з використанням досить складних операцій та устаткування та надає лише деякі часткові результати. Найбільш близькім по технічній суттєвості до корисної моделі є пристрій для перетворювання коду із СЗК у поліадичний код [5], що містить в собі розради регістру числа, суматори, функціональні перетворювачі та шифратори, причому вихід першого розряду регістра числа пов'язаний із третім входом свого суматора, а виходи розрядів регістру числа, починаючи з другого розряду, з'єднані із першими входами своїх суматорів. Недоліком цього пристрою, який має по відношенню до пристроїв [2] та [3] підвищену швидкодію та меншу кількість обладнання, є те, що цей пристрій не має. можливості ділення числа на дільник, кратний одному із модулів. В основу корисної моделі доставлено задачу: пристрій, функціонуючий у системі залишкових класів, шляхом введення додаткових елементів та встановлення відповідних зв'язків між елементами пристрою забезпечити можливість ділення числа на дільник, кратний одному із модулів. Для цього пристрій додатково устаткований генератором тактових імпульсів, першим елементом І пристрою, розподілювачем імпульсів, блоком модульних дільників, другим елементом І пристрою, блоком регістрів результату, першим елементом АБО пристрою, блоком допоміжних регістрів, другими елементами АБО пристрою, першим блоком елементів І, який включає перші, другі, ...-, (к-2)-гі та (к-1)-ший елементи І, другим блоком елементів І, який включає перші, другі,..., (к-2)-гі та (к-1)-ший елементи І, першими, другими та третіми елементами АБО, другим, третім,..., к-тим блоками вибору констант, першими, другими,..., (к-2)-гими та (к-1)шим блоками констант, вхідною шину пристрою. При цьому виходи регістрів блоку регістрів діленого, починаючи із першого по (к-1)-й, підключені до перших входів своїх модульних дільників, другі входи яких з'єднані із виходами регістрів блоку регістрів дільника, починаючи із першого по (к-1)-й, а їх треті входи та другий вхід другого елементу І пристрою пов'язані із першим виходом розподілювача імпульсів, а перший вхід другого елементу І 12655 4 пристрою підключений до виходу k-го регістру блоку регістрів діленого, вихід другого елементу І пристрою пов'язаний із другим входом першого елементу АБО пристрою, перший вхід якого з'єднаний із виходом k-го модульного суматору, а вихід першого елементу АБО пристрою підключений до входу k-го регістру блоку регістрів результату, вихід якого пов'язаний із першим входом k-го модульного суматору, виходи модульних дільників, починаючи із першого по (к-1)-й, підключені до входів своїх регістрів блоку регістрів результату та до входів своїх регістрів блоку допоміжних регістрів, причому до першого регістру безпосередньо, а до інших - через другі входи других елементів АБО пристрою, перші входи яких з'єднані із виходами своїх модульних суматорів, вихід і-го регістру блоку допоміжних регістрів підключений до других входів (і+1)-х елементів І першого блоку елементів І, перші входи яких з'єднані із 2і-ми виходами розподілювача імпульсів та першими входами (і+1)-х елементів І другого блоку елементів І, другі входи яких пов'язані із виходами своїх блоків констант, виходи елементів І першого та другого блоків І підключені - для перших елементів І безпосередньо, а для всіх наступних - через перші та другі елементи АБО до блоків вибору констант, виходи яких під'єднані до других входів своїх суматорів, а третій вхід і-го суматора пов'язаний із третім, п'ятим,..., (2і+1)-м виходами розподілювача імпульсів, причому для другого суматора - безпосередньо, а для всіх наступних - через треті елементи АБО, вхід розподілювача імпульсів пов'язаний із виходом першого елементу І пристрою, перший вхід якого підключений до вхідної шини пристрою, а другий - до виходу генератора тактових імпульсів. На кресленні зображена функціональна схема пристрою. Пристрій містить генератор тактових імпульсів І, перший елемент І пристрою 2, розподілювач імпульсів 3, блок 4 регістрів 41, 42, 43,..., 4к-1, 4к числа А= ( 1, 2, 3,..., к-1, к) для залишків 1, 2, 3,..., к-1, к відповідно по модулях системи р1, р2, р3,...,рк-1, рк блок модульних дільників 51, 52, 53,...,5к-1, другий елемент І пристрою 6, блок 7 регістрів 71, 72, 73,...,7к-1, 7к результату, перший елемент АБО пристрою 8, блок 9 допоміжних регістрів 91, 92, 93,…, 9к-1, другі елементи АБО пристрою 102, 103,..., 10к-1, перший блок елементів І, який включає перші елементи І 111,2, 111,3,..., 111,к-1, 111,к, другі елементи І 112,3,..., 112,к-1, 112,к,...,(к-2)-гі елементи І 11к-2,к-1,...,11к-2,к та (к-1)-ший елемент І 11к1,к; другий блок елементів І, який включає перші елементи І 121,2,..., 121,3,..., 121,к-1, 121,к, другі елементи І 122,3,..., 122,к-1,..., 122,к,..., (к-2)-гі елементи І 11к-2,к-1,..., 11к-2,к та(к-1)-ший елемент І 11к-1,к, перші елементи АБО 131,3,..., 131,к другі елементи АБО 132,3,..., 132,к, другий 142, третій 143,..., к-тий 14к, блоки вибору констант, перші блоки констант БК 151,2, 151,3,..., 151,к-і, 151,к, другі блоки констант БК 152,3, ..., 152,к-1, 152,к, ..., (к-2)-гі блоки констант БК 15к-2,к-1, 15к-2,к та (к-1)-ший блок констант БК 15к-1,к, блок модульних суматорів 162, 163,...,16к-1, 16к відповідно по модулях системи р2, р3,..., рк-1, рк треті елементи АБО 173,..., 17к вхідну 18 шину пристрою, блок 19 регістрів 191, 192, 193,...,19к-1, 19к, 5 числа В = ( 1, 2, 3,..., 12655 к-1, к) для залишків 1, 2, 3, ..., к-1, к, відповідно по модулях системи р1, р2, р3, ..., pк-1, рk. При цьому порядок розташування модулей p1, р2, ..., рк-1 вільний, але модуль рк, якому кратний дільник, повинен бути останнім. Роботу пристрою розглянемо для модулей р1 = 7, p2 = 5, р3 = 3, р4 = 2. Пристрій працює слідуючим чином. До моменту початку ділення на регистрах 41, 42, 43, ..., 4к-1, 4к записане число А = ( 1, 2, 3, ..., к-1, к). Нехай А = 208, тобто 1 = 5, 2 = 3, 3 = 1, 4 = 0. На регістрах 191, 192, 193, ..., 19к записане число В = ( 1, 2, 3,..., к-1, к ). Нехай В = 4, тобто 1 = 4, 2 = 4, 3 = 1, 4 = 0. Після включення сигналом по шині 18 здійснюється подача через елемент 12 сигнала на вхід розподілювача імпульсів 3. Сигнал з першого виходу розподілювача імпульсів 3 поступає на треті входи модульних дільників 51, 52, 53, ..., 5к-1, дозволяючи виконання формального ділення 1, 2, 3 на 1, 2, 3. Результат з виходів цих дільників у вигляді 1 ( 1 / 1)(mod 7 ) (5 / 4 )(mod 7 ) 3(mod 7), 2 ( 2 / 2 )(mod 5 ) (3 / 4)(mod 5) 2(mod 5), записується відповідно на допоміжні регістри 91, 92, 93 та у вигляді 1 = 3 (mod 7), 2 = 2 (mod 5), 3 = 1 (mod 3) на регістри 71, 72, 73 результату. Сигнал з другого виходу розподілювача імпульсів 3 поступає на перші входи елементів І 111,2 та 111,2, І 111,3 та 111,3, І 111,4 та 111,4, дозволяючи подачу через ці елементи І до входів блоків вибору констант відповідно 142, 143, 144 значення 1 та значення констант із виходів перших блоків констант БК 151,2, 151,3, 151,4. У таблиці 1 наведені константи на виходах відповідно блоку 151,2 - стовпчик 2 таблиці для p2 = 5, блоку 151,3 - стовпчик 3 таблиці для р3 = 3 та блоку 151,4 - стовпчик 4 таблиці для p4 = 2. В залежності від значень 1, що наведені у стовпчику 1 таблиці, блоками 142, 143, 144 здійснюється вибір відповідних констант. Для даного 1 = 3 константа з виходу 151,2 дорівнює 3, константа з виходу 151,3 дорівнює 0, константа з виходу 151,4 дорівнює 1. Сигнал з третього виходу розподілювача імпульсів 3 поступає на треті входи модульних суматорів 162, 163, 164, дозволяючи виконання в кожному суматорі, крім 164, віднімання вибраної константи, що надходить із виходу свого блоку вибору констант на другий вхід суматору, із величини, що надходить із виходу свого регістру на перший вхід суматору. Результат із виходу кожного суматору записується на свій допоміжний регістр. Водночас у суматорі 164 здійснюється додавання вибраної константи, що надходить із виходу свого блоку вибору констант на другий вхід суматору, до величини, що надходить із виходу свого регістру на перший вхід суматору. Результат із виходу цього суматору записується на свій допоміжний регістр. 3 ( 3 / 3 )(mod 3 ) (1/ 1)(mod 3) 1(mod 3), 6 Для наведеного числа А отримуємо такі значення: 2=(2-3) (mod 5), 3 =(1-0) (mod 3), 4= (0+1) (mod 2), тобто 2 = 4, 3 = 1, 4 =1. які записуються відповідно на регістри 92, 93 та 74. Сигнал з четвертого виходу розподілювача імпульсів 3 поступає на перші входи елементів І 112,3 та 112.3, I 112.4 та 112,4, дозволяючи подачу через ці елементи І до входів блоків вибору констант відповідно 143, 144 значення 2 та значення констант із виходів других блоків констант БК 152,3, 152,4. У таблиці 2 наведені константи на виходах відповідно блоку 152,3 - стовпчик 2 таблиці для р3 = 3 та блоку 152,4 - стовпчик 3 таблиці для р4 = 2. В залежності від значень 2, що наведені у стовпчику 1 таблиці, блоками 143, 144 здійснюється вибір відповідних констант. Для даного 2 = 4 константа з виходу 152,3 дорівнює 2, константа з виходу 152,4 дорівнює 0. Сигнал з п'ятого виходу розподілювача імпульсів 3 поступає на треті входи модульних суматорів 163, 164, дозволяючи виконання в кожному суматорі, крім 164, віднімання вибраної константи, що надходить із виходу свого блоку вибору констант на другий вхід суматору, із величини, що надходить із виходу свого регістру на перший вхід суматору. Результат із виходу кожного суматору записується на свій регістр. Водночас у суматорі 164 здійснюється додавання вибраної константи, що надходить із виходу свого блоку вибору констант на другий вхід суматору, до величини, що надходить із виходу свого регістру на перший вхід суматору. Результат із виходу цього суматору записується на свій допоміжний регістр. Для наведеного числа А отримуємо такі значення: 3 = (1-2) (mod 3), 4 =(1+0) (mod 2), тобто 3 = 2, 4 = 1, які записуються відповідно на регістри 93 та 74. Сигнал з шостого виходу розподілювача імпульсів 3 поступає на перші входи елементів І 113,4 та 113,4, дозволяючи подачу через ці елементи 1 до входів блоку вибору констант 144 значення 3 та значення константи із виходу третього блоку констант БК 153,4. У таблиці 3 наведені константи на виходах блоку 153,4 - стовпчик 2 таблиці для p4 = 2. В залежності від значень 3, що наведені у стовпчику 1 таблиці, блоком 144 здійснюється вибір відповідної константи. Для даного 3 = 2 константа з виходу 153,4 дорівнює 1. Сигнал з сьомого виходу розподілювача імпульсів 3 поступає на третій вхід модульного суматору 164, дозволяючи виконання в суматорі додання вибраної константи, що надходить із виходу свого блоку вибору констант на другий вхід суматору, до величини, що надходить із виходу свого регістру на перший вхід суматору. Результат із виходу суматору записується на свій регістр. Для наведеного числа А отримуємо значення: 4=(1+1) (mod 2), тобто 4 =0, який записуються на регістр 74. Отже, число В = (3, 2, 1, 0), тобто 52 є результатом ділення числа А = (5,3.1,0), тобто 208 на В = (4,4.1,0). тобто 4. Джерела інформації: 7 12655 1. Акушский И.Я., Юдицкий Д.И. Машинная арифметика в остаточных классах. М.: Сов. Радио, 1968, 440 с. 2. Авторське свідоцтво СРСР №328448, кл. G06F 5/02, 02.11.1972 3.Торгашев В.А. Применение корректирующих кодов для повышения надежности цифровых вы 8 числительных машин. Диссертация, ЛИАП, 1967. 4. Л.Б. Копыткова, Н.И. Червяков. Реализация деления чисел в системе остаточных классов на модули системы. «Вестник Ставропольского университета», 34/2003. 5. Авторське свідоцтво СРСР №637809, кл. G06F 5/02,15.12.1978 Таблиця 1 МОДУЛІ 7 5 3 2 ЗАЛИШКИ 0 1 2 3 4 5 6 0 1 2 3 4 0 1 КОНСТАНТИ 0 1 2 0 1 2 0 0 1 0 1 0 1 0 Таблиця 2 МОДУЛІ 3 5 ЗАЛИШКИ 0 1 2 3 4 2 КОНСТАНТИ 0 0 1 1 2 0 1 1 0 0 Таблиця 3 МОДУЛІ 3 2 ЗАЛИШКИ 0 1 2 КОНСТАНТИ 0 0 1 9 Комп’ютерна верстка А. Крулевський 12655 Підписне 10 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for dividing a number by a divisor that is a multiple of one of the number residue modules, by using residue arithmetic

Назва патенту російськоюУстройство для деления числа на делитель, кратный одному из модулей при определении остатка числа, с помощью арифметики в остаточных классах

МПК / Мітки

МПК: G06F 7/04, G06F 7/535

Мітки: дільник, класів, системі, чисел, одному, модулів, пристрій, кратний, ділення, залишкових

Код посилання

<a href="https://ua.patents.su/5-12655-pristrijj-dlya-dilennya-chisel-u-sistemi-zalishkovikh-klasiv-na-dilnik-kratnijj-odnomu-iz-moduliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів</a>

Попередній патент: Спосіб визначення у системі залишкових класів належності числа до даної половини

Наступний патент: Спосіб хірургічного лікування кісти паренхіматозного органа

Випадковий патент: Пристрій для виготовлення харчового екструдованого продукту