Функціональний перетворювач

Номер патенту: 14935

Опубліковано: 04.03.1997

Автори: Четвериков Григорій Григорович, Бондаренко Михайло Федорович, Коноплянко Зеновій Дмитрович

Формула / Реферат

Функциональный преобразователь, содержащий аналого-цифровой и цифроаналоговый преобразователи, а также дешифратор, включающий двухвходовый элемент И, отличающийся тем, что в него дополнительно введены коммутатор, состоящий из трех блоков коммутации, каждый из которых выполнен на трех двухвходовых элементах И, а также блок управления, включающий двухвходовый элемент И, причем вход аналого-цифрового преобразователя является информационным входом функционального преобразователя, первый выход аналого-цифрового преобразователя подключен к первому входу элемента И дешифратора, второй и третий выходы - транзитом подключены соответственно к первому и третьему выходам дешифратора, а четвертый выход - к второму входу элемента И, выход которого является вторым выходом дешифратора, первые входы элементов И в первом, втором и третьем блоке коммутации объединены и подключены соответственно к первому-третьему выходам дешифратора, вторые входы первых элементов И блоков коммутации объединены и подключены к первому выходу блока управления,вторые входы вторых элементов И блоков коммутации объединены и подключены к второму выходу блока управления, вторые входы третьих элементов И блоков коммутации объединены и подключены к третьему выходу блока управления, выходы первых элементов И блоков коммутации объединены и подключены к первому входу цифроаналогового преобразователя, выходы вторых элементов и блоков коммутации объединены и подключены к второму входу цифроаналогового преобразователя управления, выходы третьих элементов И блоков коммутации объединены и подключены к третьему входу цифроаналогового преобразователя, выход которого является выходом функционального преобразователя в целом, входы блока управления являются внешними входами управления функционального преобразователя, причем первый вход функционального преобразователя подключен к первому входу элемента И блока управления, второй и третий входы транзитом подключены к первому и третьему выходам блока управления, а второй вход элемента И подключен к четвертому входу блока управления, выход элемента И подключен к второму выходу блока управления.

Текст

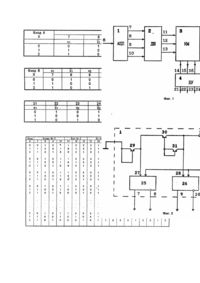

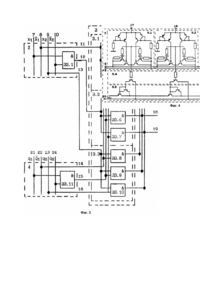

Изобретение, относится к автоматике, вычислительной технике и может использоваться в системах управления, а также при автоматической обработке текстовой языковой информации. Из известных устройств наиболее близким к предлагаемому изобретению является функциональный преобразователь (А.с. №1510077 (СССР), МКИ H03K9/08, опубл. БИ 23.09.89г., №35), содержащий аналого-цифровой и цифроаналоговый преобразователи, дешифратор, содержащий двухвходовый элемент И, а также счетчик, первые выходы которого соединены с одноименными первыми входами дешифратора, причем вход и выход блока аналого-цифрового преобразования являются информационным входом преобразователя и соединены с одноименными вторыми входами дешифратора, выходы деши фратора объединены с одноименными вторыми выходами счетчика и подключены к соответствующим входам блока цифроаналогового преобразования, выход которого является выходом преобразователя, тактовый и установочный входы счетчика являются соответственно тактовым и установочным входами преобразователя. Функциональный преобразователь характеризуется сложностью схемного решения, которое обусловлено неоднородностью схемных решений дешифратора и счетчика и, как следствие, низкой технологичностью в процессе микроэлектронной реализации, а также низким быстродействием из-за последовательного характера работы счетчика в качестве схемы управления процессом настройки функционального преобразователя на выполнение требуемого преобразования. Задачей настоящего изобретения является создание такого функционального преобразователя, в котором однотипное выполнение дешифратора и схемы управления позволяет обеспечить однородность исполнения всех субблоков, что приводит к повышению технологичности устройства в процессе микроэлектронной реализации, а также повышает его быстродействие из-за параллельного однотактного алгоритма работы дешифратора, коммутатора и блока управления. Поставленная задача решается тем, что в функциональный преобразователь, содержащий аналого-цифровой и цифроаналоговый преобразователи, а также дешифратор, включающий двухвходовый элемент И, согласно изобретению, дополнительно введены коммутатор, состоящий из трех блоков коммутации, каждый из которых выполнен на трех двувходовых элементах И, а также блок управления, включающий двухвходовый элемент И, причем вход аналогоцифрового преобразователя является информационным входом функционального преобразователя, первый выход аналогоцифрового преобразователя подключен к первому входу элемента И дешифратора, второй и третий выходы - транзитом подключены соответственно к первому и третьему выходам дешифратора, а четвертый выход - к второму входу элемента И, выход которого является вторым выходом дешифратора, первые входы элементов И в первом, втором и третьем блоке коммутации объединены и подключены соответственно к первому-третьему выходам дешифратора, вторые входы первых элементов И блоков коммутации объединены и подключены к первому вы ходу блока управления, вторые входы вторых элементов И блоков коммутации объединены и подключены к второму выходу блока управления, вторые входы третьих элементов И блоков коммутации объединены и подключены к третьему выходу блока управления, выходы первых элементов И блоков коммутации объединены и подключены к первому входу ци фроаналогового преобразователя, выходы вторых элементов И блоков коммутации объединены и подключены к второму входу цифроаналогового преобразователя, выходы третьих элементов И блоков коммутации объединении подключены к третьему входу ци фроаналогового преобразователя, выход которого является выходом функционального преобразователя, входы блока управления являются внешними входами управления функционального преобразователя, причем первый вход функционального преобразователя подключен к первому входу элемента И блока управления, второй и третий входы транзитом подключены к первому и третьему выходам блока управления, а второй вход элемента И подключен к четвертому входу блока управления, выход элемента И подключен к второму выходу блока управления. Введение в функциональный преобразователь коммутатора, состоящего из тре х блоков коммутации, каждый из которых выполнен на трех двувходовых элементах И, а также блока управления, включающего двухвходовый элемент И, которые образуют в пространстве стр уктур у параллельного типа с пространственным k-значным кодированием, осуществленным за счет возбужденных состояний в виде двоичных состояний пространственных полюсов позволило обеспечить однотипность и однородность внутренней структуры, существенно уменьшить аппаратурные затраты на создание преобразователя, упростить шинную коммутацию, а также повысить быстродействие за счет минимальной задержки во всех звеньях преобразователя. На фиг.1 изображена структурная схема преобразователя; на фиг.2 - функциональная схема аналого-цифрового преобразователя; на фиг.3 функциональные схемы дешифратора, коммутатора и блока управления; фиг.4 - принципиальная электрическая схема цифро-аналогового преобразователя. Функциональный преобразователь (фиг.1), содержит аналого-цифровой преобразователь (АЦП) 1, де шифратор (ДШ) 2, коммутатор (КМ) 3, блок 4 управления (БУ), цифроаналоговый преобразователь (ЦАП) 5, причем вход 6 АЦП 1 является информационным входом устройства, выходы 7 10 АЦП 1 подключены к соответствующим четырем информационным входам дешифратора 2, а его выходы 11 - 13 подключены к соответствующим входам коммутатора 3, входы 14 - 16 коммутатора 3 соединены с соответствующими выходами блока 4 управления, выходы 17 - 19 коммутатора 3 подключены к соответствующим трем входам ЦАП 5, а выход 20 ЦАП 5 является выходом функционального преобразователя в целом, внешние входы 21 24 управления функционального преобразователя образуют входы блока 4 управления. Аналого-цифровой преобразователь 1 (см. фиг.2) содержит вход 6, являющийся одновременно входом устройства и объединенным информационным входом компараторов 25, 26, входы 27, 28 опорных сигналов компараторов 25, 26, подключенные к соответствующим точкам транзисторного делителя напряжения, состоящего из транзисторов 29 - 31 и резистора 32, а также выходы 7 - 10. Дешифратор 2 (см. фиг.3) содержит четыре информационных входа 7 - 10, три выходы 11 - 13 и двухвходовый элемент 33.1 И, первый вход которого подключен к первому входу 7, второй вход элемента И подключен к четвертому входу 10, второй 8 и третий 9 входы транзитом подключены соответственно к выходам 11 и 13, а выход элемента 33.1 И подключен к выходу 12. Коммутатор 3 (см.фиг.2) содержит девять двухвходовых элементов 33.2 - 33.10 И, образующие три блока 3.1 - 3.3 коммутации по три двухвходовых элемента И в каждом, причем первые входы элементов 33,j И (j = 2 ... 10) в каждом блоке 3.k (k = 1 ... 3) коммутации соединены вместе и подключены соответственно к выходам 11 - 13 дешифратора 2, вторые входы второго 33.2, пятого 33.5 и восьмого 33.8 элементов И коммутатора 3 соединены вместе и подключены к выходу 14 блока 4 управления, вторые входи третьего 33.3, шестого 33.6 и девятого 33,9 элементов И коммутатора 3 соединены вместе и подключены к выходу 15 блока 4 управления, вторые входы четвертого 33.4, седьмого 33.7 и десятого 33.10 элементов И коммутатора 3 также соединены вместе и подключены к выходу 16 блока 4 управления, выходы второго 33.2, пятого 33.5 и восьмого 33.8 элементов И объединены вместе и образуют первый выход 17 коммутатора 3, выходы третьего 33.3, шестого 33.6 и девятого 33.9 элементов И объединены вместе и образуют второй выход 18 коммутатора 3, выходы четвертого 33.4, седьмого 33.7 и десятого 33.10 элементов И объединены вместе и образуют третий выход 19 коммутатора 3. Блок 4 управления (см. фиг.3) содержит четыре входа 21 - 24, являющиеся внешними входами управления функционального преобразователя, три выхода 14 - 16 и двухвходовый элемент 33.11 И, первый вход которого подключен к входу 21, а второй - к входу 24, второй 22 и третий входы 23 транзитом подключены к первому 14 и третьему 16 выходам, а выход элемента 33.11 И подключен к второму вы ходу 15 блока 4 управления. Цифроаналоговый преобразователь 5 (см. фиг.4) содержит три схемы управления 5.1 - 5.3, линейку 5.4 ключей и трехзвенный транзисторный делитель 5.5 напряжения, причем входы схем 5.1 5.3 управления подключены к выходам 17 - 19 коммутатора 3, а выход 20 ЦАП 5 является выходом преобразователя. Функциональный преобразователь работает следующим образом. В исходном состоянии на вход 6 АЦП 1 (см. фиг.1) поступает нулевой исходный сигнал. При этом на выходах 7 - 10 АЦП 1 обеспечивает следующие сигналы: . При поступлении на вход сигнала логической "1" на выходах 7 - 10 имеем , а при логической. "2" - , то есть на соответствующие входы дешифратора 2 поступают (табл.1) парафазные сигналы от компараторов 25, 26 (см. фиг.2) АЦП 1. Теория и практика искусственного интеллекта (Шабанов-Кушнаренко Ю.П. Теория интеллекта. Математические средства. - X.: Вы ща шк. Изд-во при Харьк. ун-те, 1984. - 144с.) использует понятие элемента распознавания, который при подаче на его вход буквы 6 вырабатывает на выходе сигнал "1". При подаче любой другой буквы элемент распознавания вырабатывает сигнал "0", что свидетельствует о несовпадении поступившей буквы с требуемой буквой 6. В случае использования в качестве элемента распознавания АЦП параллельного типа (линейка компараторов с единым опорным делителем напряжения), реализуем элемент распознавания k-значных сигналов с одним входом и k выходами. Для этого необходимо решить задачу однозначного распознавания, когда амплитуда входного kзначного сигнала пересекает опорные уровни с меньшими значениями амплитуд, что достигается путем введения на каждом прямом выходе 7 компаратора 25 (см.фиг.2) дополнительно двухвходового элемента 33.1 И (см. фиг.3), причем к одному входу элемента 33.1 И необходимо подключить прямой 7 выход компаратора 25, а на второй - подать сигнал с инверсного 10 выхода последующего компаратора 26. Каждый раз при срабатывании последующего компаратора 26 на его инверсном выходе 10 появится сигнал "0", который поступит на второй вход элемента 33.1 И, а поскольку на первый вход элемента 33.1 И подано сигнал "1", произойдет логическое отключение выхода 7 предыдущего компаратора 25, распознающего меньшее значение k-значного сигнала, от входа дешифратора 2. Таким образом, используя в АЦП 1 два компаратора 25, 26 можно распознать три значения k-значного сигнала. Для распознавания нулевого сигнала, при этом, не нужен отдельный компаратор, поскольку инверсный сигнал с выхода 8 первого компаратора полностью соответствует тому сигналу, который должен формировать элемент распознавания "0". Сигнал распознавания "1" через элемент 33.1 И проходит в том случае, когда не включён компаратор 26 распознающий логическую "2" и происходит распознавание логической "1", то есть произошло поступление на вход АЦП 1 3значного сигнала с уровнем равным "1". Соответственно, когда на вход 6 поступает логическая "2" происходит отключение прямого выхода 7 предыдущего компаратора 25 и на отдельный прямой выход 9 второго компаратора 26 поступает логическая "1", сигнализирующая, что произошло распознавание логической "2". Все описанные логические функции выполняет дешифратор 2 (см. фиг.3), а логика его работы описывается таблицей истинности (табл.2). Логику работы дешифратора 2 описывает следующая система уравнений где - сигнал инверсного выхода 8 первого компаратора 25; x1 - сигнал прямого выхода 7 первого компаратора 25; - инверсный сигнал с выхода 10 второго компаратора 26; x2 - прямой сигнал с выхода 9 второго компаратора 26. Переходя к описанию работы устройства в деталях отметим, что здесь рассмотрен вариант реализации функционального преобразователя (фиг.1) при реализации значности k = 3. Так как преобразователь является универсальным, то мощность множества реализуемых функций для него равна kk = 33 = 27. В силу требования универсальности к преобразователю три варианта возможных состояний пространственных выходов АЦП 1 и дешифратора 2, необходимо преобразовать в 9 комбинаций управляющих сигналов для ЦАП 5. Дело в том, что в общем случав после распознавания k-значных сигналов на выходах дешифратора 2 получено k вариантов пространственных (параллельных) единичных кодов (см. табл.2), а для формирования выходных сигналов преобразователя необходимо сопоставить каждому из k входных сигналов еще сигналов выходной k-значной функции одной переменной, которая содержит тоже k значений, то есть необходимо сформировать k x k управляющих сигналов на k входах 17 - 19 ЦАП 5. Для пространственного варианта функционирования преобразователя при k = 3 необходимо сформировать пространственную матрицу 3 x 3 управляющих си гналов, что и показано в табл.3, 4 для трех вы ходов 17 - 19 коммутатора 3. Для осуществления этого пространственного распределения в двух измерениях в преобразователь введено коммутатор 3, содержащий три блока 3.k (k = 1 ... 3) коммутации сигналов логической "1" с выходов дешифратора 2. Таким образом, пространственный дешифратор 2 осуществляет вертикальное перемещение логической "1" в матрице управляющих сигналов (см, табл.4) и включает соответствующий блок коммутации 3.k, который в свою очередь осуществляет перекоммутацию поступившей логической "1" в горизонтальном направлении в одном из k возможных направлений для включения соответствующего из ключей 5.4 ЦАП 5. Поскольку все k ключей ЦАП 5 постоянно подключены к соответствующим k значениям опорных сигналов, то на выход 20 преобразователя, по ходу изменений значений k-значной функции на входе 6 преобразователя, будут поступать значения функции, выбранной коммутатором 3 и блоком управления 4 соответственно. Управление процессом логической перекоммутации осуществляется блоком 4 управления под воздействием внешних управляющих си гналов с входов 21 - 24. Характер всех управляющи х сигналов в стр уктуре функционального преобразователя показан в табл.4. Поскольку необходимо сформировать k управляющих пространственных сигнала на входе k блоков 3.k коммутации; на внешние входы 21 - 24 блока 4 управления поступает n-разрядный параллельный код, где 2n ³ k. При таком подходе к выбору разрядности кода естественно возникает определенная избыточность, но для работы преобразователя это обстоятельство несущественно, поскольку часть возможных значений управляющего сигнала можно не использовать или использовать как избыточные для повышения помехоустойчивости. Для нашего примера 22³3, а это значит, что ближайшее значение n = 2. В блоке 4 управления из четырех возможных сочетаний входного сигнала используются только три, к примеру: , , , которые преобразуются в три пространственных варианта единичных кодов: , , . Таким образом, мы снова приходим к таблице истинности (табл.3), аналогичной табл.2 и, соответственно, к алгоритму функционирования и структуре блока 4 управления, аналогичной блоку дешифратора 2. Возвращаясь к функционированию коммутатора 3, необходимо отметить, что на его входы 11 - 13, 14 - 16 поступают сигналы от дешифратора 2 и блока 4 управления, то есть сигналы y0, y1, y2 и r0, r1, r2, причем сигналы от дешифратора 2 осуществляют выбор блока 3.k (k = 1 … 3) коммутации, а сигналы r0, r1, r2 от блока 4 управления - выбор значения из k, которое должно быть подключено на выход 20 преобразователя, соответствующие вы ходы блоков 3.k объединены вместе и образуют три вы хода 17 19 коммутатора 3. Использование проводного ИЛИ правомерно поскольку в каждый такт работы преобразователя активным является только один из выходов блоков 3.k коммутации. Формально работа коммутатора 3 может быть описана следующей системой уравнений В итоге отметим, что введение в функциональный преобразователь коммутатора, состоящего из трех блоков коммутации, каждый из которых выполнен на трех двувходовых элементах И, а также блока управления, включающего двухвходовый элемент И, которые образуют в пространстве структур у параллельного типа с пространственным k-значным кодированием, осуществленным за счет возбужденных состояний в виде двоичных состояний пространственных полюсов, кроме того, использование методов теории интеллекта для описания алгоритмов работы и структуры построения, когда k-значные числа и преобразования над ними описываются с помощью алгебры конечных предикатов, впервые позволило получить простейшие аналитические записи (1), (2) для описания основных компонентов функционального преобразователя, сходные с формулами алгебры логики, но сохраняющие свойства входного k-значного алфавита, параллелизм и однородность структуры и позволяющие предельно просто описать все необходимые преобразования для входных и выходных переменных. Указанные методы и средства позволили реализовать структур у, преобразователя, значительно проще, чем при использовании традиционных решений, которые получаются с использованием алгебры логики и традиционных двоичных методов построения в базисах дизъюнктивных и конъюнктивных нормальных форм, обеспечить однотипность и однородность внутренней структуры, существенно уменьшить аппаратурные затраты на создание преобразователя, упростить шинную коммутацию, а также повысить быстродействие за счет минимальной задержки во всех звеньях преобразователя.

ДивитисяДодаткова інформація

Назва патенту англійськоюFunctional generator

Автори англійськоюBondarenko Mykhailo Fedorovych, Konoplianko Zenovii Dmytrovych, Chetverykov Hryhorii Hryhorovych

Назва патенту російськоюФункциональный преобразователь

Автори російськоюБондаренко Михаил Федорович, Коноплянко Зеновий Дмитриевич, Четвериков Григорий Григорович

МПК / Мітки

МПК: H03K 19/08

Мітки: функціональний, перетворювач

Код посилання

<a href="https://ua.patents.su/5-14935-funkcionalnijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Функціональний перетворювач</a>

Попередній патент: Спосіб одержання біостимулятора росту та розвитку рослин з гумусовміщуючих речовин

Наступний патент: Пристрій для піднімання скла дверей автомобіля

Випадковий патент: Подрібнювач грубих кормів