Статистичний аналізатор викидів і провалів напруги

Формула / Реферат

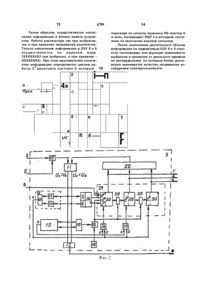

1. Статистический анализатор выбросов и провалов напряжения, содержащий пороговый элемент, RS-триггер, счетчик и первый блок памяти, отличающийся тем, что в него введены дешифратор длительности выбросов и провалов напряжения, второй блок памяти, регистр, аналого-цифровой преобразователь и преобразователь переменного напряжения в постоянное, вход которого является информационным входом анализатора, а выход подключен к информационному входу аналого-цифрового преобразователя и через пороговый элемент к старшим разрядам адресного входа первого блока памяти и информационного входа регистра, выход которого соединен с адресным входом второго блока памяти, информационный вход которого подключен к первому входу дешифратора выбросов и провалов напряжения, второй выход которого соединен с входом установки нуля регистра, а третий выход подключен к входу управления записью и считыванием второго блока памяти и к входу разрешения считывания регистра, младшие разряды информационного входа регистра и адресного входа первого блока памяти соединены с информационным входом счетчика, выход переполнения которого подключен к R-входу триггера, S - вход которого является входом пуска анализатора, а прямой выход соединен с информационным входом дешифратора выбросов и провалов напряжения и с входом запуска аналого-цифрового преобразователя, вход сброса которого соединен с инверсным выходом триггера, а выход конца работы подключен к счетному входу счетчика, к входу запуска дешифратора выбросов и провалов напряжения и к входам управления записью регистра и управления записью - считыванием первого блока памяти, информационный вход которого подключен к выходу аналого-цифрового преобразователя.

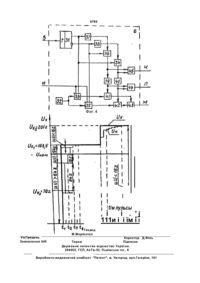

2. Анализатор по п.1,отличающий-с я тем, что аналого-цифровой преобразователь содержит реверсивный счетчик, блок сравнения, ключ, два элемента ИЛИ-НЕ, элемент ИЛИ триггер, элемент И, цифро-аналоговый преобразователь, два амплитудных анализатора, элемент "исключающее ИЛИ" и генератор тактовых импульсов, выход которого соединен с первым входом элемента И, выход которого подключен к счетному входу реверсивного счетчика, разрядный выход которого соединен с входами цифро-аналогового преобразователя, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом ключа, информационный и управляющий входы которого являются соответственно информационным и пусковым входами преобразователя, входом сброса которого является вход сброса реверсивного счетчика, выход "больше" блока сравнения соединен с первыми входами амплитудных анализаторов, с S - входом триггера и с первыми входами первого элемента ИЛИ-НЕ и элемента ИЛИ, выход которого подключен к второму входу элемента И, выход "меньше" блока сравнения подключен к вторым входам амплитудных анализаторов, к R - входу триггера и к вторым входам элемента ИЛИ и первого элемента ИЛИ-НЕ, выход которого является выходом конца работы преобразователя, выход первого амплитудного анализатора соединен с первыми входами второго элемента ИЛИ-НЕ и элемента "исключающее ИЛИ", вторые входы которых подключены к выходу второго амплитудного анализатора, выходы второго элемента ИЛИ-НЕ, элемента "исключающее ИЛИ" и первого амплитудного анализатора подключены к соответствующим разрядным входам разрешения счета реверсивного счетчика, суммирующий и вычитающий входы которого соединены соответственно с прямым и инверсным выходами триггера.

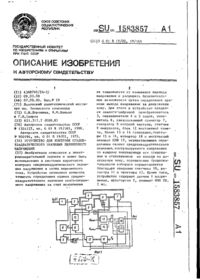

3. Анализатор по п.1,отличающий-с я тем, что дешифратор длительности выбросов и провалов напряжения содержит два счетчика, четыре элемента задержки, четыре элемента И, три элемента ИЛИ и генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены к счетным входам соответственно первого и второго счетчиков, выходы которых соединены с входами первого элемента ИЛИ, выход которого является первым выходом дешифратора, информационный вход которого соединен с вторыми входами первого и второго элементов И, вход запуска дешифратора подключен к счетному входу триггера, прямой выход которого соединен с третьим входом первого элемента И, с первым входом третьего элемента И и через первый элемент задержки - с первым входом четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ и через второй элемент задержки -к входу обнуления первого счетчика и к первому входу третьего элемента ИЛИ, выход которого является вторым выходом дешифратора, третьим выходом которого является выход второго элемента ИЛИ, инверсный выход триггера соединен с третьим входом второго элемента И, с вторым входом четвертого элемента И и через третий элемент задержки - с вторым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и через четвертый элемент задержки подключен к второму входу третьего элемента ИЛИ и к входу обнуления второго счетчика.

Текст

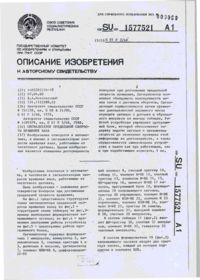

1. Статистический анализатор выбросов и провалов напряжения, содержащий поро говый элемент, RS-триггер, счетчик и первый блок памяти, о т л и ч а ю щ и й с я тем, что в него введены дешифратор длительности выбросов и провалов напряжения, второй блок памяти, регистр, аналого-цифровой преобразователь и преобразователь пере менного напряжения в постоянное, вход ко торого является информационным входом анализатора, а выход подключен к информа ционному входу аналого-цифрового преоб разователя и через пороговый элемент к старшим разрядам адресного входа первого блока памяти и информационного входа ре гистра, выход которого соединен с адрес ным входом второго блока памяти, информационный вход которого подключен к первому входу дешифратора выбросов и провалов напряжения, второй выход которо го соединен с входом установки нуля регист ра, а третий выход подключен к входу управления записью и считыванием второго блока памяти и к входу разрешения считы вания регистра, младшие разряды информа ционного входа регистра и адресного входа первого блока памяти соединены с инфор мационным входом счетчика, выход пере полнения которого подключен к R-входу триггера, S - вход которого является входом пуска анализатора, а прямой выход соединен с информационным входом дешифратора выбросов и провалов напряжения и с входом запуска аналого-цифрового преобразователя, вход сброса которого соединен с инверсным выходом триггера, а выход конца работы подключен к счетному входу счетчика, к входу запуска дешифратора выбросов и провалов напряжения и к входам управления записью регистра и управления записью - считыванием первого блока памяти, информационный вход которого подклю-' чен к выходу аналого-ц ифрового преобразователя. 2. Анализатор по п. 1,отличающийс я тем, что аналого-цифровой преобразователь содержит реверсивный счетчик, блок сравнения, ключ, два элемента ИЛИ-НЕ, элемент ИЛИ триггер, элемент И, цифроаналоговый преобразователь, два амплитудных анализатора, элемент "исключающее ИЛИ" и генератор тактовых импульсов, выход которого соединен с первым входом элемента И, выход которого подключен к счетному входу реверсивного счетчика, разрядный выход которого соединен с входами цифро-аналогового преобразователя, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом ключа, информационный и управляющий входы которого являются соответственно информационным и пусковым входами преобразователя, входом сброса которого является вход сброса реверсивного счетчика, выход "больше" блока сравнения соединен с первыми входами амплитудных анализаторов, с S - входом триггера и с первыми входами первого элемента ИЛЙ-НЕ и элемента ИЛИ, выход которого подключен к второму входу элемента И, выход "меньше" блока сравнения подклю С > О 6799 чен к вторым входам амплитудных анализаторов, к R - входу триггера и к вторым входам элемента ИЛИ и первого элемента ИЛИ-НЕ, выход которого является выходом конца работы преобразователя, выход первого амплитудного анализатора соединен с первыми входами второго элемента ИЛИНЕ и элемента "исключающее ИЛИ", вторые входы которых подключены к выходу второго амплитудного анализатора, выходы второго элемента ИЛИ-НЕ, элемента "исключающее ИЛИ" и первого амплитудного анализатора подключены к соответствующим разрядным входам разрешения счета реверсивного счетчика, суммирующий и вычитающий входы которого соединены соответственно с прямым и инверсным выходами триггера. 3. Анализатор по п. 1 , о т ли ч а ю щи й с я тем, что дешифратор длительности выбросов и провалов напряжения содержит два счетчика, четыре элемента задержки, четыре элемента И, три элемента ИЛИ и генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены к счетным входам соответственно первого и второго счетчиков, выходы кото рых соединены с входами первого элемента ИЛИ, выход которого является первым выходом дешифратора, информационный вход которого соединен с вторыми входами первого и второго элементов И, вход запуска дешифратора подключен к счетному входу триггера, прямой выход которого соединен с третьим входом первого элемента И, с первым входом третьего элемента И и через первый элемент задержки - с первым входом четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ и через второй элемент задержки к входу обнуления первого счетчика и к первому входу третьего элемента ИЛИ, выход которого является вторым выходом дешифратора, третьим выходом которого является выход второго элемента ИЛИ, инверсный выход триггера соединен с третьим входом второго элемента И, с вторым входом четвертого элемента И и через третий элемент задержки - с вторым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и через четвертый элемент задержки подключен к второму входу третьего элемента ИЛИ и к входу обнуления второго счетчика. Изобретение относится к электроизмеТехнический результат достигается тем, рительной технике и может быть использочто в статистический анализатор выбросов и вано при аппаратурном контроле качества провалов напряжения, содержащий пороговый элемент, RS-триггер, счетчик и первый электрической энергии по выбросам и провалам действующего значения напряжения. 5 блок памяти, введены дешифратор длительНаиболее близким по технической сущности выбросов и провалов напряжения, второй блок памяти, регистратор, аналогоности к предлагаемому решению является цифровой преобразователь и преобразовастатистический анализатор выбросов и протель переменного напряжения в валов напряжения, .содержащий нуль-ор10 постоянное, вход которого является инфорган,формирователь модуля, измерительные мационным входом анализатора, а выход пороговые элементы, элементы ИЛИ, RSподключен к информационному входу анатриггер, одновибратор, блок задержки, лого-цифрового преобразователя и через шифратор, счетчик и оперативное запомипороговый элемент - к старшим разрядам нающее устройство [авторское свидетельство СССР N2 947775 кл. G 01 R 19.04. 1982 г]. 15 адресного входа первого блока памяти и информационного входа регистра, выход которого соединен с адресным входом второго Общий недостаток известного устройстблока памяти, информационный вход котова - узкие функциональные возможности. рого подключен к первому выходу дешифраЗадачей изобретения является расши20 тора выбросов и провалов напряжения, рение функциональных возможностей уствторой выход которого соединен со входом ройства путем одновременного установки нуля регистра, а третий выход параллельного анализа как амплитуды, так и подключен ко входу управления записью и длительности выбросов и провалов напрясчитыванием второго блока памяти и ко вхожения. 25 ду разрешения считывания регистра, млад 6799 шиє разряды информационного входа регистра и адресного входа первого блока памяти соединены с информационным выходом счетчика, выход переполнения которого подключен к R-входу триггера, S-вход кото- 5 рого является входом пуска анализатора, а прямой выход соединен с информационным входом дешифратора выбросов и провалов напряжения и со входом запуска аналогоцифрового преобразователя, вход сброса 10 которого соединен с инверсным выходом триггера, а выход конца работы подключен к счетному входу счетчика, ко входу запуска дешифратора выбросов и провалов напряжения и ко входам управления записью ре- 15 гистра и управления записью - считыванием первого блока памяти, информационный вход которого подключен к выходу аналогоцифрового преобразователя. 20 Аналого-цифровой преобразователь содержит реверсивный счетчик, блок сравнения, ключ, два элемента ИЛИ-НЕ, элемент ИЛИ, триггер, элемент И, цифро-аналоговый преобразователь, два амплитудных анали- 25 затора, элемент исключающее ИЛИ и генератор тактовых импульсов, выход которого соединен с первым входом элемента И, выход которого подключен к счетному входу реверсивного счетчика, разрядный выход 30 которого соединен со входами цифро-аналогового преобразователя, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом ключа, ин форм ацион ный и 35 управляющий входы которого являются соответственно информационный и пусковой входами преобразователя, входом -сброса которого является вход сброса реверсивного счетчика, выход "больше" блока сравне- 40 ния соединен с первыми входами амплитудных анализаторов, с S-входом триггера и с первыми входами первого элемента ИЛИ-НЕ и элемента ИЛИ, выход которого подключен ко второму входу элемента 45 И, выход "меньше" блока сравнения подключен ко вторым входам амплитудных анализаторов, к R - входу триггера и ко вторым входам элемента ИЛИ и первого элемента ИЛИ-НЕ, выход которого является выходом 50 конца работы преобразователя, выход первого амплитудного анализатора соединен с первыми входами второго элемента ИЛИ-НЕ и элемента исключающее ИЛИ, вторые входы которых подключены к выходу ампли- 55 тудного анализатора, выходы второго элемента ИЛИ-НЕ, элемента исключающее ИЛИ и первого амплитудного анализатора подключены к соответствующим разрядным входам разрешения счета реверсивного счетчика, суммирующий и вычитающий входы которого соединены соответственно с прямым и инверсным выходами триггера. Дешифратор длительности выбросов и провалов напряжения содержит счетчики, элементы задержки, элементы И, элементы ИЛИ и генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены к счетным входам одноименных счетчиков, выходы которых соединены со входами первого элемента ИЛИ, выход которого является первым выходом дешифратора, информационный вход которого соединен со вторыми входами первого и второго элементов И, вход запуска дешифратора подключен к счетному входу триггера, прямой выход которого соединен с третьим входом первого элемента И, с первым входом третьего элемента И и через первый элемент задержки - с перовым входом четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ и через второй элемент задержки -ко входу обнуления первого счетчика и к первому входу третьего элемента ИЛИ, выход которого является выход второго элемента ИЛИ, инверсный выход триггера соединен с третьим входом второго элемента И, со вторым входом четвертого элемента И и через третий элемент задержки - со вторым входом третьего элемента И, выход которого соединен со вторым входом второго элемента ИЛИ и через четвертый элемент задержки подключен ко второму входу третьего элемента ИЛИ и ко входу обнуления второго счетчика. Принципиальное отличие предлагаемого устройства от прототипа заключается в том, что наличие преобразователя переменного напряжения в постоянное и аналогоцифрового преобразователя, а также дешифратора длительности выбросов и провалов напряжения, регистра адреса и второго оперативного запоминающего блока позволило коренным образом изменить характер обработки исходной информации в устройстве, что способствовало одновременному параллельному анализу как амплитуды, так и длительности выбросов и провалов напряжения, и тем самым существенному расширению функциональных возможностей устройства. На фиг. 1 представлена функциональная схема предлагаемого статистического анализатора выбросов и провалов напряжения; на фиг. 2 - блок-схема аналого-цифрового преобразователя; на фиг. 3 - блок-схема дешифратора длительности выбросов и провалов напряжения; на фиг. 4 - временные 6799 8 диаграммы напряжения на выходах отдельсоединены соответственно с прямым и инных составных о іементов, иллюстрирующие версным выходами триггера 14 знака, едиего работу. ничный и нулевой входы которого Статистический анализатор выбросов и соответственно объединены с входами папровалов напряжения содержит преобразо- 5 раллельно соединенных элементов ИЛИ 15, ватель 1 переменного напряжения в постоэлемента ИЛИ-НЕ 17 и пороговых элеменянное, вход которого является тов 23 и 24 амплитудных анализаторов 12 и информационным входом устройства, а вы13, и подключены к выходам "Больше" (>) и ход подключен к точке, объединяющей вход "Меньше" (

ДивитисяДодаткова інформація

Назва патенту англійськоюStatistical voltage surge and fall analyzer

Автори англійськоюMaier Viktor Yakovych

Назва патенту російськоюСтатистический анализатор выбросов и провалов напряжения

Автори російськоюМайер Виктор Яковлевич

МПК / Мітки

МПК: G06F 17/18

Мітки: провалів, аналізатор, викидів, статистичний, напруги

Код посилання

<a href="https://ua.patents.su/8-6799-statistichnijj-analizator-vikidiv-i-provaliv-naprugi.html" target="_blank" rel="follow" title="База патентів України">Статистичний аналізатор викидів і провалів напруги</a>

Попередній патент: Спосіб виготовлення статору електричної машини

Наступний патент: Подрібнювач кормів

Випадковий патент: Спосіб отримання твердих розчинів gete-snte-bi2te3-sb2te3