Програмований пристрій

Номер патенту: 107437

Опубліковано: 25.12.2014

Автори: Защолкін Костянтин В'ячеславович, Дрозд Олександр Валентинович, Нестеренко Сергій Анатолійович, Кузнєцов Микола Олександрович, Дрозд Юлія Володимирівна

Формула / Реферат

Програмований пристрій, що містить перший регістр і перший мультиплексор, при цьому тактовий вхід і перший вхід прийому даних пристрою підключено відповідно до тактового входу і входу послідовного прийому даних першого регістра, виходи розрядів 0…2n-1 якого підключено відповідно до інформаційних входів 0…2n-1 першого мультиплексора, входи n адресних розрядів 1…n першого мультиплексора є першим адресним входом пристрою, який відрізняється тим, що введено другий 2n-розрядний регістр і другий n-адресний мультиплексор, при цьому тактовий вхід і другий вхід прийому даних пристрою підключено відповідно до тактового входу та входу послідовного прийому даних другого регістра, входи молодших адресних розрядів 1…n-1 другого мультиплексора є другим адресним входом пристрою, вхід режиму пристрою підключено до входів дозволу паралельного прийому даних першого та другого регістрів, виходи розрядів 0…2n-1 першого регістра підключено відповідно до його інверсних входів розрядів 0…2n-1, виходи розрядів 0…2n-1 другого регістра підключено відповідно до його входів розрядів 2n-1…2n-1, а виходи розрядів 2n-1…2n-1 другого регістра підключено відповідно до його входів розрядів 0…2n-1, виходи розрядів 0…2n-1 другого регістра підключено відповідно до інформаційних входів 0…2n-1 другого мультиплексора, вихід першого мультиплексора підключено до входу старшого адресного розряду n другого мультиплексора, вихід якого підключено до виходу пристрою.

Текст

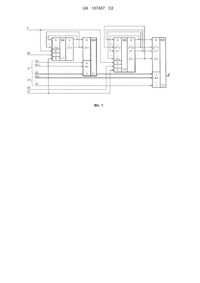

Реферат: Винахід належить до обчислювальної техніки, а саме до програмованих цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Програмований пристрій призначений для обчислення прямого або інверсного значення першої логічної функції на виході першого мультиплексора та прямого значення другої логічної функції на виході другого мультиплексора, що шляхом введення другого регістра та другого мультиплексора забезпечує дві версії програмування першої та другої функцій пристрою, за якими перша функція може бути обчислена з прямим або інверсним значенням, а друга функція не змінює свого значення, що призводить до розширення функціональних можливостей обчислення будь-якої першої функції при константній несправності будь-якого одного з виходів першого регістра. UA 107437 C2 (12) UA 107437 C2 UA 107437 C2 5 10 15 20 25 30 35 40 45 50 55 60 Пропонований винахід належить до обчислювальної техніки, а саме до програмованих цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Відомий пристрій на основі мультиплексора, адресні входи якого є входами аргументів логічної функції пристрою, інформаційні входи з номерами наборів, що приймають в таблиці істинності логічної функції нульові та одиничні значення, підключені відповідно до входів нульового та одиничного значення пристрою, а вихід є виходом пристрою [1]. Недоліки аналогу: обмежені функціональні можливості - пристрій обчислює тільки одну конкретну логічну функцію. Найбільш близьким до запропонованого винаходу по технічній суті та результату, що досягається, є програмований пристрій для обчислення логічної функції n змінних, який містить n 2 -розрядний регістр та n-адресний мультиплексор, при цьому тактовий вхід та вхід послідовного прийому даних регістра є першим та другим входами пристрою, вхід n адресних n розрядів мультиплексора є третім входом пристрою, інформаційні входи 0…2 -1 n мультиплексора підключено до виходів відповідних розрядів 0…2 -1 регістра, а вихід мультиплексора підключено до виходу пристрою [2]. Недоліки прототипу: константна несправність 0 або 1 на будь-якому одному з виходів розрядів регістра не дозволяє обчислити всі логічні функції, що програмуються в регістрі. Наприклад, константна несправність "0" на нульовому виході регістра не дозволяє обчислити логічні функції, що приймають одиничне значення на нульовому наборі змінних. Це суттєво обмежує функціональні можливості програмованого пристрою. Задача винаходу - створення програмованого пристрою, в якому шляхом введення другого регістра та другого мультиплексора забезпечено обчислення прямого або інверсного значення першої логічної функції на виході першого мультиплексора та прямого значення другої логічної функції на виході другого мультиплексора, в результаті чого розширюються функціональні можливості щодо обчислення будь-якої першої логічної функції при константній несправності будь-якого одного з виходів першого регістра. n Поставлена задача вирішується тим, що у програмований пристрій, що містить перший 2 розрядний регістр і перший n-адресний мультиплексор, при цьому тактовий вхід і перший вхід прийому даних пристрою підключено відповідно до тактового входу і входу послідовного n прийому даних першого регістра, виходи розрядів 0…2 -1 якого підключено відповідно до n інформаційних входів 0…2 -1 першого мультиплексора, входи n адресних розрядів 1…n першого мультиплексора є першим адресним входом пристрою, згідно з винаходом введено n другий 2 -розрядний регістр і другий n-адресний мультиплексор, при цьому тактовий вхід і другий вхід прийому даних пристрою підключено відповідно до тактового входу та входу послідовного прийому даних другого регістра, входи молодших адресних розрядів 1…n-1 другого мультиплексора є другим адресним входом пристрою, вхід режиму пристрою підключено до входів дозволу паралельного прийому даних першого та другого регістрів, n виходи розрядів 0…2 -1 першого регістра підключено відповідно до його інверсних входів n n розрядів 0…2 -1, виходи розрядів 0…2 -1 другого регістра підключено відповідно до його входів n-1 n n-1 n розрядів 2 …2 -1, а виходи розрядів 2 …2 -1 другого регістра підключено відповідно до його n n входів розрядів 0…2 -1, виходи розрядів 0…2 -1 другого регістра підключено відповідно до n інформаційних входів 0…2 -1 другого мультиплексора, вихід першого мультиплексора підключено до входу старшого адресного розряду n другого мультиплексора, вихід якого підключено до виходу пристрою. Технічний ефект від запропонованого рішення полягає в тому, що шляхом введення другого n 2 -розрядного регістра та другого n-адресного мультиплексора забезпечено дві версії програмування першої та другої логічних функцій пристрою, за якими перша логічна функція може бути обчислена з прямим або інверсним значенням, а друга логічна функція не змінює свого значення, що призводить до розширення функціональних можливостей обчислення будьякої першої логічної функції при константній несправності будь-якого одного з виходів першого регістра. Розширення функціональних можливостей пристрою можна оцінити наступним чином. В n прототипі при константній несправності будь-якого одного розряду першого 2 -розрядного регістра кількість логічних функцій, що обчислюються на виході першого n-адресного мультиплексора, зменшується вдвічі. В запропонованому рішенні при неможливості внаслідок несправності обчислення прямого значення першої логічної функції (на виході першого nn адресного мультиплексора) код на виході першого 2 -розрядного регістра змінюється на інверсний. Це забезпечує обчислення інверсного значення першої логічної функції. При цьому в n другому 2 -розрядному регістрі міняються місцями перша та друга половини коду, що компенсує інверсію на вході старшого розряду адреси другого n-адресного мультиплексора і зберігає 1 UA 107437 C2 5 10 15 20 25 30 значення логічної функції на виході пристрою. Таким чином, запропоноване рішення відновлює можливість обчислення всіх логічних функцій на виході першого n-адресного мультиплексора, тобто подвоює їхню кількість. n Суть винаходу пояснюється кресленням на фіг. 1, де зображено перший 1.1 та другий 1.2 2 розрядні регістри; перший 2.1 та другий 2.2 n-адресні мультиплексори, тактовий вхід Т пристрою, перший D1 та другий D2 входи прийому даних пристрою, перший А1 та другий А2 адресні входи пристрою, вхід М режиму пристрою та вихід R пристрою, при цьому вхід Т пристрою підключено до тактових входів С регістрів 1.1 та 1.2, входи D1 та D2 підключено відповідно до входів І послідовного прийому даних регістрів 1.2 та 1.2, входи n адресних розрядів 1…n мультиплексора 2.1 є входом А1 пристрою, входи молодших адресних розрядів 1…n-1 мультиплексора 2.2 є входом А2 пристрою, вхід М підключено до входів V дозволу n паралельного прийому даних регістрів 1.1 та 1.2; виходи розрядів 0…2 -1 регістра 1.1 n підключено відповідно до його інверсних входів розрядів 0…2 -1 та до інформаційних входів n n 0…2 -1 мультиплексора 2.1, виходи розрядів 0…2 -1 регістра 1.2 підключено відповідно до його n-1 n n-1 n входів розрядів 2 …2 -1, а виходи розрядів 2 …2 -1 регістра 1.2 підключено відповідно до n n його входів розрядів 0…2 -1, виходи розрядів 0…2 -1 регістра 1.2 підключено відповідно до n інформаційних входів 0…2 -1 мультиплексора 2.2, вихід мультиплексора 2.1 підключено до входу старшого адресного розряду n мультиплексора 2.2, вихід якого підключено до виходу R пристрою. На фіг. 2 показано часові діаграми роботи блоків пристрою для n=4, а саме для входів М Т, D1, D2 пристрою, для кодів RG 1.1 та RG 1.2 на виходах регістрів 1.1 та 1.2, для розрядів А11, А12, А13, А14 входу А1 пристрою, розрядів А21, А22, А23 входу А2 пристрою, а також виходів MX 2.1 та MX 2.2 (вихід R пристрою) мультиплексорів 2.1 та 2.2. Часові діаграми розбиті на 4 періоди: І-IV. Пристрій працює у такий спосіб. На періоді І виконується програмування пристрою, для чого на вхід Т пристрою та відповідно n на тактові входи регістрів 1.1 та 1.2 подається серія з 2 тактових імпульсів типу "меандр", а на входи D1 та D2 і відповідно входи І послідовного прийому даних регістрів 1.1 та 1.2 надходять послідовні коди, починаючи з молодших розрядів. У даному прикладі коди приймають значення, показані в табл. 1 у двійковій та 16-й (16 СС) системах числення. Таблиця 1 Приклад кодів для програмування пристрою Коди RG1.1 RG 1.2 35 40 45 50 15 1 0 14 0 1 13 0 1 12 0 0 11 0 1 10 0 0 Двійкові розряди 9 8 7 6 0 0 0 0 0 1 1 0 5 0 0 4 0 1 3 0 0 2 0 1 1 0 1 0 0 0 16 СС 800015 699616 За цими кодами 800016 та 699616 на виходах мультиплексорів 2.1 та 2.2 обчислюються функції логічного множення та суми за модулем два від чотирьох аргументів, відповідно. На періоді II показано роботу пристрою при відсутності несправностей. На входи А1 та А2 пристрою надходять всі набори значень від 0000 2 до 11112 та від 0002 до 1112, відповідно. Мультиплексори 2.1 та 2.2 одержують ці послідовності наборів на адресні входи 1…4 та 1…3. Мультиплексор 2.1 вибирає за цими адресами значення розрядів регістра 1.1 від молодшого 0 до старшого 15, транслюючи на свій вихід послідовність 0…012. Мультиплексор 2.2 приймає цю послідовність на старший адресний вхід 4, вибираючи значення розрядів регістра 1.2 від молодшого 0 до розряду 7, потім знову значення розрядів 0-6 та розряду 15, формуючи на виході код 01101001011010002=696816. На періоді III показано роботу пристрою на тих же послідовностях наборів, що подаються на входи А1 та А2 пристрою, але при константній несправності "1" на виході розряду 7 регістра 1.1. При транслюванні цього помилкового значення розряду 7 на вихід мультиплексора 2.1 далі його приймає на адресний вхід 4 мультиплексор 2.2, вибираючи з виходів регістра 1.2 на вихід R пристрою помилково значення "0" розряду 15 замість значення "1" розряду 7. Помилкове значення на виході R пристрою та правильне значення на попередньому періоді виділено рамками. На періоді IV показано роботу пристрою, що обчислює правильний результат на виході R при константній несправності "1" на виході розряду 7 регістра 1.1 з переходом на другу версію обчислення логічних функцій на виходах мультиплексорів 2.1 та 2.2. Для цього на вхід М 2 UA 107437 C2 5 10 15 20 пристрою подається сигнал, за яким відбувається перезапис кодів в регістрах 1.1 та 1.2. Перезапис коду регістра 1.1 виконується зі зміною його значення 8000 16 на інверсне 7FFE16 з помилкою у розряді 7. Однак несправний вихід розряду 7 зберігає значення константної несправності "1", яке тепер співпадає з правильним значенням в проінвертованому коді 7FFE 16. Перезапис коду регістра 1.2 відбувається з переміною місць його старшої та молодшої половини, що перетворює його значення 699616 на 966916. Мультиплексор 2.1 обчислює правильне інверсне значення першої логічної функції, яке подається на старший адресний розряд мультиплексора 2.2, забезпечуючи вибір значень розрядів регістра 2.2 з іншої половини коду порівняно до прямого значення першої логічної функції. Таким чином, на виході мультиплексора 2.2 та виході пристрою R обчислюється правильне значення другої логічної функції, включаючи позицію, виділену на часових діаграмах рамкою, де на попередньому періоді відобразилося помилкове значення. Пристрій може бути використаний для відновлення правильних результатів у разі прояву відмов у LUT-орієнтованій архітектурі програмованих логічних інтегральних схем (LUT: Look-Up Table - кодова таблиця). Джерела інформації: 1. Основи цифрових систем / І.П. Барабаш, М.П. Благодатний, В.Я. Жихарев та ін. Підручник - Харків: Нац. Аерокосмічний ун-т "Харк. авіац. ін-т", 2002. - 672 с., C. 159, рис. 5.18; 2. Maxfield С. The Design Warrior's Guide to FPGAs, Newnes, 2004 (рис. 3-19, стор. 51). Режим доступу: http://profs.basu.ac.ir/abdoli/upload_file/722.file_ref.2202.2686.pdf. ФОРМУЛА ВИНАХОДУ 25 30 35 40 Програмований пристрій, що містить перший регістр і перший мультиплексор, при цьому тактовий вхід і перший вхід прийому даних пристрою підключено відповідно до тактового входу і n входу послідовного прийому даних першого регістра, виходи розрядів 0…2 -1 якого підключено n відповідно до інформаційних входів 0…2 -1 першого мультиплексора, входи n адресних розрядів 1…n першого мультиплексора є першим адресним входом пристрою, який n відрізняється тим, що введено другий 2 -розрядний регістр і другий n-адресний мультиплексор, при цьому тактовий вхід і другий вхід прийому даних пристрою підключено відповідно до тактового входу та входу послідовного прийому даних другого регістра, входи молодших адресних розрядів 1…n-1 другого мультиплексора є другим адресним входом пристрою, вхід режиму пристрою підключено до входів дозволу паралельного прийому даних n першого та другого регістрів, виходи розрядів 0…2 -1 першого регістра підключено відповідно n n до його інверсних входів розрядів 0…2 -1, виходи розрядів 0…2 -1 другого регістра підключено n-1 n n-1 n відповідно до його входів розрядів 2 …2 -1, а виходи розрядів 2 …2 -1 другого регістра n n підключено відповідно до його входів розрядів 0…2 -1, виходи розрядів 0…2 -1 другого регістра n підключено відповідно до інформаційних входів 0…2 -1 другого мультиплексора, вихід першого мультиплексора підключено до входу старшого адресного розряду n другого мультиплексора, вихід якого підключено до виходу пристрою. 3 UA 107437 C2 Комп’ютерна верстка Л. Ціхановська Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюNesterenko Serhii Anatoliiovych

Автори російськоюНестеренко Сергей Анатолиевич

МПК / Мітки

МПК: G06F 11/263

Мітки: програмований, пристрій

Код посилання

<a href="https://ua.patents.su/6-107437-programovanijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Програмований пристрій</a>

Попередній патент: Спосіб візуалізації наборів даних та пристрій для його здійснення

Наступний патент: Тренажер дихальний (варіанти)

Випадковий патент: Гайковерт