Багатоканальний цифровий корелятор

Номер патенту: 116116

Опубліковано: 12.02.2018

Автори: Гуменний Петро Володимирович, Албанський Іван Богданович, Николайчук Ярослав Миколайович, ПРОЦЮК ГАЛИНА ЯРОСЛАВІВНА

Формула / Реферат

Багатоканальний цифровий корелятор, який містить синхронізатор, (n+1)-каскадний регістр зсуву, n накопичувачів, виходи яких є виходами пристрою, перетворювач "аналог-код" послідовного наближення, перший вхід якого є входом пристрою, другий вхід підключений до першого виходу синхронізатора, а вихід підключений до першого входу регістра, другий вхід якого підключений до другого виходу синхронізатора, комутаційний регістр зсуву, перший вхід якого з'єднаний з першим виходом синхронізатора, другий вхід з'єднаний з другим виходом синхронізатора, а вихідна шина з'єднана з відповідними блоками і підключена в кожному каналі до відповідних перших входів групи логічних елементів "І", другі і треті входи яких з'єднані з відповідними шинами і-х та і-1-х каскадів багатокаскадного регістра зсуву, група логічних елементів "І-НЕ", перші входи яких відповідно з'єднані з вихідною шиною 2k-1-го розряду регістра зсуву, другі і треті входи групи логічних елементів "І-НЕ" відповідно з'єднані з вихідними шинами і-х та і-1-х каскадів регістра зсуву, а виходи з'єднані з четвертими входами групи логічних елементів "І", який відрізняється тим, що виходи логічних елементів І в кожному каналі підключені до входів додатково введених синхронних накопичуючих лічильників теоретико-числового базису Галуа, виходи яких підключені до входів додатково введених дешифраторів, виходи яких є виходами пристрою.

Текст

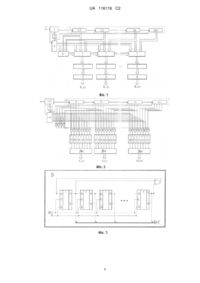

Реферат: Винахід належить до галузі обчислювальної техніки. Багатоканальний цифровий корелятор, який містить синхронізатор, (n+1)-каскадний регістр зсуву, n накоплювачів, виходи яких є виходами пристрою, перетворювач "аналог-код" послідовного наближення, перший вхід якого є входом пристрою, другий вхід підключений до першого виходу синхронізатора, а вихід підключений до першого входу регістра, другий вхід якого підключений до другого виходу синхронізатора, комутаційний регістр зсуву, перший вхід якого з'єднаний з першим виходом синхронізатора, другий вхід з'єднаний з другим виходом синхронізатора, а вихідна шина з'єднана з відповідними блоками і підключена в кожному каналі до відповідних перших входів UA 116116 C2 (12) UA 116116 C2 групи логічних елементів "І", другі і треті входи яких з'єднані з відповідними шинами і-х та і-1-х каскадів багатокаскадного регістра зсуву, група логічних елементів "І-НІ", перші входи яких відповідно з'єднані з вихідною шиною 2k-1-го розряду регістра зсуву, другі і треті входи групи логічних елементів "І-НІ" відповідно з'єднані з вихідними шинами і-х та і-1-х каскадів регістра зсуву, а виходи з'єднані з четвертими входами групи логічних елементів "І", а виходи логічних елементів І в кожному каналі підключені до входів додатково введених синхронних накопичуючих лічильників, виходи яких підключені до входів додатково введених дешифраторів. UA 116116 C2 5 10 Пристрій належить до галузі обчислювальної техніки і призначений для статистичного аналізу випадкових процесів шляхом обчислення коваріаційної функції. Відомий аналог - багатоканальний цифровий корелятор призначений для обчислення автокореляційної функції на основі дискретів центрованих процесів, який містить синхронізатор, (n+1)-каскадний регістр зсуву, n накопичувачів, перетворювач "аналог-код", вихід якого підключений до входу регістра зсуву, а вхід до першого виходу синхронізатора, шина зсуву регістра зв'язана з другим виходом синхронізатора [А.С. СССР № 337784, кл. G06F 15/34. Бюллетень № 15. - 1972]. Недоліком багатоканального цифрового корелятора є низька швидкодія та обмежені функціональні можливості обумовлені тим, що пристрій містить часо-імпульсний перетворювач "аналог-код", а операція накопичення суми добутків текучих та зміщених кодів виконується шляхом унітарного сумування кодів, які зсуваються в регістрі зсуву. Функціональні обмеження відомого пристрою визначаються тим, що на його виходах формуються значення функції автокореляції центрованих процесів, асимптотика якої відповідає умовам 15 20 25 30 35 40 45 50 55 K xx (0) Dx ; K xx () 0 (фіг. 1), де Dx - дисперсія випадкового процесу. Відомий прототип - Багатоканальний цифровий корелятор, який містить синхронізатор, (n+1)-каскадний регістр зсуву, n накопичувачів, виходи яких є виходами пристрою, перетворювач "аналог-код" послідовного наближення, перший вхід якого є входом пристрою, другий вхід підключений до першого виходу синхронізатора, а вихід підключений до першого входу регістра, другий вхід якого підключений до другого виходу синхронізатора, комутаційний регістр зсуву, перший вхід якого з'єднаний з першим виходом синхронізатора, другий вхід з'єднаний з другим виходом синхронізатора, а вихідна шина з'єднана з відповідними блоками і підключена в кожному каналі до відповідних перших входів групи логічних елементів "І", другі і треті входи яких з'єднані з відповідними шинами і-х та і-1-х каскадів багатокаскадного регістра зсуву, група логічних елементів "I-НЕ", перші входи яких відповідно з'єднані з вихідною шиною 2k-1-го розряду регістра зсуву, другі і треті входи групи логічних елементів "І-НЕ" відповідно з'єднані з вихідними шинами і-х та і-1-х каскадів регістра зсуву, а виходи з'єднані з четвертими входами групи логічних елементів "І", виходи яких в кожному каналі підключені до входів накопичуючих суматорів [Патент на корисну модель № 73320 Україна МПК G067 17/15. Багатоканальний цифровий корелятор /Я.М. Николайчук, І.Б. Албанський// Опубл. 25.09.2012, Бюл. № 18]. Недоліком багатоканального цифрового корелятора є низька швидкодія та обмежені функціональні можливості обумовлені тим, що пристрій містить багато розрядні у кожному каналі накопичуючі суматори, які працюють у двійковій системі числення теоретико-числового базису Радемахера. І характеризуються низькою швидкодією у зв'язку з наявністю наскрізних переносів між розрядами двійкового суматора. При цьому типова тривалість затримки сигналів в одному розряді повного тривходового суматора в складі 5-ти мікротактів див. [Повнофункціональна побітова потокова арифметика зі зменшеними витратами обладнання: монографія / О.Д. Азаров, 0.1. Черняк.- Вінниця: ВНТУ, 2013. с 134. рис. 4.4]. У багатоканальному цифровому кореляторі з розрядністю вхідних кодів 8 біт і об'ємом вибірки 256 значень розрядність суматорів у кожному каналі буде складати 24 біт, у процесі сумування 16ти бітних зсунутих в сторону старших розрядів вхідних кодів 8 біт в результатів їх сумувань вхідних кодів, що складає 100 мікротактів на один цикл роботи АЦП. В основу побудови пристрою поставлена задача вдосконалення корелятора шляхом підвищення швидкодії та розширення функціональних можливостей, який містить синхронізатор, (n+1)-каскадний регістр зсуву, n накопичувачів, виходи яких є виходами пристрою, перетворювач "аналог-код" послідовного наближення, перший вхід якого є входом пристрою, другий вхід підключений до першого виходу синхронізатора, а вихід підключений до першого входу регістра, другий вхід якого підключений до другого виходу синхронізатора, комутаційний регістр зсуву, перший вхід якого з'єднаний з першим виходом синхронізатора, другий вхід з'єднаний з другим виходом синхронізатора, а вихідна шина з'єднана з відповідними блоками і підключена в кожному каналі до відповідних перших входів групи логічних елементів "І", другі і треті входи яких з'єднані з відповідними шинами і-х та і-1-х каскадів багатокаскадного регістра зсуву, група логічних елементів "І-НЕ", перші входи яких відповідно з'єднані з вихідною шиною 2k-1-го розряду регістра зсуву, другі і треті входи групи логічних елементів "І-НЕ" відповідно з'єднані з вихідними шинами і-х та і-1-х каскадів регістра зсуву, а виходи з'єднані з четвертими входами групи логічних елементів "І", які відрізняються тим, що виходи логічних елементів І в кожному каналі підключені до входів додатково введених синхронних накопичуючих лічильників теоретико-числового базису Галуа, виходи яких підключені до входів 1 UA 116116 C2 5 10 15 20 25 30 35 додатково введених дешифраторів виходи яких є виходами пристрою. Багатоканальний цифровий корелятор ілюструється кресленням на фіг. 1 та фіг. 2 показана структурна та функціональна схема реалізації пристрою при k=4, тобто чотирирозрядному перетворювачі "аналог-код" послідовного наближення, що відповідає 16-рівневому діапазоні квантування вхідних аналогових сигналів x(t), на фіг. 3 показана структура лічильника теоретико-числового базису Галуа. Кодові послідовності лічильника Галуа формуються на основі ключів незвідних поліномів [див. Теорія джерел інформації. /Я.М. Николайчук// - Тернопіль:ТНЕУ 2008 р. - С. 239, Табл. 7.1]. Матричні дешифратори реалізуються по типовій схемі див. [Теоретичні засади та принципи побудови арифметико-логічного пристрою на основі вертикально-інформаційної технології /Я.М. Николайчук, ОМ. Заставний, П. В. Гуменный// Вісник Хмельницького національного технічного університету. - 2012. - № 2. - рис. 7в]. Багатоканальний цифровий корелятор включає в себе: 1-1m+1 - багатокаскадний регістр зсуву, 2 - синхронізатор, 3 - перетворювач "аналог-код", 4 - вхід пристрою, 5 - лічильники ТЧБ Галуа, 6 - комутаційний регістр зсуву, 7 - група логічних елементів "І", 8 - група логічних елементів "І-НЕ". 9 - дешифратори. На фіг. 2 показана структурна схема реалізації пристрою при к=4, яка демонструє інформаційні з'єднання інформаційних шин між компонентами пристрою. Пристрій працює наступним чином. Процес обчислення значень коваріаційної функції починається з m циклів запису вхідних біторієнтованих кодів перетворювача "аналог код" послідовного наближення 3 в багатокаскадний регістр зсуву 1. В наступних n циклах роботи пристрою у процесі зсуву інформації у багатокаскадному регістрі зсуву 1 та комутації вихідних інформаційних шин в комутаційному регістрі 6, в кожному каналі групою логічних елементів 7 та в першому каналі групою логічних елементів 8 в кожному каналі виконується сумування добутків x ixi-j, які формуються сумуванням зсунутих кодів xi-j регістра зсуву 1 та їх записом у суматор 5 під управлінням бітів x iго коду, які вибираються з 1-го та 3-го розрядів першого та 1-го та 3-го розрядів другого каскаду регістра зсуву. Таким чином, процеси формування бітів на виході перетворювача "аналог-код", зсув інформації в багатокаскадному регістрі зсуву 1, формування добутків x ixi-j відбувається синхронно з формуванням бітів вихідних кодів перетворювача "аналог-код" 3, починаючи зі старших розрядів. Після кожного з наступних n циклів роботи пристрою на виходах лічильників Галуа 5 та дешифраторів 90-9m формуються та зчитуються коди коаваріаційної функції. Число вимірювань, необхідних для отримання коваріаційної функції, вибирається кратним цілим степеням числа 2, виходячи з умов простої реалізації операцій ділення в дешифраторах, шляхом відкидання певного числа молодших розрядів отриманих кодів. За рахунок обчислення коваріаційної функції вдосконаленим багатоканальним цифровим корелятором підвищується його швидкодія відносно прототипу, оскільки операції сумування у кожному каналі виконується синхронними лічильниками ТЧБ Галуа реалізованих на D-тригерах за 2 мікротакти та реалізацією цих кодів у двійкові у матричних дешифраторах за 3 мікротакти. Таким чином при вказаній розрядності вхідних кодів 8 біт, об'ємі вибірки 256 біт швидкодія багатоканального цифрового корелятора зростає у 100/5=20 разів. 40 ФОРМУЛА ВИНАХОДУ 45 50 55 Багатоканальний цифровий корелятор, який містить синхронізатор, (n+1)-каскадний регістр зсуву, n накопичувачів, виходи яких є виходами пристрою, перетворювач "аналог-код" послідовного наближення, перший вхід якого є входом пристрою, другий вхід підключений до першого виходу синхронізатора, а вихід підключений до першого входу регістра, другий вхід якого підключений до другого виходу синхронізатора, комутаційний регістр зсуву, перший вхід якого з'єднаний з першим виходом синхронізатора, другий вхід з'єднаний з другим виходом синхронізатора, а вихідна шина з'єднана з відповідними блоками і підключена в кожному каналі до відповідних перших входів групи логічних елементів "І", другі і треті входи яких з'єднані з відповідними шинами і-х та і-1-х каскадів багатокаскадного регістра зсуву, група логічних елементів "І-НІ", перші входи яких відповідно з'єднані з вихідною шиною 2k-1-го розряду регістра зсуву, другі і треті входи групи логічних елементів "І-НІ" відповідно з'єднані з вихідними шинами і-х та і-1-х каскадів регістра зсуву, а виходи з'єднані з четвертими входами групи логічних елементів "І", який відрізняється тим, що виходи логічних елементів І в кожному каналі підключені до входів додатково введених синхронних накопичуючих лічильників теоретико-числового базису Галуа, виходи яких підключені до входів додатково введених дешифраторів, виходи яких є виходами пристрою. 2 UA 116116 C2 3 UA 116116 C2 Комп’ютерна верстка О. Рябко Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюNykolaichuk Yaroslav Mykolaiovych, Albanskyi Ivan Bohdanovych

Автори російськоюНиколайчук Ярослав Николаевич, Албанский Иван Богданович

МПК / Мітки

МПК: G06F 17/15, G06F 17/00

Мітки: корелятор, цифровий, багатоканальний

Код посилання

<a href="https://ua.patents.su/6-116116-bagatokanalnijj-cifrovijj-korelyator.html" target="_blank" rel="follow" title="База патентів України">Багатоканальний цифровий корелятор</a>

Попередній патент: Гідропіроліз біомаси для отримання високоякісних рідких палив

Наступний патент: Потрійні фунгіцидні суміші

Випадковий патент: Спосіб визначення внутрішніх дефектів у стінах приміщень