Корелятор

Номер патенту: 36644

Опубліковано: 15.05.2003

Автори: Гудима Олег Ярославович, Дурняк Богдан Васильович, Войтович Анатолій Михайлович, Никифорук Богдан Васильович, Тимченко Олександр Володимирович

Формула / Реферат

1. Корелятор, який містить М-каскадний регістр зсуву, де Μ - довжина кореляційної функції, вхід якого є входом пристрою, Μ обчислювальних блоків (![]() ,0),

,0), ![]() , перший інформаційний вхід (

, перший інформаційний вхід (![]() ,0)-го обчислювального блока підключений до (М-1-

,0)-го обчислювального блока підключений до (М-1-![]() )-го виходу регістра зсуву, вихід (

)-го виходу регістра зсуву, вихід (![]() ,0)-го обчислювального блока є відповідним виходом корелятора, блок

,0)-го обчислювального блока є відповідним виходом корелятора, блок ![]() синхронізації, вихід скидання, перший та другий тактові виходи якого об'єднані відповідно з входом скидання та тактовим входом регістра зсуву та з однойменними входами обчислювальних блоків, кожний з яких містить перемножувач, суматор, перший та другий буферні регістри, вихід останнього є виходом обчислювального блока, першим та другим інформаційними входами якого є перші та другі входи перемножувача, вихід якого з'єднаний з першим входом суматора, вихід якого з'єднаний з інформаційними входами другого та першого буферних регістрів, тактовий вхід останнього є першим тактовим входом обчислювального блока, другим тактовим входом якого є тактовий вхід другого буферного регістра, об'єднаний з першим входом скидання першого буферного регістра, другий вхід скидання якого об'єднаний зі входом скидання другого буферного регістра і є входом скидання обчислювального блока, який відрізняється тим, що додатково введені Μ перемножувачів та

синхронізації, вихід скидання, перший та другий тактові виходи якого об'єднані відповідно з входом скидання та тактовим входом регістра зсуву та з однойменними входами обчислювальних блоків, кожний з яких містить перемножувач, суматор, перший та другий буферні регістри, вихід останнього є виходом обчислювального блока, першим та другим інформаційними входами якого є перші та другі входи перемножувача, вихід якого з'єднаний з першим входом суматора, вихід якого з'єднаний з інформаційними входами другого та першого буферних регістрів, тактовий вхід останнього є першим тактовим входом обчислювального блока, другим тактовим входом якого є тактовий вхід другого буферного регістра, об'єднаний з першим входом скидання першого буферного регістра, другий вхід скидання якого об'єднаний зі входом скидання другого буферного регістра і є входом скидання обчислювального блока, який відрізняється тим, що додатково введені Μ перемножувачів та ![]() -ий обчислювальний блок (

-ий обчислювальний блок (![]() ,

,![]() ),

), ![]() , 0 <

, 0 < ![]() £

£ ![]() , перші входи перемножувачів об'єднані та підключені до (М-1)-го виходу регістра зсуву, другий вхід

, перші входи перемножувачів об'єднані та підключені до (М-1)-го виходу регістра зсуву, другий вхід ![]() -го перемножувача об'єднаний з першими інформаційними входами всіх (

-го перемножувача об'єднаний з першими інформаційними входами всіх (![]() ,

, ![]() )-их обчислювальних блоків,

)-их обчислювальних блоків, ![]() £

£ ![]() ,

, ![]() , другі інформаційні входи (

, другі інформаційні входи (![]() ,

, ![]() )-их,

)-их, ![]() обчислювальних блоків об'єднані та підключені до виходу

обчислювальних блоків об'єднані та підключені до виходу ![]() -го перемножувача, виходи (

-го перемножувача, виходи (![]() ,

,![]() ),

),![]() £

£ ![]()

![]() , обчислювальних блоків є відповідними виходами корелятора.

, обчислювальних блоків є відповідними виходами корелятора.

2. Корелятор за. п.1, який відрізняється тим, що блок синхронізації містить формувач встановлення в початковий стан пристрою при вмиканні напруги живлення, генератор тактових імпульсів, лічильник-подільник частоти, тригер з лічильним входом, елемент І, елемент затримки, вихід якого з'єднаний з лічильним входом тригера, прямий вихід якого і вихід генератора тактових імпульсів з'єднані з входами елемента І, вихід якого з'єднаний з лічильним входом лічильника-подільника, вхід встановлення в нульовий стан якого об'єднаний з одноіменним входом тригера, входом елемента затримки та підключений до виходу формувача встановлення в початковий стан, інверсний вихід тригера є виходом скидання блока синхронізації, першим та другим тактовими виходами якого є відповідно вихід елемента І та вихід лічильника-подільника.

Текст

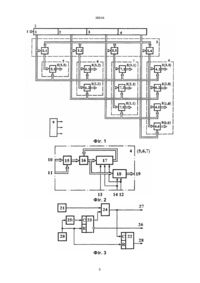

1. Корелятор, який містить М-каскадний регістр зсуву, де М - довжина кореляційної функції, вхід якого є входом пристрою, М обчислювальних 36644 сигналів системи, що досліджується, у зв'язку з цим відомий пристрій вирішує вузький клас задач. Найближчим по технічній суті до рішення, що заявляється, є корелятор паралельної дії, що містить М-каскадний регістр, де М - число ординат кореляційної функції (довжина кореляційної функції), першу груп у з М арифметичних блоків, кожний з яких складається з перемножувача і накопичувача, блок синхронізації [2]. Відомий пристрій містить М-каскадний регістр зсуву, де М - довжина кореляційної функції, вхід якого є входом пристрою, М обчислювальних бло підключений до други х входів з першого по і-й арифметичних блоків і-ї групи, виходи арифметичних блоків (М-1)-их гр уп є відповідними виходами ординат кореляційної функції корелятора. Існує тісний причинно-наслідковий зв'язок між усією сукупністю суттєвих ознак та очікуваним технічним результатом. Так, за рахунок включення у відомий пристрій групи з М блоків перемноження та (М-1)-ої гр упи арифметичних блоків по і блоків в кожній, де i = 1, M - 1 з відповідними зв'язками в заявленому пристрої реалізується обчислення послідовності значень кумулянтів третього порядку в реальному масштабі часу: в такті надходження вхідних відліків без накопичування затримки. Це здійснюється шляхом додаткової обробки вхідних відліків і накопичення результатів цієї обробки у відповідних обчислювальних блоках. Тому включення в схему відомого пристрою зазначених блоків дозволяє досягнути заявлюваного технічного результату, тобто розширити клас задач, які вирішуються, за рахунок обчислення значень кумулянтів третього порядку, що дозволяє, наприклад, проводити ідентифікацію немінімальнофазових систем лише за наявності вихідного сигналу системи, оскільки кумулянти третього порядку на відміну від кумулянтів другого порядку є статистиками, чутливими до фази вихідного сигналу. Причому, за допомогою кумулянтів третього порядку можна визначити модуль і фазу передавальної функції системи, виключивши неоднозначність масштабу і часової затримки. Введені до складу корелятора блоки відомі і широко застосовуються. Однак, лише їхнє введення з відповідними зв'язками дозволяє виявити в ньому нові властивості і сприяє отриманню передбаченого технічного результату. Суть винаходу полягає в тому, що корелятор містить М-каскадний регістр зсуву, де М - довжина кореляційної функції, вхід якого е входом пристрою, М обчислювальних блоків (і,0), ків (і,0), i = 0, M - 1 , перший інформаційний вхід (і,0)-го обчислювального блока підключений до (М1-і)-го виходу регістра зсуву, вихід (і,0)-го обчислювального блока є відповідним виходом корелятора, блок синхронізації, вихід скидання, перший та другий тактові виходи якого об'єднані відповідно з входом скидання та тактовим входом регістра зсуву та з однойменними входами обчислювальних блоків, кожний з яких містить перемножувач, суматор, перший та другий буферні регістри, вихід останнього є виходом обчислювального блока, першим та другим інформаційними входами якого являються перші та другі входи перемножувача, вихід якого з'єднаний з інформаційними входами другого та першого буферних регістрів, тактовий вхід останнього є першим тактовим входом обчислювального блока, другим тактовим входом якого є тактовий вхід другого буферного регістра, об'єднаний з першим входом скидання першого буферного регістра, другий вхід скидання якого об'єднаний зі входом скидання другого буферного регістра і е входом скидання обчислювального блока. Пристрій-прототип, як і аналогічні, здійснює обчислення кореляційної функції вхідних сигналів, тобто кумулянтів другого порядку. Однак, розширити клас задач, що вирішуються, шляхом обчислення кумулянтів третього порядку в відомому пристрої неможливо. В основу винаходу поставлено завдання удосконалення корелятора шляхом конструктивного забезпечення обчислення кумулянтів третього порядку в режимі реального часу, що дозволяє підвищити інформативність, завдяки розширенню класів задач, які вирішуються. Поставлене завдання вирішується тим, що у відомий пристрій, який містить М-каскадний регістр зсуву, вхід якого є входом корелятора, першу групу арифметичних блоків, перші інформаційні входи яких підключені відповідно до виходів однойменних розрядів регістра зсуву, а ви ходи є відповідними виходами ординат кореляційної функції корелятора, введені група з М блоків перемноження, (М-1)-а гр упа арифметичних блоків по і блоків в = 0, M - 1 , перший інформаційний вхід (і,0)-го i обчислювального блока підключений до (М-1-і)-го виходу регістра зсуву, вихід (і,0)-го обчислювального блока є відповідним виходом корелятора, блок синхронізації, вихід скидання, перший та другий тактові виходи якого об'єднані відповідно з входом скидання та тактовим входом регістра зсуву та з однойменними входами обчислювальних блоків, кожний з яких містить перемножувач, суматор, перший та другий буферні регістри, вихід останнього є виходом обчислювального блока, першим та другим інформаційними входами якого являються перші та другі входи перемножувача, вихід якого з'єднаний з інформаційними входами другого та першого буферних регістрів, тактовий вхід останнього є першим тактовим входом обчислювального блока, другим тактовим входом якого є тактовий вхід другого буферного регістра, об'єднаний з першим входом скидання першого буферного регістра, другий вхід скидання якого об'єднаний зі входом скидання другого буферного регістра і є входом скидання обчислювального блоку, а також, згідно винаходу М перемножувачів та кожному, де i = 1, M - 1 , та блок синхронізації, виходи якого з'єднані з синхровходами арифметичних блоків, і-й розрядний вихід регістра зсуву з'єднаний з першими виходами і-их арифметичних блоків (М-1)-их груп, вихід М-го розряду регістра зсуву підключений до перших входів блоків перемножувача групи, другі входи яких з'єднані з виходами однойменних розрядів регістра, зсуву, ви хід М-го блока, перемноження групи підключений до други х входів з першого по М-й арифметичні блоки першої групи, вихід і-го блока перемноження групи M ( M - 1) -ий 2 2 обчислювальний блок (k, j), 36644 ремножувачів і підключені до одноіменних розрядів регістра 2 зсуву. Другі входи перемножувачів k = 1, M - 1 , 0 < j £ k , перші входи перемножувачів об'єднані та підключені до (М-1)-го ви ходу регістра зсуву, др угий вхід і-го перемножувача об'єднаний з першими інформаційними входами всіх (i , j)-их обчислювальних блоків, j £ i , j = 0, M - 1 , 3.к, k = 1, M групи 3 об'єднані і підключені до виходу М-го розряду регістра, 2 зсуву, і-й розрядний вихід якого, i = 1, M з'єднаний з першими входами і-их арифметичних блоків 5.і, 6.і, 7.і, і т.д.(М-1)-и х гр уп 5, 6, 7 і т.д., вихід блока 3.М перемноження групи 3 підключений до других входів арифметичних блоків 4.1...4.М гр упи 4, вихід блока другі інформаційні входи (i, j)-их, j = i , M - 1 обчислювальних блоків об'єднані та підключені до виходу і-го пермножувача, виходи (k, j), j £ k , обчислювальних блоків являються відповідними виходами корелятора. Блок синхронізації містить формувач встановлення в початковий стан пристрою при вмиканні напруги живлення, генератор тактових імпульсів, лічильник-подільник частоти, тригер з лічильним входом, елемент І, елемент затримки, вихід якого з'єднаний з лічильним входом тригера, прямий вихід якого і вихід генератора тактових імпульсів з'єднані з входами елемента І, вихід якого з'єднаний з лічильним входом лічильника-подільника, вхід встановлення в нульовий стан якого об'єднаний з одноіменним входом тригера, входом елемента затримки та підключений до виходу формувача встановлення в початковий стан, інверсний вихід тригера є виходом скидання блока синхронізації, першим та другим тактовими виходами якого є ви хід елемента І та вихід лічильника-подільника. На фіг. 1 наведена структурна схема корелятора; на фіг. 2 - структурна схема арифметичного блока, на фіг. 3 - структурна схема блока синхронізації. На фіг. 4 представлені часові діаграми роботи пристрою. Корелятор містить вхід 1, М-каскадний регістр 2 зсуву, де М -довжина кореляційної функції, групу 3 із М блоків перемноження 3.1... 3. М, першу гр упу 4 із М арифметичних блоків 4.1...4. М, (М-1)-у гр упу і-их арифметичних блоків 5, 6, 7 (на фіг.1 М=4) по і перемноження 3.і, i = 1, M - 1 групи 3 підключений до других входів з першого по і-й арифметичних блоків (М-1)-их гр уп 5, 6, 7 і т.д. відповідно. Виходи блока 9 синхронізації з'єднані з синхровходами арифметичних блоків груп 4, 5, 6, 7, виходи яких є виходами 8 корелятора. В кожному арифметичному блоці 4.і (5.і, 6.і, 7.і) першими і другими інформаційними входами 10 і 11 є перші і другі входи перемножувача 15, вихід якого з'єднаний з першим входом суматора 16, вихід якого з'єднаний з інформаційним входом першого 17 і другого 18 буферних регістрів, ви хід останнього є виходом 19 арифметичного блока. Перший вхід скидання першого 17 і вхід скидання другого 18 буферних регістрів об'єднані і є входом 12 скидання блока., першим тактовим входом 13 блока є тактовий вхід першого буферного регістра 17, вихід якого з'єднаний з другим входом суматора 16, другий вхід скидання першого буферного регістра 17 об'єднаний з тактовим входом другого буферного регістра 18 і є другим тактовим входом 14 арифметичного блока. В блоці 9 синхронізації вихід формувача 20 початкового встановлення з'єднаний з входом елемента 24 затримки і входами встановлення в нульовий стан тригера 23 і лічильника-подільника 22, лічильний вхід якого підключений до виходу елемента 24 І, перший вхід якого підключений до виходу генератора 21 тактових імпульсів, другий вхід елемента 24 І підключений до прямого виходу тригера 28, інверсний вихід якого є виходом 26 скидання блока 9, вихід елемента 25 затримки з'єднаний з тактовим входом тригера 23, вихід елемента 24 І і вихід лічильника-подільника 22 є першим 27 і другим 28 тактовими виходами блока 9 синхронізації. Корелятор працює наступним чином. Після підключення напруги живлення в блоці 9 синхронізації формувач 20 генерує імпульс (фіг. 4а), тривалість t1, якого більша або рівна тривалості перехідних процесів в пристрої. Цей імпульс встановлює тригер 23 і лічильник-подільник 22 в нульовий стан. Імпульс (фіг. 4б) з виходу тригера 23 встановлює всі виходи регістра 2 затримки і всі виходи буферних регістрів 16 і 18 арифметичних блоків 4 в н ульовий стан (кола скидання і синхронізації на фіг. 1 не показані). Після закінчення імпульсу (фіг. 4а) формувача 20 по задньому фронту цього імпульсу тригер 23 через час, що визначається часом затримки t3 в елементі 25, встановлюється в одиничний стан і сигнал з його прямого виходу дозволяє проходження імпульсів генератора 21 (фіг. 4в) на перший тактовий вихід 27 блока. 9 синхронізації (фіг. 4г). блоків 5.і, 6.і, 7.і в кожній, де i = 1, M - 1 , виходи 8 арифметичних блоків 4.1, 5.і, 6.і, 7.і, блок 9 синхронізації. Кожний обчислювальний блок 4-і (5.і, 6.і, 7.і), містить перший 10 і другий 11 інформаційні входи, входи 12 скидання, перший і другий тактові входи 13 і 14, перемножувач 15, суматор 16 і перший буферний регістр 17, що утворюють накопичувач, другий буферний регістр 18 (що є пам'яттю кореляційної функції) і вихід 19 арифметичного блока. Блок 9 синхронізації містить формувач 20 початкового встановлення пристрою при включенні напруги живлення, генератор 21 тактових імпульсів, лічильник-подільник 22 частоти, тригер 23 з лічильним входом, елемент 24 І, елемент 25 затримки, вихід 26 скидання, перший 27 і другий 28 тактові виходи блока 9 синхронізації. На фіг. 4 показані наступні сигнали: а - імпульс на виході формувача 20 початкового встановлення пристрою; б - імпульс на виході тригера 23; в імпульси тактового генератора 21; г - імпульси на виході елемента 24 І; д - імпульс на виході лічильника-подільника 22. Інформаційний вхід М-каскадний регістра 2 зсуву є входом 1 корелятора, перші інформаційні входи арифметичних блоків 4.к, к=1,М першої групи 4 об'єднані з відповідними входами групи 3 пе 3 36644 В кінці інтервалу реалізації Q за імпульсом (фіг. 4д) з другого тактового входу 14 значення сигналу з виходу суматора 16 записується в другий буферний регістр 18, а перший буферний регістр 17 скидається в нульовий стан. Частота повторення імпульсів генератора 21 відповідає частоті дискретизації вхідного сигналу T1, а час t3 0 записуються і зсуваються в регістрі 2 зсуву, В (n+М)-му інтервалі дискретизації, n>0 Тому на виходах 8(I,j), i = 0, M - 1 , j0. На перші інформаційні входи арифметичних блоків 4.і, i = 1, M - 1 першої групи, на перші інформаційні входи арифметичних блоків 5.і, 6.і, 7.і та т.д. (М-1)-ої гр упи арифметичних блоків надходять відліки {хn+M-i} вхідного сигналу з і-го виходу регістра 2 зсуву. На др угі інформаційні входи арифметичних блоків 4.і надходять значення добутків {хn хn} з виходу М-го блока перемноження 3.М. Аналогічно, на другі інформаційні входи арифметичних блоків 5.і, 6.і, 7.і і т. д. надходять значення добутків {xn xn+M-i}, {xn xn+M-2}. {xn xn+M-3} та т. д. відповідно з виходу j-го блока перемноження 3.j групи. В обчислювальних блоках 4.і (5.і, 6.і, 7.і і т. д.) значення сигналів {xn+M-i} та {xn xn+M-j} надходять з інформаційних входів 10 і 11 на входи перемножувача 15, на виході якого формується послідовність добутків {xn xn+M-ixn+M-j}, що надходять на перший вхід суматора 16. На другий вхід суматора 16 з виходу першого регістра 17 надходить значення сигналу суматора 16 в попередньому (n+М-2)-му періоді дискретизації вхідного сигналу. З врахуванням нульових початкових значень регістра 2 зсуву та буферного регістра 17 в (n+М-1)-му періоді дискретизації накопичене значення дорівнює: i = 0, M - 1 , перемножувача 15 та операції підсумовування tsm, суматором 16. Він може бути визначений з виразу T > 2t m + t sm . Ця величина може бути зменшена Tmin = max (t m t sm ) до при відповідній буферизації блоків перемноження 3.к, k = 1, M та перемножувачів 15 за допомогою буферних регістрів. Таким чином, в пристрої здійснюється обчислення послідовності кумулянтів третього порядку в режимі реального часу, що дозволило досягнути поставленої мети - розширити клас задач, які вирішуються. Це дозволяє, наприклад, здійснювати ідентифікацію систем тільки по вихідному сигналу системи, оскільки кумулянти є функціями не тільки амплітуди, але і фази сигналу. Джерела інформації. 1. Jones D. An on-board digital correlation for spacecraft VLF radio wave studies. - IEEE Trans. Geosci. Electron., 1974, V.12, № 1, p.l2, fig.3. 2. Грибанов Ю.И. и др. Автоматические цифровые корреляторы. - М. Энергия, 1971. - С. 150, рис. 4. 6. n K ( M -i, M - j ) = å xm x m+ M -i x m+ M - j m =0 Це значення за імпульсами (фіг.4г) на першому тактовому вході 13 блоків 4.і (5.і, 6.і, 7.і та т. д.) записується в регістр 17. 4 36644 Фіг. 1 Фіг. 2 Фіг. 3 5 36644 Фіг. 4 __________________________________________________________ ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2001 р. Формат 60х84 1/8. Обсяг ______ обл.-вид. арк. Тираж 50 прим. Зам._______ ____________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 ___________________________________________________________ 6

ДивитисяДодаткова інформація

Назва патенту англійськоюCorrelator

Автори англійськоюVoitovych Anatolii Mykhailovych, Nykyforuk Bohdan Vasyliovych, Tymchenko Oleksandr Volodymyrovych

Назва патенту російськоюКоррелятор

Автори російськоюВойтович Анатолий Михайлович, Никифорук Богдан Васильевич, Тимченко Александр Владимирович

МПК / Мітки

МПК: G06F 17/15, G06F 7/575

Мітки: корелятор

Код посилання

<a href="https://ua.patents.su/6-36644-korelyator.html" target="_blank" rel="follow" title="База патентів України">Корелятор</a>

Попередній патент: Кронен-пробка з язичком-важелем для відкривання

Наступний патент: Головний аеродинамічний обтічник космічної ракети

Випадковий патент: Спосіб визначення можливої тяжкості перебігу тропічної малярії (тм) у осіб з немалярійної зони