Цифровий корелятор

Номер патенту: 69700

Опубліковано: 15.09.2004

Автори: Корніловська Наталя Володимирівна, Рогальський Франц Борисович, Боярчук Василь Петрович, Головащенко Наталя Вікторівна

Формула / Реферат

Цифровий корелятор, що містить перший n-розрядний регістр зрушення, другий n-розрядний регістр зрушення, входи першого і другого n-розрядних регістрів зрушення є однойменними входами корелятора, інформаційні входи яких є однойменними входами першого і другого n-розрядних регістрів зрушення, який відрізняється тим, що у нього введені сумарно-різницевий підсилювач та n-блоків порівнянь, які складаються з n елементів по модулю 2 і n інверторів, розрядні виходи першого і другого n-розрядних регістрів зрушення з'єднані з відповідними інформаційними входами елементів по модулю 2, виходи яких з'єднані з входами інверторів та різницевим входом сумарно-різницевого підсилювача, інформаційні виходи інверторів з'єднані з підсумовуючим входом сумарно-різницевого підсилювача.

Текст

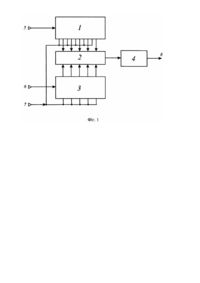

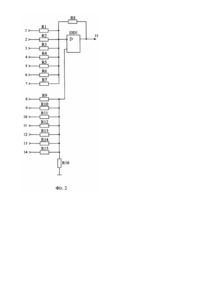

Винахід відноситься до галузі радіотехніки та автоматики, зокрема, до автоматичних систем управління і може використовуватися для синтезу кореляційної функції. Відомо, що існує спеціалізований обчислювальний пристій (Балл Г.А. Аппаратурный корреляционный анализ случайных процессов. М. "Энергия" 1968г., стр. 126), який синтезує кореляційну функцію. Він є пристроєм, який складається з фільтрів, потенціометрів, суматорів та перемножувача. Найбільш близьким технічним рішенням, який прийнято за прототип, являється цифровий корелятор (А. С. SU 1282158 А1), що містить перший n-розрядний регістр зрушення, n блоків множення, n суматорів, перемикач вибору режиму роботи, другий n-розрядний регістр зрушення, n фіксаторів зрушення, кожний з яких містить RS-тригер, елемент И та перемикач, n блоків розподілу, n лічильників, елемент затримки й елемент диференціювання. Тактовий вхід першого n-розрядного регістра зрушення є однойменним входом корелятора, інформаційний вхід якого є однойменним входом першого n-розрядного регістра зрушення, розрядні виходи якого з'єднані з першими входами відповідних блоків множення, виходи яких з'єднані з інформаційними входами відповідних суматорів. Тактовий вхід друго го n-розрядного регістра зрушення з'єднаний з тактовим входом першого n-розрядного регістра зрушення, інформаційний вхід другого nрозрядного регістра зрушення з'єднаний з першим входом елемента И кожного фіксатора зрушення і є входом стробування корелятора. Вихід кожного розряду другого n-розрядного регістра зрушення з'єднаний відповідно з другим входом елемента И відповідного фіксатора зрушення, вихід молодшого розряду другого n-розрядного регістра зрушення з'єднаний із третім входом елемента И кожного фіксатора зрушення. Вхід початкової установки RS-тригера кожного фіксатора зрушення з'єднаний із входами початкової установки обох n-розрядних регістрів зрушення і підключений до виходу елемента диференціювання. Вихід старшого розряду другого n-розрядного регістра зрушення з'єднаний із входом перемикача вибору режиму роботи, вихід якого через елемент затримки з'єднаний із входом елемента диференціювання. Вихід молодшого розряду першого n-розрядного регістра зрушення з'єднаний із другим входом усі х блоків множення. Виходи суматорів з'єднані з першими інформаційними входами відповідних блоків розподілу, ви хід елемента И усіх фіксаторів зрушення з'єднаний із входом перемикача і підключений до входів дозволу підсумовування відповідних суматорів і до рахункових входів відповідних лічильників, інверсні виходи переносу яких з'єднані з четвертим входом елемента И відповідних фіксаторів зрушення. Інформаційні виходи лічильників з'єднані з другими інформаційними входами блоків розподілу, виходи яких і інформаційні виходи лічильників є виходами значень відповідних ординат кореляційної функції корелятора. У кожному фіксаторі зрушення вихід перемикача з'єднаний з S-входом RS-тригера, інверсний вихід якого з'єднаний з п'ятим входом елемента И. Проте схема приведеного корелятора досить велика за апаратурним складом і вимагає використання великих обчислювальних потужностей, що є значним недоліком. В основу цього винаходу положено задача створення цифрового корелятора, схема виконання якого забезпечила б синтез кореляційної функції з невеликими апаратурними витратами та використанням невеликих обчислювальних потужностей. Це досягається тим, що в цифровий корелятор, який містить перший n-розрядний регістр зрушення, другий n-розрядний регістр зрушення, входи першого і другого n-розрядних регістрів зрушення є однойменними входами корелятора, інформаційні входи яких є однойменними входами першого і другого n-розрядних регістрів зрушення, введені сумарно-різницевий підсилювач та n-блоків порівнянь, які складаються з n елементів по модулю 2 і n інверторів, розрядні виходи першого і другого n-розрядних регістрів зрушення з'єднані з відповідними інформаційними входами елементів по модулю 2, виходи яких з'єднані з входами інверторів та різницевим входом сумарно-різницевого підсилювача, інформаційні виходи інверторів з'єднані з підсумовуючим входом сумарно-різницевого підсилювача. На відміну від прототипу, в якому для перетворення в напругу суму збігів і розбіжностей кодових знаків необхідно використовувати додатково цифро-аналоговий перетворювач, згідно винаходу в якості введеного суматора кількості збігів і розбіжностей використовується сумарно-різницевий підсилювач. Він забезпечує дві функції: цифрову - підсумовування кількості збігів та розбіжностей, та аналогову перетворювання цієї кількості у напругу-форму, зручн у для індикації кінцевого результату, що цілком зменшує апаратурні витрати. На фіг.1 представлена структурна схема цифрового корелятора; на фіг.2 - електрична функціональна схема сумарно-різницевого підсилювача; на фіг.3 - моделювання цифрового корелятора в ППП Electronics Workbench; на фіг.4 - результати моделювання. Цифровий корелятор (фіг.1) містить статичний регістр зрушення 1, схему порівняння 2, динамічний регістр зрушення 3, цифро-аналоговий перетворювач 4, інформаційні входи корелятора 5-6, тактовий вхід 7, вихід 8 значення кореляційної функції. Сумарно-різницевий підсилювач (фіг.2) містить ІМС DD1, резистори R1-R16, інформаційні входи 1-14, інформаційний вихід 15. Електрична принципова схема цифрового корелятора в ППП Electronics Workbench (фіг.3) містить генератор квазівипадкових послідовностей (КВП) ІМС DD1-DD3, регістр зрушення статичний ІМС DD4, регістр зрушення динамічний ІМС DD5, схему порівняння ІМС DD6-DD19, сумарно-різницевий підсилювач DA1, R2-R17, ключ S1, генератор тактових імпульсів G1, осцилограф О1, аналізатор А1, блоки живлення +5В та +15В, -15В. Результати моделювання (фіг.4) містять автокореляційну функцію (зверху), часові діаграми роботи регістрів зрушення статичного та динамічного в різних режимах роботи цифрового корелятора (нижче). Відомо, що автоматичне знаходження знакових кореляційних функцій вимагає менших апаратурних затрат, чим звичайний. Технічне спрощення під час автоматичного знаходження знакових кореляційних функцій забезпечується тим, що аналогові сигнали x(t) заміняються їх знаками, тобто виконується перетворення ì- 1 при х 0 î (1) Процес знаходження знакової кореляційної функції можна ілюструвати таким чином ° ° é ù rx (t) = Mê sgn x (t )sgn x (t - t )ú ê ú ë û (2) ° де rx(t) - знакова кореляційна функція, x(t ) - центрована функція, тобто без сталої складової, M функція осереднення. З формули (2) видно, що алгоритм функціонування корелятора складається з часових зміщень (t-t), виявлення побітових збігів та розбіжностей (знак множення) та визначення сумарного осередненого їх значення (M). Цифровий корелятор визначає міру однаковості прийнятого кодового слова з кодовим словом, що зберігається в пам'яті корелятора. Принцип дії цифрового корелятора такий. У регістрі зрушення статичному 1 весь цикл вимірів зберігається кодове слово, кореляційну функцію якого необхідно визначити. Це кодове слово надходить на вхід 5 від генератора квазівипадкових послідовностей (КВП). На вхід 6 у реальному масштабі часу надходить КВП у виді знакового сигналу, що пройшов через лінію зв'язку і схему відновлення структури КВП. На вхід 7 надходять тактові імпульси, що зрушують. С хема порівняння 2 визначає кількість порозрядних збігів і розбіжностей кодових слів, того що зберігається в регістрі зрушення статичному 1 і того що знаходиться в даний момент в регістрі зрушення динамічному 3. Цифро-аналоговий перетворювач (ЦАП) 4 перетворює переважаючу кількість збігів і розбіжностей у напругу - форму, зручну для спостерігання. У даному випадку необхідно використовувати ЦАП унітарного (одиночного) коду в напругу. У якості такого цифро-аналоговий перетворювач 4 можна використовува ти багатоканальний сумарно-різницевий підсилювач (фіг.2). Призначення приведеного на фіг.2 пристрою - визначати переважну кількість збігів і розбіжностей та перетворити її у напругу. На входи 1-7 подається інформація про кількість розбіжностей. На входи 8-14 - про кількість збігів. На виході 15 сумарно-різницевого підсилювача 4 результат алгебраїчного підсумовування. Для визначення апаратурного складу було виконане моделювання з використанням ППП Electronics Workbench (фіг.3). Принцип дії схеми такий. Ключ S1 служить для здійснення режимів запису і збереження КВП. Якщо ключ S1 замкнутий реалізується запис КВП у регістр зрушення статичний (DD4). Якщо ключ S1 розімкнутий - реалізується режим збереження КВП у регістрі зрушення статичному (DD4). Генератор тактових імпульсів G1, використовується як генератор імпульсів зрушення регістрів зрушення, осцилограф О1 - для спостереження кореляційної функції, аналізатор А1 - для спостереження тимчасових діаграм у різних крапках регістрів зрушення. Схема, зібрана на ИМС DA1 являє собою сумарно-різницевий підсилювач. Виконує функцію цифроаналогового перетворювача унітарного коду. Перетворює в напругу сум у збігів і розбіжностей кодових знаків - розрядів КВП, що знаходяться в даний момент у регістрах зрушення статичному DD4 і динамічному DD5.DD6-DD12 - суматори по модулю 2. Вони визначають факт збігу і розбіжності кодових знаків. DD13DD19 - інвертори. Суматори й інвертори включені для визначення збігів і розбіжностей. Результати моделювання приведені на фіг.4. Зверху зображена автокореляційна функція як результат алгебраїчного підсумовування кількості порозрядних збігів і розбіжностей кодових слів, того що зберігається в регістрі зрушення статичному 1 (DD4) і того що знаходиться в даний момент в регістрі зрушення динамічному 3 (DD5). Нижче показано як відбувається запис КВП у регістр зрушення статичний - ключ S1 замкнутий, та збереження КВП у регістрі зрушення статичному - ключ S1 розімкнутий. Алгоритм функціонування цифрового корелятора цілком відповідає алгоритмові, опис якого приведено раніш. Апаратурні витрати при цьому досить невеликі. Розроблений цифровий корелятор можна використовувати в обчислювальної техніці для синтезу кореляційної функції, бо в порівнянні з існуючими пристроями, він має невеликі апаратурні витрати та потребує використання невеликих обчислювальних потужностей, що обумовлює його промислове застосування.

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital correlator

Автори англійськоюRohalskyi Frants Borysovych, Holovaschenko Natalia Viktorivna

Назва патенту російськоюЦифровой коррелятор

Автори російськоюРогальский Франц Борисович, Головащенко Наталья Викторовна

МПК / Мітки

МПК: G06F 17/15

Код посилання

<a href="https://ua.patents.su/6-69700-cifrovijj-korelyator.html" target="_blank" rel="follow" title="База патентів України">Цифровий корелятор</a>

Попередній патент: Спосіб зміцнення різального інструмента

Наступний патент: Спосіб уловлювання високодисперсної краплинної рідини з газорідинного потоку і пристрій для його здійснення

Випадковий патент: Інсектицидний засіб