Пристрій для аналого-цифрового перетворення

Номер патенту: 120126

Опубліковано: 25.10.2017

Автори: Бортник Олександр Геннадійович, Васильківський Микола Володимирович, Бортник Геннадій Григорович

Формула / Реферат

Пристрій для аналого-цифрового перетворення, який містить блок вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, малорозрядний АЦП, тактовий вхід якого під'єднано до тактової шини пристрою, ЦАП, входи якого під'єднані до відповідних виходів малорозрядного АЦП, різницевий підсилювач, другий вхід якого під'єднано до виходу блока вибірки та зберігання, а перший вхід до виходу ЦАП, шину молодших розрядів та шину старших розрядів пристрою, який відрізняється тим, що введено двійковий лічильник, лічильний вхід якого під'єднано до тактової шини пристрою, перший постійний запам'ятовуючий пристрій, адресні входи, якого під'єднані до відповідних виходів двійкового лічильника, перший цифровий суматор, перші входи якого з'єднані з виходами першого постійного запам'ятовуючого пристрою, аналоговий комутатор, перший вхід якого під'єднано до виходу блока вибірки та зберігання, а другий вхід під'єднано до виходу різницевого підсилювача, вихід аналогового комутатора під'єднано до аналогового входу малорозрядного АЦП, а керувальний вхід під'єднано до шини керування пристрою, другий цифровий суматор, другий постійний запам'ятовуючий пристрій, адресні входи якого з'єднано з виходами малорозрядного АЦП, з другими входами другого цифрового суматора та з другими входами першого цифрового суматора, інформаційні входи другого постійного запам'ятовуючого пристрою під'єднано до виходів першого цифрового суматора, а виходи другого постійного запам'ятовуючого пристрою з'єднано з першими входами другого цифрового суматора, інвертор, крім того пристрій містить перший та другий буферні регістри, причому виходи другого цифрового суматора з'єднано з входами першого та другого буферних регістрів, виходи першого буферного регістра під'єднано до шини старших розрядів пристрою, виходи другого буферного регістра під'єднано до шини молодших розрядів пристрою, вхід інвертора з'єднано з шиною керування пристрою та керувальним входом першого буферного регістра, а вихід інвертора з'єднано з керувальним входом другого буферного регістра.

Текст

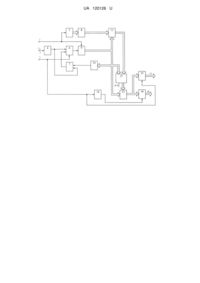

Реферат: Пристрій для аналого-цифрового перетворення, який містить блок вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, малорозрядний АЦП, тактовий вхід якого під'єднано до тактової шини пристрою, ЦАП, входи якого під'єднані до відповідних виходів малорозрядного АЦП, різницевий підсилювач, другий вхід якого під'єднано до виходу блока вибірки та зберігання, а перший вхід до виходу ЦАП, шину молодших розрядів та шину старших розрядів пристрою, який відрізняється тим, що введено двійковий лічильник, лічильний вхід якого під'єднано до тактової шини пристрою, перший постійний запам'ятовуючий пристрій, адресні входи, якого під'єднані до відповідних виходів двійкового лічильника, перший цифровий суматор, перші входи якого з'єднані з виходами першого постійного запам'ятовуючого пристрою, аналоговий комутатор, перший вхід якого під'єднано до виходу блока вибірки та зберігання, а другий вхід під'єднано до виходу різницевого підсилювача, вихід аналогового комутатора під'єднано до аналогового входу малорозрядного АЦП, а керувальний вхід під'єднано до шини керування пристрою, другий цифровий суматор, другий постійний запам'ятовуючий пристрій, адресні входи якого з'єднано з виходами малорозрядного АЦП, з другими входами другого цифрового суматора та з другими входами першого цифрового суматора, інформаційні входи другого постійного запам'ятовуючого пристрою під'єднано до виходів першого цифрового суматора, а виходи другого постійного запам'ятовуючого пристрою з'єднано з першими входами другого цифрового суматора, інвертор, крім того пристрій містить перший та другий буферні регістри, причому виходи другого цифрового суматора з'єднано з входами першого та другого буферних регістрів, виходи першого буферного регістра під'єднано до шини старших розрядів пристрою, виходи другого буферного регістра під'єднано до шини молодших розрядів пристрою, вхід інвертора з'єднано з шиною керування пристрою та керувальним входом першого буферного регістра, а вихід інвертора з'єднано з керувальним входом другого буферного регістра. UA 120126 U (54) ПРИСТРІЙ ДЛЯ АНАЛОГО-ЦИФРОВОГО ПЕРЕТВОРЕННЯ UA 120126 U UA 120126 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до автоматики і обчислювальної техніки та призначена для перетворення швидкозмінних аналогових сигналів у цифровий код. Відомий пристрій для аналого-цифрового перетворення, який містить групу компараторів старших розрядів і групу компараторів молодших розрядів, перші входи яких підключені до джерел опорних напруг, сигнальні входи групи компараторів старших розрядів підключені до джерела вхідного сигналу, який перетворюється, а виходи компараторів в кожній групі, крім компараторів старших розрядів, об'єднані попарно і підключені до керуючих входів елементів пам'яті, і резистивні підсилювачі, перші входи яких підключені до джерел струмів зміщення, другі через повторювач та інвертор підключені до джерела вхідного сигналу, який перетворюється, а виходи попарно зі зсувом на один підключені до входів елемента, виходи яких через елемент АБО з'єднані з сигнальними входами компараторів молодших розрядів, входи стробування елементів пам'яті підключені до джерела стробуючого сигналу (А.с. СРСР № 879771, МКИ Н03K 5/22, бюлетень № 41, 1981 р.). Недоліком даного перетворювача є низька точність. Відомий пристрій для аналого-цифрового перетворення, який містить аналого-цифровий перетворювач (АЦП), тактові і опорні входи якого є відповідно тактовою і опорною шинами, а інформаційний вхід з'єднаний з виходом блока зміни координати положення, інформаційний вхід якого є вхідною шиною, група керуючих входів з'єднана відповідно з першими входами блока керування, постійний запам'ятовуючий пристрій (ПЗП), перші і другі входи якого під'єднані відповідно до відповідних виходів АЦП та до відповідних других виходів блока керування, а вихід є вихідною шиною, причому тактовий вхід блока керування з'єднаний з тактовою шиною, інформаційні входи з'єднані з відповідними виходами АЦП, опорний вхід блока зміни координати положення з'єднаний з шиною опорної напруги, а сам блок зміни координати положення виконаний на підсумовуючому підсилювачі і трьох ключах, виходи яких з'єднані відповідно з першим, другим і третім входами підсумовуючого підсилювача, четвертий вхід якого є інформаційним входом блока керування, групою керуючих входів якого є керуючі входи відповідно першого, другого і третього ключів, інформаційні входи яких об'єднані і є опорним входом блока, а його виходом є вихід підсумовуючого підсилювача, блок керування виконаний на двох ПЗП і регістрі пам'яті, перша і друга групи інформаційних входів якого з'єднані з відповідними виходами першої і другої групи виходів першого ПЗП, і перша група виходів є першими виходами блока керування, другими виходами якого є третя група виходів першого ПЗП, перша група входів якого з'єднана з відповідними виходами регістра пам'яті, а друга група входів з'єднана з відповідними виходами другого ПЗП, входи якого є інформаційними входами блоку керування, тактовим входом якого є вхід синхронізації регістра пам'яті [А.с. СРСР № 1425828, М.кл. А1 - Н03М 1/18, Бюл. № 35, 1988 р.]. Недоліком даного пристрою для аналого-цифрового перетворення є низька точність. Найбільш близьким є пристрій для аналого-цифрового перетворення, який містить блок вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, малорозрядний АЦП, аналоговий вхід якого під'єднано до виходу блока вибірки та зберігання, а виходи малорозрядного АЦП підключені до шини старших розрядів пристрою, тактовий вхід малорозрядного АЦП під'єднано до тактової шини пристрою, цифроаналоговий перетворювач (ЦАП), входи якого під'єднані до відповідних виходів малорозрядного АЦП, різницевий підсилювач, перший вхід якого з'єднаний з виходом ЦАП, другий вхід різницевого підсилювача під'єднано до виходу блока вибірки та зберігання, а до виходу різницевого підсилювача під'єднані компаратори, другі входи яких під'єднані до шини опорної напруги, виходи компараторів під'єднані до шин молодших розрядів пристрою [заявка ФРН № 274316, кл. Н03К 13/05]. Недоліками даного пристрою є низька точність, що обумовлена наявністю диференціальної нелінійності характеристики перетворення АЦП, що призводить до збільшення похибки пристрою аналого-цифрового перетворення. В основу корисної моделі поставлено задачу створення пристрою для аналого-цифрового перетворення, в якому за рахунок введення нових блоків та зв'язків підвищується точність перетворення шляхом цифрового коригування результатів аналого-цифрового перетворення. Поставлена задача вирішується тим, що в пристрій для аналого-цифрового перетворення, який містить блок вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, малорозрядний АЦП, тактовий вхід якого під'єднано до тактової шини пристрою, ЦАП, входи якого під'єднані до відповідних виходів малорозрядного АЦП, різницевий підсилювач, другий вхід якого під'єднано до виходу блока вибірки та зберігання, а перший вхід до виходу ЦАП, шину молодших розрядів та шину старших розрядів пристрою, введені двійковий лічильник, лічильний вхід якого під'єднано до тактової шини 1 UA 120126 U 5 10 15 20 25 30 35 40 45 50 55 60 пристрою, перший ПЗП, адресні входи якого під'єднані до відповідних виходів двійкового лічильника, перший цифровий суматор, перші входи якого з'єднані з виходами першого ПЗП, аналоговий комутатор, перший вхід якого під'єднано до виходу блока вибірки та зберігання, а другий вхід під'єднано до виходу різницевого підсилювача, вихід аналогового комутатора під'єднано до аналогового входу малорозрядного АЦП, а керувальний вхід під'єднано до шини керування пристрою, другий цифровий суматор, другий ПЗП, адресні входи якого з'єднано з виходами малорозрядного АЦП, з другими входами другого цифрового суматора та з другими входами першого цифрового суматора, інформаційні входи другого ПЗП під'єднано до виходів першого цифрового суматора, а виходи другого ПЗП з'єднано з першими входами другого цифрового суматора, інвертор, перший та другий буферні регістри, виходи другого цифрового суматора з'єднано з входами першого та другого буферних регістрів, виходи першого буферного регістра під'єднано до шини старших розрядів пристрою, виходи другого буферного регістра під'єднано до шини молодших розрядів пристрою, вхід інвертора з'єднано з шиною керування пристрою та керувальним входом першого буферного регістра, а вихід інвертора з'єднано з керувальним входом другого буферного регістра, що дає при однаковій кількості розрядів пристрою для аналого-цифрового перетворення, який пропонується і прототипу, підвищення точності шляхом цифрового коригування результатів аналого-цифрового перетворення. На кресленні наведена структурна електрична схема пристрою для аналого-цифрового перетворення. Пристрій містить тактову шину 1, шину джерела вхідного сигналу 2, Uвх, шину керування 3, блок вибірки та зберігання (БВЗ) 4, двійковий лічильник 5, аналоговий комутатор 6, блок різницевого підсилювача 7, перший ПЗП 8, малорозрядний АЦП 9, ЦАП 10, перший цифровий суматор 11, другий ПЗП 12, другий цифровий суматор 13, інвертор 14, перший буферний регістр 15, другий буферний регістр 16, шину старших розрядів пристрою 17, шину молодших розрядів пристрою 18, причому вхід БВЗ 4 під'єднано до шини джерела вхідного сигналу 2, який підлягає перетворенню, тактовий вхід малорозрядного АЦП 9 під'єднано до тактової шини 1 пристрою, входи ЦАП 10 під'єднані до відповідних виходів малорозрядного АЦП 9, другий вхід різницевого підсилювача 7 під'єднано до виходу БВЗ 4, лічильний вхід двійкового лічильника 5 під'єднано до тактової шини 1 пристрою, адресні входи першого ПЗП 8 під'єднані до відповідних виходів двійкового лічильника 5, перші входи першого цифрового суматора 11 з'єднані з виходами першого ПЗП 8, перший вхід аналогового комутатора 6 під'єднано до виходу БВЗ 4, другий вхід під'єднано до виходу різницевого підсилювача 7, вихід аналогового комутатора 6 під'єднано до аналогового входу малорозрядного АЦП 9, керувальний вхід якого під'єднано до шини керування 3 пристрою, вихід ЦАП 10 з'єднано з першим входом різницевого підсилювача 7, адресні входи другого ПЗП 12 з'єднано з виходом малорозрядного АЦП 9, з входом ЦАП 10, другими входами першого цифрового суматора 11 та другими входами другого цифрового суматора 13, інформаційні входи другого ПЗП 12 під'єднано до виходів першого цифрового суматора 11, а виходи другого ПЗП 12 з'єднано з першими входами другого цифрового суматора 13, виходи якого з'єднано з входами першого 15 та другого 16 буферних регістрів, виходи першого буферного регістра 15 під'єднано до шини старших розрядів 17 пристрою, виходи другого буферного регістра 16 під'єднано до шини молодших розрядів 18 пристрою, вхід інвертора 14 з'єднано з шиною керування пристрою 3 та керувальним входом першого буферного регістра 15, а вихід інвертора з'єднано з керувальним входом другого буферного регістра 16. Пристрій для аналого-цифрового перетворення працює наступним чином. В режимі калібрування встановлюється сигнал "запис" на керувальному вході другого ПЗП 12. На шину 2 джерела вхідного сигналу надходить синусоїдальний тестовий сигнал, а малорозрядний АЦП 9 перетворює його в цифрову форму, використовуючи стробуючі імпульси, які надходять на тактовий вхід малорозрядного АЦП 9 з тактової шини 1. Отриманий сигнал надходить на другі входи першого цифрового суматора 11 та на адресні входи другого ПЗП 12. З тактової шини 1 стробувальні імпульси надходять також на лічильний вхід двійкового лічильника 5, який формує код адреси зразкового цифрового синусоїдального сигналу, записаного в першому ПЗП 8. Цифрові еквіваленти синусоїдального сигналу з виходу першого ПЗП 8 подаються на перші входи першого цифрового суматора 11, який формує на виході код коригувальної похибки Δу(n), яка в свою чергу записується за адресою сформованою цифровим сигналом з виходу малорозрядного АЦП 9. Калібрування виконується у всіх точках цифрового синусоїдального сигналу, записаного в першому ПЗП 8. Другий цифровий суматор 13 в режимі калібрування не функціонує, тому що другий ПЗП 12 працює в режимі запису і на його вихідній шині встановлено третій високоімпедансний стан. 2 UA 120126 U 5 10 15 20 25 30 У робочому режимі встановлюється сигнал "читання" на керувальному вході другого ПЗП 12, тому вихідний сигнал з першого цифрового суматора 11 заблокований. На шину 1 джерела вхідного сигналу надходить аналоговий сигнал, який через БВЗ 4 у вигляді дискретної вибірки подається на вхід малорозрядного АЦП 9 і перетворюється в цифровий код. Вихідний код АЦП надходить на адресні входи другого ПЗП 12 та другі входи другого цифрового суматора 13. Цей вихідний код АЦП утворює адресу вибірки сигналу похибки Δу(n), який надходить на перший вхід другого цифрового суматора 13. У результаті на виході другого цифрового суматора 13 формується скоригований код ys(n)=у(n)-Δу(n), який є цифровим сигналом старших розрядів, що через перший буферний регістр 15 подається на шину старших розрядів 17 пристрою. Другий буферний регістр 16 заблокований вихідним сигналом інвертора 14. Вихідний сигнал ЦАП 10, що є аналоговим еквівалентом старших розрядів АЦП, подається на перший вхід різницевого підсилювача 7. На другий вхід різницевого підсилювача 7 подається з виходу БВЗ 4 дискретна вибірка аналогового сигналу. У результаті на виході різницевого підсилювача 7 утворюється підсилений різницевий сигнал для формування молодших розрядів АЦП. Після встановлення на керувальній шині 3 одиничного імпульсу, вихідний сигнал з різницевого підсилювача 7 через аналоговий комутатор 6 подається на вхід малорозрядного АЦП 9. Потім після подачі з тактової шини 1 стробувального імпульсу на тактовий вхід малорозрядного АЦП 9 відбувається перетворення різницевого сигналу у цифровий код молодших розрядів. За допомогою другого ПЗП 12 та другого цифрового суматора 13 відбувається коригування коду молодших розрядів: yl(n)=у(n)-Δу(n). Цей код через другий буферний регістр 16, що активізується керувальним сигналом з інвертора 14, подається на шину молодших розрядів 18. У результаті такого двоетапного перетворення формується повний скоригований цифровий код, що складається з групи старших і групи молодших розрядів. Таким чином, запропонований пристрій для аналого-цифрового перетворення дає можливість збільшити точність за рахунок врахування диференціальної нелінійності малорозрядного АЦП та цифрового коригування його вихідного коду в процесі виконання кожного з двох етапів аналого-цифрового перетворення вхідного сигналу. Окрім цього, на відміну від аналогового коригування, запропонований пристрій для аналого-цифрового перетворення з цифровим коригуванням усуває із загальної похибки АЦП інструментальну цифроаналогового перетворювача. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 35 40 45 50 55 Пристрій для аналого-цифрового перетворення, який містить блок вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, малорозрядний АЦП, тактовий вхід якого під'єднано до тактової шини пристрою, ЦАП, входи якого під'єднані до відповідних виходів малорозрядного АЦП, різницевий підсилювач, другий вхід якого під'єднано до виходу блока вибірки та зберігання, а перший вхід до виходу ЦАП, шину молодших розрядів та шину старших розрядів пристрою, який відрізняється тим, що введено двійковий лічильник, лічильний вхід якого під'єднано до тактової шини пристрою, перший постійний запам'ятовуючий пристрій, адресні входи, якого під'єднані до відповідних виходів двійкового лічильника, перший цифровий суматор, перші входи якого з'єднані з виходами першого постійного запам'ятовуючого пристрою, аналоговий комутатор, перший вхід якого під'єднано до виходу блока вибірки та зберігання, а другий вхід під'єднано до виходу різницевого підсилювача, вихід аналогового комутатора під'єднано до аналогового входу малорозрядного АЦП, а керувальний вхід під'єднано до шини керування пристрою, другий цифровий суматор, другий постійний запам'ятовуючий пристрій, адресні входи якого з'єднано з виходами малорозрядного АЦП, з другими входами другого цифрового суматора та з другими входами першого цифрового суматора, інформаційні входи другого постійного запам'ятовуючого пристрою під'єднано до виходів першого цифрового суматора, а виходи другого постійного запам'ятовуючого пристрою з'єднано з першими входами другого цифрового суматора, інвертор, крім того пристрій містить перший та другий буферні регістри, причому виходи другого цифрового суматора з'єднано з входами першого та другого буферних регістрів, виходи першого буферного регістра під'єднано до шини старших розрядів пристрою, виходи другого буферного регістра під'єднано до шини молодших розрядів пристрою, вхід інвертора з'єднано з шиною керування пристрою та керувальним входом першого буферного регістра, а вихід інвертора з'єднано з керувальним входом другого буферного регістра. 3 UA 120126 U Комп’ютерна верстка В. Мацело Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 1/18

Мітки: пристрій, перетворення, аналого-цифрового

Код посилання

<a href="https://ua.patents.su/6-120126-pristrijj-dlya-analogo-cifrovogo-peretvorennya.html" target="_blank" rel="follow" title="База патентів України">Пристрій для аналого-цифрового перетворення</a>

Попередній патент: Електромагнітний засіб визначення механічної напруженості у матеріалах конструктивних елементів

Наступний патент: Перетворювач магнітної індукції з активним індуктивним елементом

Випадковий патент: Спосіб діагностики вестибулярної дисфункції у хворих зі струсом головного мозку у гострому періоді черепно-мозкової травми