Цифровий регулятор

Формула / Реферат

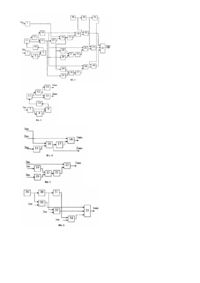

1. Цифровий регулятор, що містить з'єднані блок фіксатора помилки і блок вибірки, який відрізняється тим, що він додатково містить блоки формування сигналів m0, m1, m2, і блок виміру швидкості сигналу, перший та другий виходи якого з'єднані відповідно з другими та третіми входами блоків формування сигналів m0, m1, m2, вихід блока фіксатора помилки з'єднаний з першим входом блока формування сигналу m0, другий вихід блока формування сигналу та з'єднаний з першими входами блоків формування сигналів m1, m2, а перші виходи блоків формування сигналів m0, m1, m2 з'єднані відповідно з входами блока вибірки.

2. Цифровий регулятор за п. 1, який відрізняється тим, що блок виміру швидкості сигналу містить блок фіксатора, перший вихід якого з'єднаний з першим входом блока віднімання, а другий вихід з'єднаний з блоком затримки, блок затримки з'єднаний з другим входом блока віднімання, вихід блока віднімання з'єднаний з входом блока підсилення, вихід блока підсилення з'єднаний з входом блока фіксатора, блок фіксатора, другий вихід якого з'єднаний з другим входом блока віднімання, а перший вихід з'єднаний з входом блока затримки, вихід блока затримки з'єднаний з входом блока підсилення та з першим входом блока віднімання.

3. Цифровий регулятор за п. 1, який відрізняється тим, що блок формування сигналу m0 містить блок підсилення, вихід якого з'єднаний з другим входом блока суматора, вихід блока суматора з'єднаний з входом блока підсилення, а вихід блока підсилення з'єднаний з другим входом блока суматора.

4. Цифровий регулятор за п. 1, який відрізняється тим, що блок формування сигналу m1 містить блок підсилення, вихід якого з'єднаний з першим входом блока суматора, вихід блока підсилення з'єднаний з другим входом блока суматора, вихід блока суматора з'єднаний з входом блока підсилення, а вихід блока підсилення з'єднаний з другим входом блока суматора.

5. Цифровий регулятор за п. 1, який відрізняється тим, що блок формування сигналу m2 містить блок підсилення, вихід якого з'єднаний з першим входом блока суматора, вихід блока підсилення з'єднаний з другим входом блока суматора, вихід блока суматора з'єднаний з входом блока підсилення, а вихід блока підсилення з'єднаний з другим входом блока суматора.

Текст

Винахід відноситься до галузі автоматики, і може бути використаний в системах автоматичного керування, в яких об'єкт управління можна описати лінійною динамічною моделлю з передавальною функцією любого порядку. Відомий регулятор [1], що містить паралельно з'єднані пропорційне звено, інтегральне звено та диференційне звено. Регулятор виробляє вихідний сигнал, який є сумою трьох складових пропорційного регулювання, регулювання по інтегралу і регулювання по похідній. Перше звено пропорційне помилці вихідної величини, друга - інтегралу по часу помилки вихідної величини, а третє звено - похідній помилки. Відомий також цифровий регулятор [1], що містить блоки підсилення з коефіцієнтами підсилення b 0, b1, b2 і а1, -а2, шість блоків ліній затримки та суматор. Похибка системи по трьом паралельним каналам поступає на суматор: перший канал містить блок підсилення з коефіцієнтами підсилення b0, другий канал містить послідовно з'єднані блок лінії затримки та блок підсилення з коефіцієнтами підсилення b1, третій канал містить два блоки ліній затримки та блок підсилення з коефіцієнтами підсилення b2. Вихід суматора по двум каналам зворотного зв'язку з'єднаний з його входом: перший канал містить послідовно з'єднані блок лінії затримки та блок підсилення з коефіцієнтами підсилення –а1, другий канал містить два блоки ліній затримки та блок підсилення з коефіцієнтами підсилення –а2. Коефіцієнти підсилення b0, b1, b2 і –а1, -а2 вибираються з умов підвищення точності системи або забезпечення оптимального перехідного процесу. Недоліки аналогів полягають в тому, що при забезпеченні оптимального (чи близького к оптимальному) перехідного процесу не можливо забезпечити достатньо високу точність системи в установленому режимі, і навпаки, при забезпеченні високої точності системи в установленому режимі не можливо забезпечити якісний перехідний процес. В якості прототипу вибраний оптимальний по швидкодії цифровий регулятор [2], що містить блок фіксатора помилки, три блоки підсилення та блок вибірки. Блок фіксатора фіксує похибку системи з інтервалом регулювання tp=Nh. Блок фіксатора з'єднаний з трьома блоками підсилення, які працюють з коефіцієнтами підсилення K0, q1K0, q2K0. Виходи блоків підсилення з'єднані відповідно з трьома входами блоку вибірки, що працює із кроком квантування h і забезпечує кінцеві по тривалості перехідні процеси (реакції систем на ступінчатий вплив), що закінчуються за час Nh, де N- порядок об'єкта управління. Блок вибірки складається з блоку імпульсного генератора, двох блоків затримки, та трьох блоків множення. Імпульсний генератор генерує імпульси одиничної амплітуди тривалістю h з періодом проходження Nh. Ці імпульси безпосередньо з генератора і з блоків затримок (кожна для зрушення імпульсів на крок квантування h) надходять на відповідні блоки множення і утворюють стробуючі тривалістю h імпульси, необхідні для тимчасового розподілу імпульсів оптимального керуючого впливу m 0, m 1, m 2. В результаті отримуємо серію імпульсних сигналів, амплітуда котрих вра ховує похибку системи. Недоліком прототипу є недостатньо висока якість системи, в наслідок значних похибок системи при довільних вхідних сигналах. В основу винаходу поставлена задача удосконалення цифрового регулятора за рахунок введення блоку виміру швидкості, який обраховує поточне значення швидкості (першу різницю) вхідного довільного впливу, та приріст швидкості довільного вхідного впливу на інтервалі регулювання. Це забезпечує підвищення точності відпрацювання вхідного сигналу систем автоматичного керування при довільних впливах на систему керування і дозволяє значно зменшити похибку системи. Поставлена задача вирішується тим, що в цифровому регуляторі, який містить блок фіксатора помилки і блок вибірки, додатково введені блоки формування сигналів m 0, m 1, m 2, і блок виміру швидкості сигналу. При цьому перший та другий виходи блоку виміру швидкості сигналу з'єднані відповідно з другими та третіми входами блоків формування сигналів m 0, m 1, m 2, вихід блоку фіксатора помилки з'єднаний з першим входом блоку формування сигналу m 0, другий ви хід блоку формування сигналу m 0 з'єднаний з першими входами блоків формування сигналів m 1, m 2, а перші виходи блоків формування сигналів m 0, m 1, m 2 з'єднані відповідно з входами блоку вибірки. При цьому блок виміру швидкості сигналу містить блок фіксатора, перший вихід якого з'єднаний з першим входом блоку віднімання, а другий вихід з'єднаний з блоком затримки, блок затримки з'єднаний з другим входом блоку віднімання, вихід блоку віднімання з'єднаний з входом блоку підсилення, вихід блоку підсилення з'єднаний з входом блоку фіксатора, блок фіксатора, другий ви хід якого з'єднаний з другим входом блоку віднімання, а перший вихід з'єднаний з входом блоку затримки, вихід блоку затримки з'єднаний з входом блоку підсилення та з першим входом блоку віднімання. При цьому блок формування сигналу m 0 містить блок підсилення, вихід якого з'єднаний з другим входом блоку суматора, вихід блоку суматора з'єднаний з входом блоку підсилення, а вихід блоку підсилення з'єднаний з другим входом блоку суматора. При цьому блок формування сигналу m 1 містить блок підсилення, вихід якого з'єднаний з першим входом блоку суматора, вихід блоку підсилення з'єднаний з другим входом блоку суматора, вихід блоку суматора з'єднаний з входом блоку підсилення, а вихід блоку підсилення з'єднаний з другим входом блоку суматора. При цьому блок формування сигналу m 2 містить блок підсилення, вихід якого з'єднаний з першим входом блоку суматора, вихід блоку підсилення з'єднаний з другим входом блоку суматора, вихід блоку суматора з'єднаний з входом блоку підсилення, а вихід блоку підсилення з'єднаний з другим входом блоку суматора. Таким чином цифровий регулятор враховує не тільки похибку системи, а й швидкість (першу різницю) та приріст швидкості вхідного довільного впливу, що забезпечує значно меншу похибку системи. Суть винаходу пояснюється кресленнями (див.фіг.) де зображені: - на фіг.1 - загальна структурна схема цифрового регулятора; - на фіг.2 - детальна структурна схема цифрового регулятора; - на фіг.3 - стр уктурна схема блоку виміру швидкості сигналу; - на фіг.4 - стр уктурна схема блоку формування сигналу m 0, - на фіг.5 - стр уктурна схема блоків формування сигналів m 1, m 2 - на фіг.6 - структурна схема блоку вибірки; - на фіг.7 - зображені амплітудно-часові характеристики сигналів систем автоматичного керування: а) - графік залежності напруги від часу вхідного і вихідного сигналу системи автоматичного керування з оптимальним по швидкодії цифровим регулятором; б) - графік залежності напруги від часу вхідного І ви хідного сигналу системи автоматичного керування з заявленим цифровим регулятором; в) - графік залежності напруги від часу похибки системи автоматичного керування з оптимальним по швидкодії цифровим регулятором; г) - графік залежності напруги від часу похибки системи автоматичного керування з заявленим цифровим регулятором. Фіг.1 містить: блок 1 фіксатора помилки з'єднаний з першим входом блоку 3 формування сигналу m 0; блок 2 виміру швидкості сигналу перший та другий виходи якого з'єднані відповідно з 2 та 3 входами блоку 3 формування сигналу m 0, блоку 4 формування сигналу m 1, блоку 5 формування сигналу m 2, блок 3 формування сигналу m 0 перший вихід якого з'єднаний з першим входом блоку 6 вибірки, а другий вихід якого з'єднаний з першим входом блоку 4 формування сигналу m 1 та з першим входом блоку 5 формування сигналу m 2; блок 4 формування сигналу m 1 і з'єднаний з другим входом блоку 6 вибірки; блок 5 формування сигналу m 1 з'єднаний з третім входом блоку 6 вибірки; Фіг.2 містить: блок 7 фіксатора, перший вихід якого з'єднаний з першим входом блоку 9 віднімання, а другий вихід з'єднаний з входом блоку 8 затримки; блок 9 віднімання з'єднаний з блоком 10 підсилення; блок 10 підсилення з'єднаний з блоком 11 фіксатора; блок 11 фіксатора другий вихід якого з'єднаний з другим входом блоку 13 віднімання, а перший вихід з'єднаний з входом блоку 12 затримки; блок 12 затримки з'єднаний з блоком 14 підсилення та з першим входом блоку 13 віднімання; блок 14 підсилення з'єднаний з першим входом блоку 18 суматора, першим входом блоку 23 суматора та першим входом блоку 28 суматора; блок 13 віднімання з'єднаний з блоком 15 підсилення, блоком 20 підсилення, блоком 25 підсилення; блок 1 фіксатора з'єднаний з першим входом блоку 16 суматора; блок 15 підсилення з'єднаний з другим входом блоку 16 суматора; блок 16 суматора з'єднаний з блоком 17 підсилення, блоком 19 підсилення та блоком 24 підсилення; блок 17 підсилення з'єднаний з другим входом блоку 18 суматора; блок 18 суматора з'єднаний з другим входом блоку 32 множення; блок 19 підсилення з'єднаний з першим входом блоку 21 суматора; блок 20 підсилення з'єднаний з другим входом блоку 21 суматора; блок 21 суматора з'єднаний з блоком 22 підсилення; блок 22 підсилення з'єднаний з другим входом блоку 23 суматора; блок 23 суматора з'єднаний з другим входом блоку 33 множення; блок 24 підсилення з'єднаний з першим входом блоку 26 суматора; блок 25 підсилення з'єднаний з другим входом блоку 26 суматора; блок 26 суматора з'єднаний з блоком 27 підсилення; блок 27 підсилення з'єднаний з другим входом блоку 28 суматора; блок 28 суматора з'єднаний з другим входом блоку 34 множення; блок 29 імпульсного генератора з'єднаний з блоком 30 затримки та першим входом блоку 32 множення; блок 30 затримки з'єднаний з блоком 31 затримки та першим входом блоку 33 множення; блок 31 затримки з'єднаний з першим входом блоку 34 множення; блоки 32, 33, 34 множення з'єднані відповідно з першим, другим, та третім входами блоку 35 суматора. Фіг.3 містить: блок 7 фіксатора, перший вихід якого з'єднаний з першим входом блоку 9 віднімання, а другий вихід з'єднаний з входом блоку 8 затримки; блок 8 затримки з'єднаний з другим входом блоку 9 віднімання; блок 9 віднімання з'єднаний з блоком 10 підсилення; блок 9 віднімання з'єднаний з блоком 10 підсилення; блок 10 підсилення з'єднаний з блоком 11 фіксатора; блок 11 фіксатора другий вихід якого з'єднаний з другим входом блоку 13 віднімання, а перший вихід з'єднаний з входом блоку 12 затримки; блок 12 затримки з'єднаний з блоком 14 підсилення та з першим входом блоку 13 віднімання; Фіг.4 містить: блок 15 підсилення з'єднаний з другим входом блоку 16 суматора; блок 16 суматора з'єднаний з блоком 17 підсилення; блок 17 підсилення з'єднаний з другим входом блоку 18 суматора. Фіг.5 містить: блок 19 підсилення з'єднаний з першим входом блоку 21 суматора; блок 20 підсилення з'єднаний з другим входом блоку 21 суматора; блок 21 суматора з'єднаний з блоком 22 підсилення; блок 22 підсилення з'єднаний з другим входом блоку 23 суматора. Фіг.6 містить: блок 29 імпульсного генератора з'єднаний з блоком 30 затримки та першим входом блоку 32 множення; блок 30 затримки з'єднаний з блоком 31 затримки та першим входом блоку 33 множення; блок 31 затримки з'єднаний з першим входом блоку 34 множення; блоки 32, 33, 34 множення з'єднані відповідно з першим, другим, та третім входами блоку 35 суматора. На фіг.7 зображені амплітудно-часові характеристики сигналів систем автоматичного керування: а) - графік залежності напруги від часу вхідного і вихідного сигналу системи автоматичного керування з оптимальним по швидкодії цифровим регулятором; б) - графік залежності напруги від часу вхідного і вихідного сигналу системи автоматичного керування з заявленим цифровим регулятором; в) - графік залежності напруги від часу похибки системи автоматичного керування з оптимальним по швидкодії цифровим регулятором; г) - графік залежності напруги від часу похибки системи автоматичного керування з заявленим цифровим регулятором. Пристрій працює наступним чином: Вихідний сигнал з системи керування (похибка системи O(t ) поступає на блок 1 фіксатора Фіг.1, який фіксує сигнал з інтервалом регулювання tp=Nh. З виходу блоку фіксатора сигнал поступає на перший вхід блоку З формування сигналу m 0. Вхідний сигнал з системи керування U(t) поступає на блок 2 виміру швидкості сигналу, який обраховує поточне значення швидкості (першу різницю) вхідного сигналу, та приріст швидкості вхідного сигналу на інтервалі s регулювання. Обраховані поточне значення швидкості (перша різниця) вхідного сигналу n-1 з першого виходу та приріст швидкості вхідного сигналу на інтервалі регулювання Ds з другого виходу блоку 2 виміру швидкості сигналу поступають відповідно на другий та третій входи блоку 3 формування сигналу m 0, в якому формується DU + S0 Ds сигнал m 0 амплітуда якого визначається виразом (1) та сигнал з амплітудою , який з другого виходу блоку 3 формування сигналу m 0 поступає на перший вхід блоку 4 формування сигналу m 1 та на перший вхід s блоку 5 формування сигналу m 2. Обра ховані поточне значення швидкості (перша різниця) вхідного сигналу n -1 з першого виходу та приріст швидкості вхідного сигналу на інтервалі регулювання Ds з др угого виходу блоку 2 виміру швидкості сигналу поступають відповідно на другий та третій входи блоку 4 формування сигналу m 1, в якому формується сигнал m 1 амплітуда якого визначається виразом (2). Обраховані поточне значення швидкості s (перша різниця) вхідного сигналу - n-1 з першого виходу та приріст швидкості вхідного сигналу на інтервалі регулювання з другого виходу блоку 2 виміру швидкості сигналу поступають відповідно на другий та третій входи блоку 5 формування сигналу m 2, в якому формується сигнал m 2 амплітуда якого визначається виразом (3). Сигнал m 0 з першого виходу блоку 3 формування сигналу m 0 поступає на перший вхід блоку 6 вибірки. Сигнал m 1 з виходу блоку 4 формування сигналу m 1 поступає на другий вхід блоку 6 вибірки. Сигнал m 2 з виходу блоку 5 формування сигналу m 2 поступає на третій вхід блоку 6 вибірки, якийформує серію імпульсів оптимального керуючого впливу сигналів m 0, m 1, m 2. В блоці 2 виміру швидкості сигналу фіг.3 вхідний сигнал з системи керування U(t) поступає на блок 7 фіксатора, який квантує сигнал U(t) з кроком моделювання – h0, перший вихід якого з'єднаний з першим входом блоку 9 віднімання, а другий вихід з'єднаний з блоком 8 затримки (затримує сигнал з кроком моделювання h 0), блок 8 з'єднаний з другим входом блоку 9 віднімання, де обчислюється різниця затриманого та незатриманого сигналу (вимірюється поточне значення швидкості довільного вхідного впливу з шагом моделювання – h0), блок 9 з'єднаний з блоком 10 підсилення, який підсилює вхідний сигнал з коефіцієнтом підсилення 1/h0, блок 10 підсилення з'єднаний з блоком 11 фіксатора, який квантує вхідний сигнал з кроком квантування Nh (N - порядок об'єкта управління, h - крок квантування), блок 11 фіксатора перший вихід якого з'єднаний з другим входом блоку 13 віднімання, а другий ви хід якого з'єднаний з входом блоку 12 затримки (затримує вхідний сигнал з кроком квантування Nh), блок 12 з'єднаний з блоком 14 підсилення (підсилює вхідний сигнал з коефіцієнтом підсилення R} та з першим входом блоку 13 віднімання, який обчислює різницю затриманого та незатриманого сигналу (вимірює приріст швидкості довільного вхідного впливу на інтервалі регулювання tp=Nh). Обраховані перша s різниця вхідного впливу n-1 з першого виходу блоку виміру швидкості сигналу та приросту швидкості на інтервалі регулювання - Ds з другого ви ходу блоку виміру швидкості сигналу поступають відповідно на другі та треті входи блоків формування сигналів m 0, m 1, m 2. В блоці 3 формування сигналу m 0 фіг.4 блок 15 підсилення підсилює сигнал Ds з коефіцієнтом підсилення So і з'єднаний з другим входом блоку 16 суматора (сумує вхідні сигнали) на перший вхід якого поступає похибка DU + S0 Ds системи. На виході блоку 16 формується сигнал з амплітудою , який з'єднаний з блоком 17 підсилення, який підсилює сигнал з коефіцієнтом підсилення К 0, блок 17 підсилення з'єднаний з другим входом блоку 18 s суматора (сумує вхідні сигнали) на перший вхід якого поступає перша різниця вхідного довільного впливу R n-1 , на виході блоку 18 суматора формується сигнал m 0 амплітуда якого визначається виразом (1). Сигнал з DU + S0 Ds амплітудою з другого виходу блоку 3 формування сигналу m 0 поступає на другі входи блоку 4 формування сигналів m 1 та блоку 5 формування сигналу m 2. В ідентичних блоках 4, 5 формування сигналів m 1, m 2 які відрізняються тільки коефіцієнтами підсилення DU + S0 Ds підсилювачів перед першим суматором Фіг.5, сигнал поступає на блок 19 підсилення, який підсилює вхідний сигнал з коефіцієнтом підсилення ql (q2 для блоку 5). З ви ходу блоку 19 підсилення сигнал поступає на перший вхід блоку 21 суматора, сигнал Ds поступає на блок 20 підсилення, який підсилює вхідний сигнал з коефіцієнтом підсилення h (h(l+ql) для блоку 5). Сигнал з блоку 20 підсилення поступає на блок 21 суматора (сумує вхідні сигнали), з блоку 21 суматора сигнал поступає на блок 22 підсилення, який підсилює вхідний сигнал з коефіцієнтом підсилення К0, з блоку 22 підсилення сигнал поступає на другим вхід блоку 23 суматора, на s перший вхід якого поступає сигнал R n-1 , який сумує вхідні сигнали, на виході блоку 23 формується сигнал m 1 (m 1 для блоку 5) амплітуда якого визначається виразом (2) (виразом (3) для блоку 5). Амплітуди імпульсів тривалістю h оптимального керуючого впливу на об'єкт керування при лінійно змінюючомуся сигналі на вході системи управління на n-м інтервалі регулювання визначаються [3]: m0 = K 0 (D U + S0Ds ) + Rsn-1, ntp £ t £ ntp + h; (1) m1 = K 0 [q1(DU + S0 Ds ) + hD s] + R sn -1, nt p + h £ t £ nt p + 2 h; (2) m2 = K 0 [q 2 (D U + S0 Ds ) + hD s(1 + q1)] + Rsn -1, ntp + 2 h £ t £ ntp + 3 h ; (3) ab a+b h(2 + q1) K0 = ; S 0 = 3h + ; ah(1 - A(1- B )) ab (1- A )(1 - B ) де ab R= ; q1 = - (A + B); q 2 = AB ; A = e -ah ; B = e -bh . a DU = On O , де n - помилка на вході регулятора в момент початку n-го інтервалу регулювання тривалістю tp =Nh, тобто помилка в момент ntp. h- крок квантування. N=3 - порядок об'єкта керування. Ds = s n - sn -1 s - приріст швидкості на інтервалі регулювання ntp £ t

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital controller

Назва патенту російськоюЦифровой регулятор

МПК / Мітки

МПК: H03L 5/00

Код посилання

<a href="https://ua.patents.su/6-65784-cifrovijj-regulyator.html" target="_blank" rel="follow" title="База патентів України">Цифровий регулятор</a>

Попередній патент: Екскаваторне робоче обладнання телескопічного типу

Наступний патент: Пристрій для гомогенізації

Випадковий патент: Спосіб запалювання агломераційної шихти