Буферний каскад

Номер патенту: 71948

Опубліковано: 25.07.2012

Автори: Росощук Анастасія Володимирівна, Азаров Олексій Дмитрович, Богомолов Сергій Віталійович

Формула / Реферат

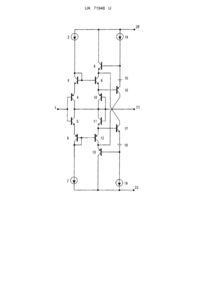

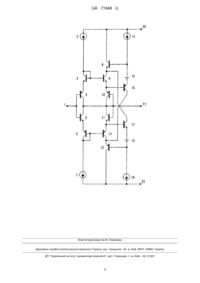

Буферний каскад, який містить десять транзисторів, перше та друге джерело струму, шини додатного та від'ємного живлення, вхідну та вихідну шини причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери першого та восьмого транзисторів з'єднано з емітерами четвертого та п'ятого транзисторів відповідно, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери другого та сьомого транзисторів з'єднано з колекторами третього та шостого транзисторів відповідно, емітери третього та шостого транзисторів з'єднано з емітерами дев'ятого та десятого транзисторів відповідно, другі виводи першого та другого джерела струму з'єднано з шиною додатного і від'ємного живлення відповідно, бази та колектори дев'ятого та десятого транзисторів об'єднано між собою, а також з колекторами четвертого та п'ятого транзисторів та з'єднано з вихідною шиною, бази третього та шостого транзисторів з'єднано з базами першого та восьмого транзисторів відповідно, який відрізняється тим, що у нього введено одинадцятий та дванадцятий транзистори, третє та четверте джерела струму, перше та друге джерела напруги, причому бази одинадцятого та дванадцятого транзисторів з'єднано з емітерами третього, дев'ятого та шостого, десятого транзисторів відповідно, емітери одинадцятого та дванадцятого транзисторів з'єднано з першими виводами першого та другого джерела напруги відповідно, другі виводи першого та другого джерела напруги з'єднано з базами другого та сьомого транзисторів відповідно, а також з першими виводами третього та четвертого джерела струму відповідно, другі виводи третього та четвертого джерела струму з'єднано з шиною додатного і від'ємного живлення відповідно, колектори одинадцятого та дванадцятого транзисторів з'єднано з колекторами шостого та третього транзисторів відповідно, а також з емітерами десятого та дев'ятого транзисторів відповідно, бази та колектори першого та восьмого транзисторів з'єднано з першими виводами першого та другого джерела струму відповідно.

Текст

Реферат: UA 71948 U UA 71948 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах і цифрових вимірювальних приладах. Відомо буферний пристрій (Бахтиаров Г.Д., Малинин В.В., Школин В.П. Аналого-цифровые преобразователи / Под ред. Г.Д. Бахтиарова. - М.: Советское радио, 1980.-280 с. ил. Рис. 6.28 на сторінці 150), який містить вісім транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери другого та сьомого транзисторів з'єднано з колекторами третього та шостого транзисторів відповідно, колектор першого транзистора з'єднано з шиною додатного живлення через відповідні виводи першого джерела струму, колектор восьмого транзистора з'єднано з шиною від'ємного живлення через відповідні виводи другого джерела струму, бази другого та сьомого транзисторів з'єднано з базами та колекторами першого та восьмого транзисторів відповідно, емітери восьмого та п'ятого транзисторів об'єднано між собою та з'єднано з базою шостого транзистора, емітери першого та четвертого транзисторів об'єднано між собою та з'єднано з базою третього транзистора, колектори четвертого та п'ятого транзисторів з'єднано з колекторами шостого та третього транзисторів відповідно, емітери третього та шостого транзисторів об'єднано та з'єднано з вихідною шиною. Основним недоліком аналогу є низька точність, що викликано значною вихідною напругою зміщення нуля через неідентичність параметрів пар n-p-n та p-n-р транзисторів у верхньому та нижньому каналах. За найближчий аналог вибрано буферний каскад (Патент України № 51014, Н03К 5/22, G05B 1/00, 2010 р.), який містить десять транзисторів, перше та друге джерело струму, шини додатного та від'ємного живлення, вхідну та вихідну шини причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери першого та восьмого транзисторів з'єднано з емітерами четвертого та п'ятого транзисторів відповідно, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери другого та сьомого транзисторів з'єднано з базами та колекторами третього та шостого транзисторів відповідно, а також з базами першого та восьмого транзисторів відповідно, емітери третього та шостого транзисторів з'єднано з емітерами дев'ятого та десятого транзисторів відповідно, другі виводи першого та другого джерела струму з'єднано з шиною додатного і від'ємного живлення відповідно, бази другого та сьомого транзисторів з'єднано з колекторами першого та восьмого транзисторів відповідно, а також з першими виводами першого та другого джерела струму відповідно, бази та колектори дев'ятого та десятого транзисторів об'єднано між собою, а також з колекторами четвертого та п'ятого транзисторів та з'єднано з вихідною шиною. Недоліком найближчого аналогу є низька точність, що обмежує галузь використання пристрою. В основу корисної моделі поставлена задача створення буферного каскаду, в якому за рахунок введення нових елементів та зв'язків підвищується точність, це розширює галузь використання корисної моделі у різноманітних цифрових вимірювальних пристроях та аналогово-цифрових перетворювачах. Поставлена задача досягається тим, що в буферний каскад, який містить десять транзисторів, перше та друге джерело струму, шини додатного та від'ємного живлення, вхідну та вихідну шини причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери першого та восьмого транзисторів з'єднано з емітерами четвертого та п'ятого транзисторів відповідно, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери другого та сьомого транзисторів з'єднано з колекторами третього та шостого транзисторів відповідно, емітери третього та шостого транзисторів з'єднано з емітерами дев'ятого та десятого транзисторів відповідно, другі виводи першого та другого джерела струму з'єднано з шиною додатного і від'ємного живлення відповідно, бази та колектори дев'ятого та десятого транзисторів об'єднано між собою, а також з колекторами четвертого та п'ятого транзисторів та з'єднано з вихідною шиною, бази третього та шостого транзисторів з'єднано з базами першого та восьмого транзисторів відповідно, введено одинадцятий та дванадцятий транзистори,третє та четверте джерела струму, перше та друге джерела напруги, причому бази одинадцятого та дванадцятого транзисторів з'єднано з емітерами третього, дев'ятого та шостого, десятого транзисторів відповідно, емітери одинадцятого та дванадцятого транзисторів з'єднано з першими виводами першого та другого джерела напруги відповідно, другі виводи першого та другого джерела напруги з'єднано з базами другого та сьомого транзисторів відповідно, а також з першими виводами третього та четвертого джерела струму відповідно, другі виводи третього та четвертого джерела струму 1 UA 71948 U 5 10 15 20 25 30 35 40 45 50 55 з'єднано з шиною додатного і від'ємного живлення відповідно, колектори одинадцятого та дванадцятого транзисторів з'єднано з колекторами шостого та третього транзисторів відповідно, а також з емітерами десятого та дев'ятого транзисторів відповідно, бази та колектори першого та восьмого транзисторів з'єднано з першими виводами першого та другого джерела струму відповідно. На кресленні представлено принципову схему буферного каскаду. Пристрій містить вхідну шину 1, яку з'єднано з базами четвертого 4 та п'ятого 5 транзисторів, емітери першого 3 та восьмого 6 транзисторів з'єднано з емітерами четвертого 4 та п'ятого 5 транзисторів відповідно, колектори другого 8 та сьомого 13 транзисторів з'єднано з шинами додатного 20 та від'ємного 22 живлення відповідно, емітери другого 8 та сьомого 13 транзисторів з'єднано з колекторами третього 9 та шостого 12 транзисторів відповідно, а також з колекторами дванадцятого 17 та одинадцятого 16, емітери третього 9 та шостого 12 транзисторів з'єднано з емітерами дев'ятого 10 та десятого 11 транзисторів відповідно, а також з базами одинадцятого 16 та дванадцятого 17 транзисторів відповідно, другі виводи першого 2 та другого 7 джерела струму з'єднано з шиною додатного 20 і від'ємного 22 живлення відповідно, бази та колектори дев'ятого 10 та десятого 11 транзисторів об'єднано між собою, а також з колекторами четвертого 4 та п'ятого 5 транзисторів та з'єднано з вихідною шиною 21, бази третього 9 та шостого 12 транзисторів з'єднано з базами та колекторами першого 3 та восьмого 6 транзисторів відповідно, а також з першими виводами першого 2 та другого 7 джерела струму відповідно, емітери одинадцятого 16 та дванадцятого 17 транзисторів з'єднано з першими виводами першого 15 та другого 18 джерела напруги відповідно, другі виводи першого 15 та другого 18 джерела напруги з'єднано з базами другого 8 та сьомого 13 транзисторів відповідно, а також з першими виводами третього 14 та четвертого 19 джерела струму відповідно, другі виводи третього 14 та четвертого 19 джерела струму з'єднано з шиною додатного 20 і від'ємного 22 живлення відповідно. Буферний каскад працює таким чином. Якщо напруга на вхідній шині 1 збільшується, то п'ятий 5 транзистор трохи відкривається, а четвертий 4 транзистор трохи закривається. При цьому напруга на емітерах четвертого 4, п'ятого 5, першого 3, восьмого 6 транзисторів зростає. Водночас зростають потенціали баз третього 9 та шостого 12 транзисторів, а також емітерів дев'ятого 10 та десятого 11 транзисторів. Потенціали точки об'єднання емітерів третього 9 та дев'ятого 10 транзисторів, а також десятого 11 та шостого 12 транзисторів відслідковує потенціали точок об'єднання емітерів першого 3 та четвертого 4 транзисторів, а також п'ятого 5 та восьмого 6 транзисторів відповідно. Підвищення потенціалу точок об'єднання емітерів третього 9 та дев'ятого 10, а також шостого 12 та десятого 11 транзисторів призводить до зростання потенціалу вихідної шини 21. Таким чином потенціал вихідної шини 21 відслідковує потенціал вхідної шини. Якщо напруга на вхідній шині 1 зменшується, то п'ятий 5 транзистор трохи закривається, а четвертий 4 транзистор трохи відкривається. При цьому напруга на емітерах четвертого 4, п'ятого 5, першого 3, восьмого 6 транзисторів зменшується. Водночас зменшуються потенціали баз третього 9 та шостого 12 транзисторів, а також емітерів дев'ятого 10 та десятого 11 транзисторів. Потенціали точки об'єднання емітерів третього 9 та дев'ятого 10 транзисторів, а також десятого 11 та шостого 12 транзисторів відслідковує потенціали точок об'єднання емітерів першого 3 та четвертого 4 транзисторів, а також п'ятого 5 та восьмого 6 транзисторів відповідно. Зменшення потенціалу точок об'єднання емітерів третього 9 та дев'ятого 10, а також шостого 12 та десятого 11 транзисторів призводить до зменшення потенціалу вихідної шини 21. Таким чином потенціал вихідної шини 21 відслідковує потенціал вхідної шини. Перше 15 та друге 18 джерела напруги, третє 14 та четверте 19 джерела струму у поєднанні із одинадцятим 16 і дванадцятим 17 транзисторами забезпечують стабілізацію напруги базаемітер другого 8 та сьомого 13 транзисторів відповідно. Другий 8 та сьомий 13 транзистори у свою чергу забезпечують стабілізацію напруг колектор-емітер третього 9 і шостого 12 транзисторів відповідно. Це зменшує вплив зміни напруги живлення буферного каскаду на появу зсуву напруги по виходу, що у свою чергу призводить до збільшення точності роботи. Перше 2 та друге 7 джерела струму задають режим по постійному струму каскадів схеми. Перший 3, третій 9 та восьмий 6, шостий 12 транзистори утворюють відбивачі струму, які забезпечують збільшення навантажувальної здатності виходу схеми. Четвертий 4 та п'ятий 5 вхідні, а також дев'ятий 10 та десятий 11 вихідні транзистори слугують для передачі сигналу зі входу та на вихід схеми відповідно. Шини додатного 19 і від'ємного 21 живлення забезпечують необхідний рівень напруг для живлення схеми. 60 2 UA 71948 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 Буферний каскад, який містить десять транзисторів, перше та друге джерело струму, шини додатного та від'ємного живлення, вхідну та вихідну шини причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери першого та восьмого транзисторів з'єднано з емітерами четвертого та п'ятого транзисторів відповідно, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери другого та сьомого транзисторів з'єднано з колекторами третього та шостого транзисторів відповідно, емітери третього та шостого транзисторів з'єднано з емітерами дев'ятого та десятого транзисторів відповідно, другі виводи першого та другого джерела струму з'єднано з шиною додатного і від'ємного живлення відповідно, бази та колектори дев'ятого та десятого транзисторів об'єднано між собою, а також з колекторами четвертого та п'ятого транзисторів та з'єднано з вихідною шиною, бази третього та шостого транзисторів з'єднано з базами першого та восьмого транзисторів відповідно, який відрізняється тим, що у нього введено одинадцятий та дванадцятий транзистори, третє та четверте джерела струму, перше та друге джерела напруги, причому бази одинадцятого та дванадцятого транзисторів з'єднано з емітерами третього, дев'ятого та шостого, десятого транзисторів відповідно, емітери одинадцятого та дванадцятого транзисторів з'єднано з першими виводами першого та другого джерела напруги відповідно, другі виводи першого та другого джерела напруги з'єднано з базами другого та сьомого транзисторів відповідно, а також з першими виводами третього та четвертого джерела струму відповідно, другі виводи третього та четвертого джерела струму з'єднано з шиною додатного і від'ємного живлення відповідно, колектори одинадцятого та дванадцятого транзисторів з'єднано з колекторами шостого та третього транзисторів відповідно, а також з емітерами десятого та дев'ятого транзисторів відповідно, бази та колектори першого та восьмого транзисторів з'єднано з першими виводами першого та другого джерела струму відповідно. 3 UA 71948 U Комп’ютерна верстка М. Ломалова Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Назва патенту англійськоюBuffer stage

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych, Rososchuk Anastasia Volodymyrivna

Назва патенту російськоюБуферный каскад

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич, Росощук Анастасия Владимировна

МПК / Мітки

МПК: H03K 5/22

Код посилання

<a href="https://ua.patents.su/6-71948-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Буферний каскад

Наступний патент: Спосіб вимірювання витрат рідини в трубопроводі

Випадковий патент: Спосіб прогнозування зрощення перелому