Реверсивний регістр зсуву

Номер патенту: 83310

Опубліковано: 10.09.2013

Автори: Макаренко Ганна Миколаївна, Литвинова Євгенія Іванівна, Вареца Віталій Вікторович, Хаханов Володимир Іванович, Какурін Микола Яковлевич

Формула / Реферат

Реверсивний регістр зсуву, який складається з групи n тригерів стану, першого елемента АБО, першого і другого елементів І в кожному розряді, комбінаційного двійкового суматора SM кількості одиниць неущільненого двійкового коду, першого DC1 і другого дешифраторів DC2 для перетворення позиційного двійкового коду кількості одиниць в унітарний код одиниць, другого елемента АБО в кожному розряді, крім останнього, третього елемента АБО в кожному розряді, крім першого, четвертого і п'ятого елементів АБО, виходи яких з'єднані з інверсним входом управління відповідно першого DC1 і другого DC2 дешифраторів, входів обнуління і синхронізації регістра зсуву, з'єднаних відповідно з входами обнуління і синхронізації усіх тригерів стану, прямого інформаційного входу реверсивного регістра зсуву, що з'єднаний з першим входом першого елемента І в першому розряді, перший вхід першого елемента І в кожному розряді, крім першого, з'єднаний з прямим виходом тригера попереднього розряду, прямий вихід тригера стану останнього розряду є виходом реверсивного регістра при зсуві праворуч, треті входи обох елементів І в кожному розряді з'єднані з шиною управління режимом роботи регістра зсуву (зсув/ущільнення коду) і з першими входами четвертого і п'ятого елементів АБО, другі входи перших елементів І в кожному розряді з'єднані з шиною зсув праворуч і з другим входом п'ятого елемента АБО, другі входи других елементів І в кожному розряді з'єднані з шиною зсув ліворуч і з другим входом четвертого елемента АБО, прямого інформаційного входу реверсивного регістра зсуву при зсуві ліворуч, що з'єднаний з першим входом другого елемента І в останньому розряді, перший вхід другого елемента І в кожному розряді, крім останнього, з'єднаний з прямим виходом тригера наступного розряду, прямий вихід тригера стану першого розряду є виходом реверсивного регістра зсуву при зсуві ліворуч, в якому прямі виходи тригерів усіх розрядів з'єднані з відповідними входами комбінаційного двійкового суматора SM кількості одиниць неущільненного двійкового коду, виходи якого з'єднані з відповідними входами дешифраторів DC1 і DC2, виходи других схем АБО в кожному розряді, крім останнього, з'єднані відповідно з третім входом першого елемента АБО у даному розряді, другий вхід другого елемента АБО в кожному розряді, крім останнього і передостаннього, з'єднано з виходом другого елемента АБО в наступному розряді, другий вхід другого елемента АБО в передостанньому розряді з'єднано з виходом n дешифратора DC1 і з третім входом першого елемента АБО в останньому розряді, виходи унітарного коду першого дешифратора DC1 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім останнього, виходи унітарного коду другого дешифратора DC2 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім першого, вихід кількості одиниць n другого дешифратора DC2 з'єднано з четвертим входом першого елемента АБО в першому розряді і з другим входом третього елемента АБО в другому розряді, другий вхід третього елемента АБО в кожному розряді, крім першого і другого, з'єднано з виходом третього елемента АБО в попередньому розряді, виходи першого і другого елементів І в кожному розряді з'єднані відповідно з першим і другим входами першого елемента АБО в цьому розряді, який відрізняється тим, що для тригерів стану використані CDR-тригери, причому вихід першого елемента АБО в усіх розрядах з'єднано з D-входами CDR-тригерів.

Текст

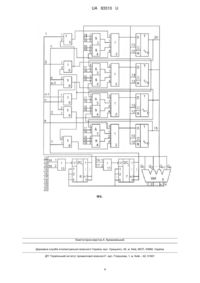

Реферат: Реверсивний регістр зсуву складається з групи n тригерів стану, першого елемента АБО, першого і другого елементів І в кожному розряді, комбінаційного двійкового суматора SM кількості одиниць неущільненого двійкового коду, першого DC1 і другого дешифраторів DC2 для перетворення позиційного двійкового коду кількості одиниць в унітарний код одиниць, другого елемента АБО в кожному розряді, крім останнього, третього елемента АБО в кожному розряді, крім першого, четвертого і п'ятого елементів АБО, виходи яких з'єднані з інверсним входом управління відповідно першого DC1 і другого DC2 дешифраторів, входів обнуління і синхронізації регістра зсуву з'єднаних відповідно з входами обнуління і синхронізації усіх тригерів стану, прямого інформаційного входу реверсивного регістра зсуву, що з'єднаний з першим входом першого елемента І в першому розряді, перший вхід першого елемента І в кожному розряді, крім першого, з'єднаний з прямим виходом тригера попереднього розряду. Прямий вихід тригера стану останнього розряду є виходом реверсивного регістра при зсуві праворуч, треті входи обох елементів І в кожному розряді з'єднані з шиною управління режимом роботи регістра зсуву (зсув/ущільнення коду) і з першими входами четвертого і п'ятого елементів АБО, другі входи перших елементів І в кожному розряді з'єднані з шиною зсув праворуч і з другим входом п'ятого елемента АБО. Другі входи других елементів І в кожному розряді з'єднані з шиною зсув ліворуч і з другим входом четвертого елемента АБО, прямого інформаційного входу реверсивного регістра зсуву при зсуві ліворуч, що з'єднаний з першим входом другого елемента І в останньому розряді. Перший вхід другого елемента І в кожному розряді, крім останнього, з'єднаний з прямим виходом тригера наступного розряду. Прямий вихід тригера стану першого розряду є виходом реверсивного регістра зсуву при зсуві ліворуч, в якому прямі виходи тригерів усіх розрядів з'єднані з відповідними входами комбінаційного двійкового суматора SM кількості одиниць неущільненного двійкового коду, виходи якого з'єднані з відповідними входами дешифраторів DC1 і DC2. Виходи других схем АБО в кожному розряді, крім останнього, з'єднані відповідно з третім входом першого елемента АБО у даному розряді. Другий вхід другого елемента АБО в кожному розряді, крім останнього і передостаннього, з'єднано з виходом другого елемента АБО в наступному розряді. Другий вхід другого елемента АБО в передостанньому розряді з'єднано з виходом n дешифратора DC1 і з третім входом першого елемента АБО в останньому розряді. Виходи унітарного коду першого дешифратора DC1 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім останнього. Виходи унітарного коду другого дешифратора DC2 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім першого. Вихід UA 83310 U (54) РЕВЕРСИВНИЙ РЕГІСТР ЗСУВУ UA 83310 U кількості одиниць n другого дешифратора DC2 з'єднано з четвертим входом першого елемента АБО в першому розряді і з другим входом третього елемента АБО в другому розряді. Другий вхід третього елемента АБО в кожному розряді, крім першого і другого, з'єднано з виходом третього елемента АБО в попередньому розряді. Виходи першого і другого елементів І в кожному розряді з'єднані відповідно з першим і другим входами першого елемента АБО в цьому розряді. Для тригерів стану використані CDR-тригери. Вихід першого елемента АБО в усіх розрядах з'єднано з D-входами CDR-тригерів. UA 83310 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до автоматики і обчислювальної техніки і може бути використана в пристроях діагностування і статистичної обробки інформації. Відомий односторонній регістр зсуву (патент України на корисну модель №71361 МПК 2012.01 G11C 19/00, Бюл. 13, 10.07.2012), що вміщує n-розрядний регістр з CDR-тригерів, комбінаційний двійковий суматор кількості одиниць неущільненого двійкового коду, дешифратор для перетворення позиційного двійкового коду кількості одиниць в унітарний код, один елемент І і один елемент АБО на розряд для управління режимом зсуву коду і управління режимом роботи (зсув коду або ущільнення коду) та по одному другому елементу АБО на кожний розряд, крім останнього, для перетворення унітарного двійкового коду в просторовий. Такий регістр зсуву забезпечує зсув коду праворуч за n тактів, ущільнення двійкового коду тільки ліворуч за один такт, має витрати у три елементи на розряд і не дозволяє виконувати зсув та ущільнення двійкового коду у двох напрямах (ліворуч та праворуч). Найбільш близьким по сукупності ознак до патенту, що заявляється, є реверсивний регістр зсуву (авт. св. СССР № 1642527 МПК G11C 19/00, Бюл. 14, 1991), що містить n-розрядний регістр з CKIR-тригерів, перший і другий елементи АБО, перший і другий елементи АБО-НІ, перший, другий, третій і четвертий елементи І, третій і четвертий елементи АБО на розряд (в першому розряді тільки третій елемент АБО, в останньому розряді тільки четвертий елемент АБО) для перетворення унітарного двійкового коду в просторовий, комбінаційний двійковий суматор SM кількості одиниць неущільненого двійкового коду, два дешифратори DC1 і DC2 для перетворення позиційного двійкового коду кількості одиниць в унітарний код одиниць, п'ятий і шостий елементи АБО для управління синхронізацією відповідно першого і другого дешифраторів DC1 і DC2, входи обнуління і синхронізації регістра зсуву, прямий і інверсний інформаційні входи, та прямий інформаційний вихід регістра зсуву при зсуві праворуч, прямий і інверсний інформаційні входи, та прямий інформаційний вихід регістра при зсуві ліворуч. Такий реверсивний регістр зсуву забезпечує зсув коду як ліворуч, так і праворуч за n тактів, ущільнення двійкового коду як ліворуч, так і праворуч за один такт, але має великі апаратні витрати (10 елементів на розряд), що зумовлює велику складність схеми. В основу корисної моделі поставлена задача створення такого реверсивного регістра зсуву, в якому нове схемне рішення дозволило б при збереженні кількості мікрооперацій і швидкодії істотно зменшити його апаратні витрати. Такий технічний результат може бути досягнутий, якщо в реверсивному регістрі зсуву, який складається з групи n тригерів стану, першого елемента АБО, першого і другого елементів І в кожному розряді, комбінаційного двійкового суматора SM кількості одиниць неущільненого двійкового коду, першого DC1 і другого дешифраторів DC2 для перетворення позиційного двійкового коду кількості одиниць в унітарний код одиниць, другого елемента АБО в кожному розряді, крім останнього, третього елемента АБО в кожному розряді, крім першого, четвертого і п'ятого елементів АБО, виходи яких з'єднані з інверсним входом управління відповідно першого DC1 і другого DC2 дешифраторів, входів обнуління і синхронізації регістра зсуву з'єднаних відповідно з входами обнуління і синхронізації усіх тригерів стану, прямого інформаційного входу реверсивного регістра зсуву, що з'єднаний з першим входом першого елемента І в першому розряді, перший вхід першого елемента І в кожному розряді, крім першого, з'єднаний з прямим виходом тригера попереднього розряду, прямий вихід тригера стану останнього розряду є виходом реверсивного регістра при зсуві праворуч, треті входи обох елементів І в кожному розряді з'єднані з шиною управління режимом роботи регістра зсуву (зсув/ущільнення коду) і з першими входами четвертого і п'ятого елементів АБО, другі входи перших елементів І в кожному розряді з'єднані з шиною зсув праворуч і з другим входом п'ятого елемента АБО, другі входи других елементів І в кожному розряді з'єднані з шиною зсув ліворуч і з другим входом четвертого елемента АБО, прямого інформаційного входу реверсивного регістра зсуву при зсуві ліворуч, що з'єднаний з першим входом другого елемента І в останньому розряді, перший вхід другого елемента І в кожному розряді, крім останнього, з'єднаний з прямим виходом тригера наступного розряду, прямий вихід тригера стану першого розряду є виходом реверсивного регістра зсуву при зсуві ліворуч, в якому прямі виходи тригерів усіх розрядів з'єднані з відповідними входами комбінаційного двійкового суматора SM кількості одиниць неущільненого двійкового коду, виходи якого з'єднані з відповідними входами дешифраторів DC1 і DC2, виходи других схем АБО в кожному розряді, крім останнього, з'єднані відповідно з третім входом першого елемента АБО у даному розряді, другий вхід другого елемента АБО в кожному розряді, крім останнього і передостаннього, з'єднано з виходом другого елемента АБО в наступному розряді, другий вхід другого елемента АБО в передостанньому розряді з'єднано з виходом n дешифратора DC1 і з третім входом першого елемента АБО в останньому розряді, виходи унітарного коду першого дешифратора DC1 з'єднані з відповідним першим входом третього 1 UA 83310 U 5 10 15 20 25 30 35 40 45 50 55 60 елемента АБО в кожному розряді, крім останнього, виходи унітарного коду другого дешифратора DC2 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім першого, вихід кількості одиниць n другого дешифратора DC2 з'єднано з четвертим входом першого елемента АБО в першому розряді і з другим входом третього елемента АБО в другому розряді, другий вхід третього елемента АБО в кожному розряді, крім першого і другого, з'єднано з виходом третього елемента АБО в попередньому розряді, виходи першого і другого елементів І в кожному розряді з'єднані відповідно з першим і другим входами першого елемента АБО в цьому розряді, згідно з корисною моделлю для тригерів стану використані CDR-тригери, причому вихід першого елемента АБО в усіх розрядах з'єднано з Dвходами CDR- тригерів. Таким чином, завдяки новому типу тригера та новому зв'язку, а також вилученню п'ятьох елементів схеми в кожному розряді, створено реверсивний регістр зсуву зі спрощеною схемою, що дозволяє при збереженні швидкодії і функціональних можливостей істотно зменшити його апаратні витрати з десяти до п'яти логічних елементів на один розряд (в першому і останньому розрядах до 4- х). На фігурі зображена структурна схема реверсивного регістра зсуву і ущільнення кодів для узагальненого випадку кількості розрядів n. Реверсивний регістр зсуву містить в кожному розряді CDR-тригер 1, перший 2 елемент АБО, перший 3 і другий 4 елементи І, комбінаційний 5 двійковий суматор SM кількості одиниць неущільненого двійкового колу, перший 6 дешифратор DC1 для перетворення позиційного двійкового коду кількості одиниць в унітарний код при ущільненні ліворуч, другий 7 дешифратор DC2 для перетворення позиційного двійкового коду кількості одиниць в унітарний код при ущільненні праворуч, в усіх розрядах, крім останнього, ланцюг других 8 схем АБО для перетворення унітарного двійкового коду в ущільнений при ущільненні ліворуч, в усіх розрядах, крім першого, ланцюг третіх 9 схем АБО для перетворення унітарного двійкового коду в ущільнений при ущільненні праворуч, четверту 10 і п'яту 11 схеми АБО для управління відповідно синхронізацією першого і другого дешифраторів DC1 і DC2, вхід 12 обнуління регістра зсуву, вхід 13 синхронізації регістра зсуву, прямий 14 інформаційний вхід регістра зсуву при зсуві праворуч, прямий 15 інформаційний вихід регістра зсуву при зсуві праворуч, вхід 16 управління режимом роботи реверсивного регістра зсуву зсув/ущільнення (1/0), вхід 17 управління зсувом праворуч, вхід 18 управління зсувом ліворуч, прямий 19 інформаційний вхід регістра зсуву при зсуві ліворуч, прямий 20 інформаційний вихід регістра зсуву при зсуві ліворуч. Пристрій працює наступним чином. В залежності від значення сигналу на вході 16 управління режимом роботи реверсивного регістра зсуву зсув/ущільнення (1/0) і значення сигналів зсув праворуч 17 (1/0), зсув ліворуч 18 (1/0) та значення сигналу синхронізації на вході 13 подача сигналу/відсутність сигналу (1/0), регістр працює в чотирьох режимах роботи: зсув послідовного двійкового коду праворуч, зсув послідовного двійкового коду ліворуч, ущільнення двійкового коду праворуч, ущільнення двійкового коду ліворуч. Заповнення n-розрядного регістра зсуву послідовним кодом виконується за час дії n сигналів зсуву на вході синхронізації 13 і присутності відповідних розрядів послідовного коду від розряду n до n-1,n-2,…,2,1 на послідовному вході 14 реверсивного регістра зсуву і значеннях сигналів 1 і 0 відповідно на входах зсув праворуч 17 і зсув ліворуч 18, і значенні сигналу 1 на вході 16 зсув/ущільнення. Наприклад, після запису в регістр зсуву при n=8 коду 01001010 цей код буде зберігатися в регістрі зсуву подалі при відсутності імпульсів синхронізації на вході 13. При нульовому значенні сигналу на вході управління режимом роботи 16 регістр працює в режимі ущільнення двійкового коду ліворуч при сигналах 1 на вході 17 і 0 на вході 18. Логічний зв'язок між прямим виходом тригера попереднього розряду і інформаційним Dвходом тригера розряду, що розглядається, при цьому відсутній. Позиційний двійковий код кількості одиниць і з виходу комбінаційного суматора 5 за допомогою дешифратора 6 перетворюється у сигнал одиниці на виході і, який далі подається на перший вхід другої 8 схеми АБО розряду і і далі через ланцюг других 8 схем АБО на другі входи других 8 схем АБО в розрядах і, і-1, і-2, і-3,…,2, 1. Після подачі одного імпульсу на вхід синхронізації 13 в регістр зсуву буде записано двійковий код 11100000 ущільнений ліворуч, який через вихід 20 може бути виведено з регістра зсуву зсувом ліворуч. При нульовому значенні сигналу на вході управління режимом роботи 16 регістр працює в режимі ущільнення двійкового коду праворуч при сигналах 0 на вході 17 і 1 на вході 18. Логічний 2 UA 83310 U 5 10 зв'язок між прямим виходом тригера наступного розряду і інформаційним D-входом тригера розряду, що розглядається, при цьому відсутній. Позиційний двійковий код кількості одиниць і з виходу комбінаційного суматора 5 за допомогою дешифратора 7 перетворюється у сигнал одиниці на виході і, який далі подається на перший вхід третьої 9 схеми АБО розряду і і далі через ланцюг третіх 9 схем АБО на другі входи третіх 9 схем АБО в розрядах і, і+1,1-+2, і+3, … n-, n. Наприклад, після запису в регістр зсуву при n=8 коду 01001010, переключення регістра потім в режим ущільнення праворуч і подачі одного сигналу на вхід синхронізації 13 одержимо в регістрі зсуву код 00000111, який через вихід 15 може бути виведено з регістра зсуву зсувом праворуч. Швидкодія регістра зсуву в режимі ущільнення коду не залежить від кількості розрядів коду і дорівнює одному такту. Запропонований регістр зсуву має малі апаратні витрати і може бути використаний в пристроях діагностування і статистичної обробки інформації. 15 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 20 25 30 35 40 45 50 55 Реверсивний регістр зсуву, який складається з групи n тригерів стану, першого елемента АБО, першого і другого елементів І в кожному розряді, комбінаційного двійкового суматора SM кількості одиниць неущільненого двійкового коду, першого DC1 і другого дешифраторів DC2 для перетворення позиційного двійкового коду кількості одиниць в унітарний код одиниць, другого елемента АБО в кожному розряді, крім останнього, третього елемента АБО в кожному розряді, крім першого, четвертого і п'ятого елементів АБО, виходи яких з'єднані з інверсним входом управління відповідно першого DC1 і другого DC2 дешифраторів, входів обнуління і синхронізації регістра зсуву, з'єднаних відповідно з входами обнуління і синхронізації усіх тригерів стану, прямого інформаційного входу реверсивного регістра зсуву, що з'єднаний з першим входом першого елемента І в першому розряді, перший вхід першого елемента І в кожному розряді, крім першого, з'єднаний з прямим виходом тригера попереднього розряду, прямий вихід тригера стану останнього розряду є виходом реверсивного регістра при зсуві праворуч, треті входи обох елементів І в кожному розряді з'єднані з шиною управління режимом роботи регістра зсуву (зсув/ущільнення коду) і з першими входами четвертого і п'ятого елементів АБО, другі входи перших елементів І в кожному розряді з'єднані з шиною зсув праворуч і з другим входом п'ятого елемента АБО, другі входи других елементів І в кожному розряді з'єднані з шиною зсув ліворуч і з другим входом четвертого елемента АБО, прямого інформаційного входу реверсивного регістра зсуву при зсуві ліворуч, що з'єднаний з першим входом другого елемента І в останньому розряді, перший вхід другого елемента І в кожному розряді, крім останнього, з'єднаний з прямим виходом тригера наступного розряду, прямий вихід тригера стану першого розряду є виходом реверсивного регістра зсуву при зсуві ліворуч, в якому прямі виходи тригерів усіх розрядів з'єднані з відповідними входами комбінаційного двійкового суматора SM кількості одиниць неущільненного двійкового коду, виходи якого з'єднані з відповідними входами дешифраторів DC1 і DC2, виходи других схем АБО в кожному розряді, крім останнього, з'єднані відповідно з третім входом першого елемента АБО у даному розряді, другий вхід другого елемента АБО в кожному розряді, крім останнього і передостаннього, з'єднано з виходом другого елемента АБО в наступному розряді, другий вхід другого елемента АБО в передостанньому розряді з'єднано з виходом n дешифратора DC1 і з третім входом першого елемента АБО в останньому розряді, виходи унітарного коду першого дешифратора DC1 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім останнього, виходи унітарного коду другого дешифратора DC2 з'єднані з відповідним першим входом третього елемента АБО в кожному розряді, крім першого, вихід кількості одиниць n другого дешифратора DC2 з'єднано з четвертим входом першого елемента АБО в першому розряді і з другим входом третього елемента АБО в другому розряді, другий вхід третього елемента АБО в кожному розряді, крім першого і другого, з'єднано з виходом третього елемента АБО в попередньому розряді, виходи першого і другого елементів І в кожному розряді з'єднані відповідно з першим і другим входами першого елемента АБО в цьому розряді, який відрізняється тим, що для тригерів стану використані CDR-тригери, причому вихід першого елемента АБО в усіх розрядах з'єднано з D-входами CDR-тригерів. 3 UA 83310 U Комп’ютерна верстка А. Крижанівський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюKachurin Mykola Yakovych, Varetsa Vitalii Viktorovych, Makarenko Hanna Mykolaivna

Автори російськоюКакурин Николай Яковлевич, Вареца Виталий Викторович, Макаренко Анна Николаевна

МПК / Мітки

МПК: G11C 19/00

Мітки: зсуву, регістр, реверсивний

Код посилання

<a href="https://ua.patents.su/6-83310-reversivnijj-registr-zsuvu.html" target="_blank" rel="follow" title="База патентів України">Реверсивний регістр зсуву</a>

Попередній патент: Пристрій автоматичного моніторингу стану контактних з’єднань високовольтних підстанцій і ліній електропередач

Наступний патент: Захисна споруда

Випадковий патент: Спосіб виготовлення навитих заготовок і верстат для його здійснення