Паралельно-послідовний аналого-цифровий перетворювач

Номер патенту: 89366

Опубліковано: 25.04.2014

Автори: Кичак Володимир Васильович, Стальченко Олександр Володимирович, Бортник Геннадій Григорович

Формула / Реферат

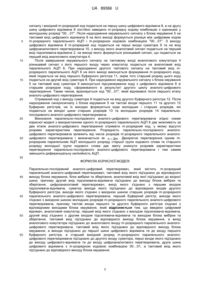

Паралельно-послідовний аналого-цифровий перетворювач, який містить m-розрядний паралельний аналого-цифровий перетворювач, тактовий вхід якого під'єднано до відповідного виходу блока керування, блок вибірки та зберігання, аналоговий вхід якої під'єднано до вхідної шини, причому другий вхід підсилювача-віднімача під'єднано до виходу блока вибірки та зберігання, цифроаналоговий перетворювач, вихід якого з'єднано з першим входом підсилювача-віднімача, суматор виходи якого під'єднано до відповідних входів другого буферного регістра, виходи якого з'єднані з вихідною шиною старших розрядів m-розрядного паралельного аналого-цифрового перетворювача, перший буферний регістр, виходи якого з'єднані з вихідною шиною молодших розрядів m-розрядного паралельного аналого-цифрового перетворювача, причому тактові входи першого та другого буферного регістра з'єднані з відповідними виходами блока керування, який відрізняється тим, що введено цифровий віднімач, аналоговий комутатор, перший вхід якого з'єднано з виходом підсилювача-віднімача, другий вхід з'єднано з другим входом підсилювача-віднімача та виходом блока вибірки та зберігання, тактовий вхід під'єднано до відповідного виходу блока керування, а вихід аналогового комутатора під'єднано до аналогового входу m-розрядного паралельного аналого-цифрового перетворювача, тактовий вхід якого під'єднано до відповідного виходу блока керування, а виходи під'єднано до першої шини цифрового віднімача та до входу першого буферного регістра, а старший вихідний розряд m-розрядного паралельного аналого-цифрового перетвюрювача під'єднано до другого входу суматора, перші входи якого під'єднано до виходу цифрового-віднімача та до входу цифроаналогового перетворювача, друга шина цифрового віднімача з m-розрядною кодовою комбінацією 00…01, а тактовий вхід якого під'єднано до відповідного виходу блока керування.

Текст

Реферат: Паралельно-послідовний аналого-цифровий перетворювач містить m-розрядний паралельний аналого-цифровий перетворювач, блок керування, блок вибірки та зберігання, вхідну шину, підсилювач-віднімач, цифроаналоговий перетворювач, перший та другий буферний регістр, вихідні шини старших та молодших розрядів m-розрядного паралельного аналого-цифрового перетворювача. Додатково введено цифровий віднімач, аналоговий комутатор та другу шину цифрового віднімача з m-розрядною кодовою комбінацією 00…01. UA 89366 U (54) ПАРАЛЕЛЬНО-ПОСЛІДОВНИЙ АНАЛОГО-ЦИФРОВИЙ ПЕРЕТВОРЮВАЧ UA 89366 U UA 89366 U Корисна модель належить до інформаційно-вимірювальної техніки і призначена для спектрометричних вимірювань високої точності та швидкодії в контрольно-вимірювальній техніці, радіолокації, експериментальній фізиці. Відомий паралельно-послідовний аналого-цифровий перетворювач (АЦП), який містить 5 10 15 20 2m 1 пристроїв порівняння, де m - кількість розрядів вихідного коду, яка визначається за один вимірювальний такт перетворювача, перші входи яких з'єднані з шиною джерела вхідного сигналу, другі входи - з відповідними виходами резистивного подільника, а виходи з'єднані з цифровими входами блока керування, перший вихід блока керування з'єднаний з першим входом першого перетворювача код-струм, вихід якого з'єднаний з першим виходом резистивного подільника, другий вихід блока керування з'єднаний з першим входом другого перетворювача код-струм, вихід якого з'єднаний з 2m 1 виходом резистивного подільника, а вхід резистивного подільника з'єднаний з шиною джерела початкового зміщення, третій вихід блока керування з'єднаний з входом блока пам'яті, перший вихід якого через цифро-аналоговий перетворювач (ЦАП) з'єднаний з другими входами першого і другого перетворювачів код-струм, другий вихід блока пам'яті з'єднаний з першими входами додаткових перетворювачів код-струм, вихід одного з яких з'єднаний з першим входом резистивного подільника, а вихід другого з 2m 1 виходом резистивного подільника [авторське свідоцтво СРСР № 651475, МКИ Н03К 13/17 бюлетень № 9, 1979 р.]. Недоліком цього АЦП є висока диференціальна нелінійність. Відомий паралельно-послідовний 8-розрядний аналого-цифровий перетворювач, який містить два 4-розрядних АЦП, кожен з яких містить послідовно з'єднані джерело опорних напруг m 25 30 35 40 45 50 55 і набір 2 2 1 компараторів, де m - кількість розрядів вихідного коду, різницевий пристрій, перші входи компараторів першого 4-розрядного АЦП з'єднані з шиною джерела напруги, що підлягає перетворенню, виходи компараторів першого 4-розрядного АЦП з'єднані з входами елементів пам'яті через групу елементів І та АБО, виходи елементів пам'яті під'єднані до шин старших розрядів і до входів ЦАП, вихід якого з'єднаний з другим входом різницевого пристрою, перший вхід якого під'єднаний до шини напруги, що підлягає перетворенню, вихід різницевого пристрою з'єднаний з першими входами компараторів другого 4-розрядного АЦП, другі входи яких і другі входи першого 4-розрядного АЦП під'єднані до шини джерела опорних напруг, виходи компараторів другого 4-розрядного АЦП через групу елементів І та АБО під'єднані до шин молодших розрядів [патент США № 41248224, кл. 330/252 МКИ - Н03К 13/17]. Недоліком даного перетворювача є висока диференціальна нелінійність, що обмежує точність перетворення. Найбільш близьким є паралельно-послідовний аналого-цифровий перетворювач, який містить m-розрядний паралельний аналого-цифровий перетворювач, тактовий вхід якого під'єднано до відповідного виходу блока керування, а аналоговий вхід під'єднано до виходу блока вибірки та зберігання, аналоговий вхід якої під'єднано до шини джерела аналогового сигналу, який підлягає перетворенню, а тактовий вхід до відповідного виходу блока керування, виходи m-розрядного паралельного аналого-цифрового перетворювача під'єднано до першої вхідної шини суматора та до відповідних входів цифроаналогового перетворювача, вихід якого з'єднано з першим входом підсилювача-віднімача, вихід якого під'єднано до аналогового входу l-розрядного паралельного аналого-цифрового перетворювача, де m l n - розрядність паралельно-послідовного аналого-цифрового перетворювача, причому другий вхід підсилювача-віднімача під'єднано до виходу блока вибірки та зберігання, а виходи l-розрядного паралельного аналого-цифрового перетворювача під'єднано до відповідних входів першого буферного регістра, причому старший розряд з'єднано з другою шиною суматора, виходи якого під'єднано до відповідних входів другого буферного регістра, виходи якого з'єднані з вихідною шиною старших розрядів пристрою, а виходи першого буферного регістра з'єднані з вихідною шиною молодших розрядів пристрою, причому тактові входи першого та другого буферного регістра з'єднані з відповідними виходами блока керування [Кестер У. Аналого-цифровое преобразование. - М: Техносфера, 2007, С. 242, рис. 3.70]. Недоліком даного пристрою є висока диференціальна нелінійність, особливо у точках характеристики перетворення, де узгоджуються шкали старших та молодших розрядів АЦП. Цей тип нелінійності є характерним для паралельно-послідовних аналого-цифрових перетворювачів, що ускладнює використання даних АЦП у галузі спектрометричних вимірювань. Причому для зниження диференціальної нелінійності висуваються жорсткі вимого щодо точності як АЦП старших розрядів, так і АЦП молодших розрядів. А це обмежує вихідну розрядність таких паралельно-послідовних аналого-цифрових перетворювачів на рівні 6 8 біт, 1 UA 89366 U 5 10 15 20 25 30 35 40 45 50 55 60 що є недостатнім при їх використанні в цифрових спектроаналізаторах та іншій контрольновимірювальній апаратурі, пов'язаній зі спектральним аналізом радіо- та широкосмугових відеосигналів. В основу корисної моделі поставлена задача створення паралельно-послідовного аналогоцифрового перетворювача, в якому за рахунок введення нових блоків та зв'язків зменшується диференціальна нелінійність, що сприяє підвищенню точності. Поставлена задача вирішується тим, що в паралельно-послідовний аналого-цифровий перетворювач, який містить m-розрядний паралельний аналого-цифровий перетворювач, тактовий вхід якого під'єднано до відповідного виходу блока керування, блока вибірки та зберігання, аналоговий вхід якої під'єднано до шини джерела аналогового сигналу, який підлягає перетворенню, причому другий вхід підсилювача-віднімача під'єднано до виходу блока вибірки та зберігання, цифроаналоговий перетворювач, вихід якого з'єднано з першим входом підсилювача-віднімача, суматор виходи якого під'єднано до відповідних входів другого буферного регістра, виходи якого з'єднані з вихідною шиною старших розрядів аналогоцифрового перетворювача, перший буферний регістр, виходи якого з'єднані з вихідною шиною молодших розрядів пристрою, причому тактові входи першого та другого буферного регістра з'єднані з відповідними виходами блока керування, введено цифровий віднімач, аналоговий комутатор, перший вхід якого з'єднано з виходом підсилювача-віднімача, другий вхід з'єднано з другим входом підсилювача-віднімача та виходом блока вибірки та зберігання, тактовий вхід під'єднано до відповідного виходу блока керування, а вихід аналогового комутатора під'єднано до аналогового входу m-розрядного паралельного аналого-цифрового перетворювача, тактовий вхід якого під'єднано до відповідного виходу блока керування, а виходи під'єднано до першої шини цифрового віднімача та до входу першого буферного регістра, а старший вихідний розряд m-розрядного паралельного АЦП під'єднано до другого входу суматора, перші входи якого під'єднано до виходу цифрового-віднімача та до входу цифроаналогового перетворювача, друга шина цифрового віднімача з m-розрядною кодовою комбінацією 00…01, а тактовий вхід якого під'єднано до відповідного виходу блока керування. На кресленні наведена структурна електрична схема паралельно-послідовного аналогоцифрового перетворювача. Пристрій містить вхідну шину 1 напруги Eв х , підсилювача-віднімача 2, блок вибірки та зберігання 3, аналоговий комутатор 4, блок керування 5, m-розрядний паралельний аналогоцифровий перетворювач 6, друга шина 7 цифрового віднімача з m-розрядною кодовою комбінацією 00…01, цифровий віднімач 8, суматор 9, цифроаналоговий перетворювач 10, перший буферний регістр 11 і другий буферний регістр 12, вихідна шина старших розрядів 13 та вихідна шина молодших розрядів 14, тактовий вхід m-розрядного паралельного аналогоцифрового перетворювача 6 під'єднано до відповідного виходу блока керування 5, аналоговий вхід блока вибірки та зберігання 3, під'єднано до вхідної шини 1, другий вхід підсилювачавіднімача 8 під'єднано до виходу блока вибірки та зберігання 3, вихід цифроаналогового перетворювача 10 з'єднано з першим входом підсилювача-віднімача 8, виходи суматора 9 під'єднано до відповідних входів другого буферного регістра 12, виходи якого з'єднані з вихідною шиною старших розрядів 13, виходи першого буферного регістра 11 з'єднані з вихідною шиною молодших розрядів 13, тактові входи першого 11 та другого 12 буферних регістрів з'єднані з відповідними виходами блока керування 5, перший вхід аналогового комутатора 4 з'єднано з виходом підсилювача-віднімача 2, другий вхід з'єднано з другим входом підсилювача-віднімача 2 та виходом блока вибірки та зберігання 3, тактовий вхід під'єднано до відповідного виходу блока керування 5, а вихід аналогового комутатора 4 під'єднано до аналогового входу m-розрядного паралельного аналого-цифрового перетворювача 6, тактовий вхід якого під'єднано до відповідного виходу блока керування 5, а виходи під'єднано до першої шини цифрового віднімача 8 та до входу першого буферного регістра 11, а старший вихідний розряд m-розрядного паралельного АЦП 6 під'єднано до другого входу суматора 9, перші входи якого під'єднано до виходу цифрового віднімача 8 та до входу цифроаналогового перетворювача 10, друга шину цифрового віднімача з m-розрядною кодовою комбінація 00…01, а тактовий вхід якого під'єднано до відповідного виходу блока керування. Аналого-цифровий перетворювач працює наступним чином. Вхідна напруга, яка перетворюється Uв х через вхідну шину 1 подається на вхід блока вибірки та зберігання 3. Після надходження керувального сигналу з блока керування 5 на тактовий вхід аналогового комутатора 4, вихідний сигнал з блока вибірки та зберігання з другого входу аналогового комутатора 4 спрямовується на його вихід і відповідно - на аналоговий вхід m-розрядного паралельного АЦП 6. Під дією синхросигналу з блока керування 5, що подається на тактовий вхід m-розрядного паралельного АЦП 6 виконується аналого-цифрове перетворення вхідного 2 UA 89366 U 5 10 15 20 25 30 сигналу і вихідний m-розрядний код подається на першу шину цифрового віднімача 8, а на другу шину цифрового віднімана 8 постійно заведено m-розрядну кодову комбінацію з одиницею у молодшому розряді "00…01". Після надходження керувального сигналу з блока керування 5 на тактовий вхід цифрового віднімача 8 на його виході формується різниця між цифровим кодом m-розрядного паралельного АЦП і m-розрядною кодовою комбінацією "00…01". З виходу цифрового віднімача 8 m-розрядний код подається на перші входи суматора 9 та на вхід цифроаналогового перетворювача 10, з виходу якого аналоговий сигнал подається на перший вхід підсилювача-віднімача 2, на виході якого формується різницевий сигнал, що подається на перший вхід аналогового комутатора 4. Після завершення керувального сигналу на тактовому вході аналогового комутатора 4 різницевий сигнал з його першого входу через комутатор подається на аналоговий вхід паралельного АЦП 6. При надходженні другого тактового сигналу на тактовий вхід mрозрядного паралельного АЦП 6 на його виході виконується формування m-розрядного коду, який подається на вхід першого буферного регістра 11, окрім того старший розряд цього коду подається на другий вхід суматора 9. При надходженні керувального сигналу з блока керування 5 на тактовий вхід суматора 9 виконується підсумовування коду з цифрового віднімача 8 зі старшим розрядом коду, сформованого в результаті другого циклу аналого-цифрового перетворення. Таким чином, враховується код "00…01", який віднімався після першого етапу аналого-цифрового перетворення. Отриманий код з виходу суматора 9 подається на вхід другого буферного регістра 12. Після надходження синхросигналу з блока керування 5 на тактові входи першого 11 та другого 12 буферних регістрів, на їх виходах формуються коди молодших і старших розрядів, які подаються на вихідні шини старших розрядів 13 та молодших розрядів 14 паралельнопослідовного аналого-цифрового перетворювача. Виконання паралельно-послідовного аналого-цифрового перетворювача згідно схеми корисної моделі з використанням одного m-розрядного паралельного АЦП 6 дає можливість за два етапи аналого-цифрового перетворення отримати m-розрядний код, у якому відсутні розриви характеристики перетворення. Розрядність паралельно-послідовного аналогоцифрового перетворювача залежить від числа розрядів m-розрядного паралельного аналогоцифрового перетворювача і визначається як n 2m . Двократне перетворення одним mрозрядним паралельним АЦП молодшого розряду старшої групи кодового слова та старшого розряду молодшої групи кодового слова дає змогу уникнути розривів характеристики перетворення паралельно-послідовного аналого-цифрового перетворювача і тим самим зменшити диференціальну нелінійність АЦП. 35 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 40 45 50 55 Паралельно-послідовний аналого-цифровий перетворювач, який містить m-розрядний паралельний аналого-цифровий перетворювач, тактовий вхід якого під'єднано до відповідного виходу блока керування, блок вибірки та зберігання, аналоговий вхід якої під'єднано до вхідної шини, причому другий вхід підсилювача-віднімача під'єднано до виходу блока вибірки та зберігання, цифроаналоговий перетворювач, вихід якого з'єднано з першим входом підсилювача-віднімача, суматор виходи якого під'єднано до відповідних входів другого буферного регістра, виходи якого з'єднані з вихідною шиною старших розрядів m-розрядного паралельного аналого-цифрового перетворювача, перший буферний регістр, виходи якого з'єднані з вихідною шиною молодших розрядів m-розрядного паралельного аналого-цифрового перетворювача, причому тактові входи першого та другого буферного регістра з'єднані з відповідними виходами блока керування, який відрізняється тим, що введено цифровий віднімач, аналоговий комутатор, перший вхід якого з'єднано з виходом підсилювача-віднімача, другий вхід з'єднано з другим входом підсилювача-віднімача та виходом блока вибірки та зберігання, тактовий вхід під'єднано до відповідного виходу блока керування, а вихід аналогового комутатора під'єднано до аналогового входу m-розрядного паралельного аналогоцифрового перетворювача, тактовий вхід якого під'єднано до відповідного виходу блока керування, а виходи під'єднано до першої шини цифрового віднімача та до входу першого буферного регістра, а старший вихідний розряд m-розрядного паралельного аналогоцифрового перетвюрювача під'єднано до другого входу суматора, перші входи якого під'єднано до виходу цифрового-віднімача та до входу цифроаналогового перетворювача, друга шина цифрового віднімача з m-розрядною кодовою комбінацією 00…01, а тактовий вхід якого під'єднано до відповідного виходу блока керування. 3 UA 89366 U Комп’ютерна верстка М. Ломалова Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюBortnyk Hennadii Hryhorovych, Stalchenko Oleksandr Volodymyrovych

Автори російськоюБортник Геннадий Григорьевич, Стальченко Александр Владимирович

МПК / Мітки

МПК: G06G 7/00

Мітки: перетворювач, паралельно-послідовний, аналого-цифровий

Код посилання

<a href="https://ua.patents.su/6-89366-paralelno-poslidovnijj-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Паралельно-послідовний аналого-цифровий перетворювач</a>

Попередній патент: Удосконалена оптико-електронна мішень стрілецького тренажера

Наступний патент: Паралельний аналого-цифровий перетворювач

Випадковий патент: Сировинна суміш для виготовлення теплоізоляційного матеріалу